【RK3568 看门狗驱动开发详解】

RK3568 看门狗驱动开发详解

- 一、Linux 看门狗子系统架构

- 二、设备树配置

- 三、 看门狗驱动实现

- 四、验证

看门狗定时器(Watchdog Timer)是保障嵌入式系统可靠性的关键硬件,它通过定期接收 “喂狗” 信号监控系统运行状态,当系统故障导致信号中断时,自动触发硬件复位实现系统自愈。本文以 RK3568 平台为例,全面讲解看门狗驱动的开发流程,包括子系统架构、驱动实现及功能验证。

一、Linux 看门狗子系统架构

Linux 内核通过看门狗子系统实现对硬件看门狗的标准化管理,架构采用分层设计:

┌─────────────────────────────────────────┐

│ 用户空间 │

│ ┌──────────┐ ┌──────────┐ ┌────────┐ │

│ │ watchdogd│ │ 应用程序 │ │ 工具类 │ │

│ └──────────┘ └──────────┘ └────────┘ │

└───────────────────┬─────────────────────┘│

┌───────────────────▼─────────────────────┐

│ 内核空间 │

│ ┌───────────────────────────────────┐ │

│ │ 核心层 │ │

│ │ (watchdog_core.c、watchdog_dev.c) │ │

│ └───────────────────┬───────────────┘ │

│ │ │

│ ┌───────────────────▼───────────────┐ │

│ │ 驱动层 │ │

│ │ (dw_wdt.c 具体实现) │ │

│ └───────────────────┬───────────────┘ │

└──────────────────────┼──────────────────┘│

┌──────────────────────▼──────────────────┐

│ 硬件层 │

│ RK3568 看门狗定时器硬件 │

└─────────────────────────────────────────┘

核心组件解析

- 核心层:

- 提供统一的struct watchdog_device结构体抽象硬件

- 定义标准操作集struct watchdog_ops

- 管理/dev/watchdog字符设备节点

- 实现用户空间接口(ioctl、write 等)

- 驱动层:

- 实现硬件特定的操作(启动、停止、喂狗等)

- 处理硬件中断和复位逻辑

- 对接核心层接口完成设备注册

- 关键数据结构:

// 看门狗设备结构体

struct watchdog_device {const struct watchdog_ops *ops; // 硬件操作函数集struct device *dev; // 关联设备int id; // 设备IDunsigned int timeout; // 超时时间(秒)unsigned int min_timeout; // 最小超时时间unsigned int max_timeout; // 最大超时时间unsigned int flags; // 设备标志(如WDIOF_KEEPALIVEPING)// 其他成员...

};// 看门狗操作函数集

struct watchdog_ops {int (*start)(struct watchdog_device *wdd); // 启动看门狗int (*stop)(struct watchdog_device *wdd); // 停止看门狗int (*ping)(struct watchdog_device *wdd); // 喂狗int (*set_timeout)(struct watchdog_device *wdd, unsigned int t); // 设置超时// 其他可选操作...

};

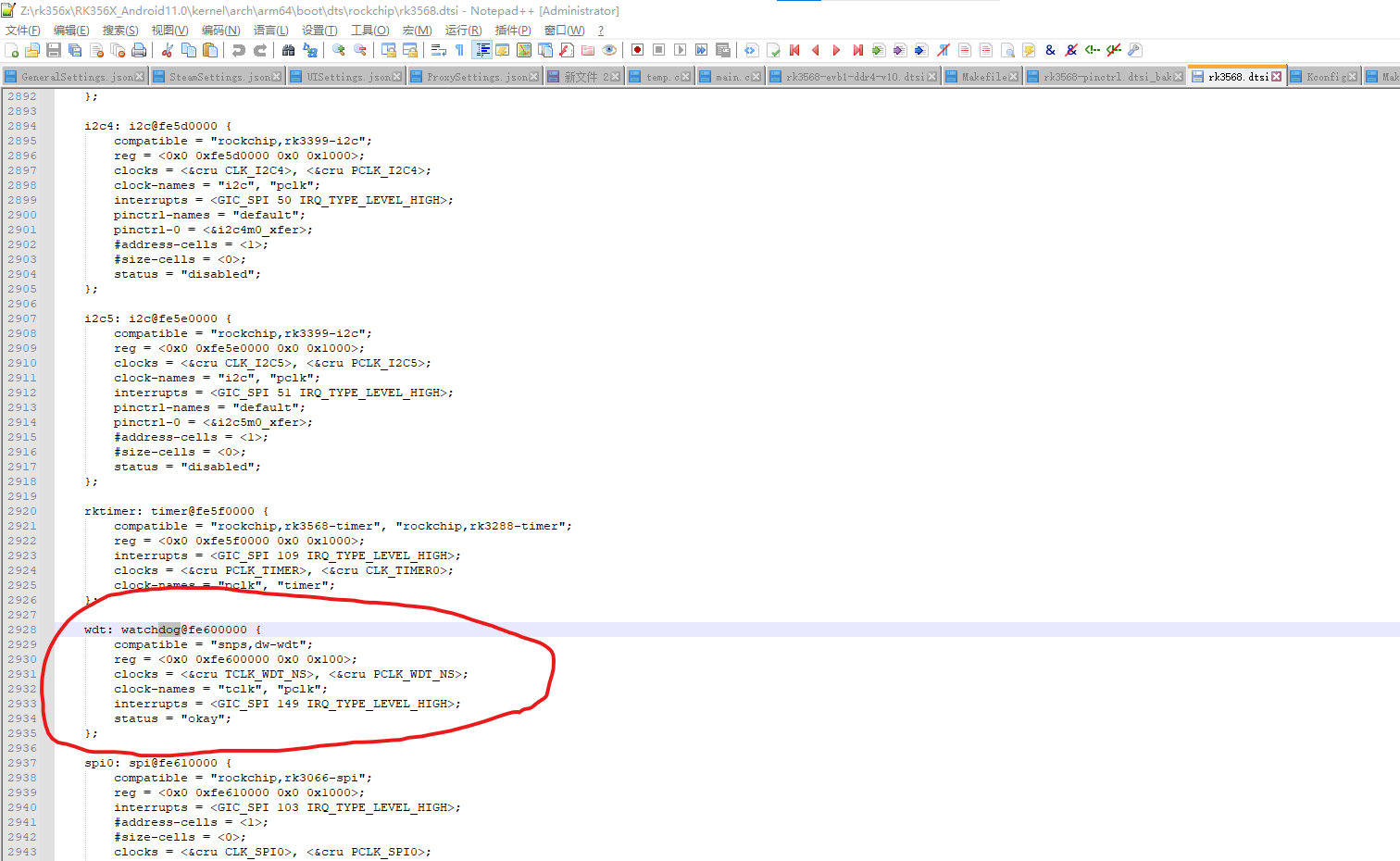

二、设备树配置

RK3568 看门狗设备树节点配置如下:

kernel/arch/arm64/boot/dts/rockchip/rk3568.dtsi

三、 看门狗驱动实现

kernel/drivers/watchdog/dw_wdt.c

/** Copyright 2010-2011 Picochip Ltd., Jamie Iles* http://www.picochip.com** This program is free software; you can redistribute it and/or* modify it under the terms of the GNU General Public License* as published by the Free Software Foundation; either version* 2 of the License, or (at your option) any later version.** This file implements a driver for the Synopsys DesignWare watchdog device* in the many subsystems. The watchdog has 16 different timeout periods* and these are a function of the input clock frequency.** The DesignWare watchdog cannot be stopped once it has been started so we* do not implement a stop function. The watchdog core will continue to send* heartbeat requests after the watchdog device has been closed.*/#define pr_fmt(fmt) KBUILD_MODNAME ": " fmt#include <linux/bitops.h>

#include <linux/clk.h>

#include <linux/delay.h>

#include <linux/err.h>

#include <linux/io.h>

#include <linux/kernel.h>

#include <linux/module.h>

#include <linux/moduleparam.h>

#include <linux/of.h>

#include <linux/pm.h>

#include <linux/platform_device.h>

#include <linux/reset.h>

#include <linux/watchdog.h>#define WDOG_CONTROL_REG_OFFSET 0x00

#define WDOG_CONTROL_REG_WDT_EN_MASK 0x01

#define WDOG_CONTROL_REG_RESP_MODE_MASK 0x02

#define WDOG_TIMEOUT_RANGE_REG_OFFSET 0x04

#define WDOG_TIMEOUT_RANGE_TOPINIT_SHIFT 4

#define WDOG_CURRENT_COUNT_REG_OFFSET 0x08

#define WDOG_COUNTER_RESTART_REG_OFFSET 0x0c

#define WDOG_COUNTER_RESTART_KICK_VALUE 0x76/* The maximum TOP (timeout period) value that can be set in the watchdog. */

#define DW_WDT_MAX_TOP 15#define DW_WDT_DEFAULT_SECONDS 30static bool nowayout = WATCHDOG_NOWAYOUT;

module_param(nowayout, bool, 0);

MODULE_PARM_DESC(nowayout, "Watchdog cannot be stopped once started ""(default=" __MODULE_STRING(WATCHDOG_NOWAYOUT) ")");struct dw_wdt {void __iomem *regs;struct clk *clk;struct clk *pclk;unsigned long rate;struct watchdog_device wdd;struct reset_control *rst;/* Save/restore */u32 control;u32 timeout;

};#define to_dw_wdt(wdd) container_of(wdd, struct dw_wdt, wdd)static inline int dw_wdt_is_enabled(struct dw_wdt *dw_wdt)

{return readl(dw_wdt->regs + WDOG_CONTROL_REG_OFFSET) &WDOG_CONTROL_REG_WDT_EN_MASK;

}static inline int dw_wdt_top_in_seconds(struct dw_wdt *dw_wdt, unsigned top)

{/** There are 16 possible timeout values in 0..15 where the number of* cycles is 2 ^ (16 + i) and the watchdog counts down.*/return (1U << (16 + top)) / dw_wdt->rate;

}static int dw_wdt_get_top(struct dw_wdt *dw_wdt)

{int top = readl(dw_wdt->regs + WDOG_TIMEOUT_RANGE_REG_OFFSET) & 0xF;return dw_wdt_top_in_seconds(dw_wdt, top);

}static int dw_wdt_ping(struct watchdog_device *wdd)

{struct dw_wdt *dw_wdt = to_dw_wdt(wdd);writel(WDOG_COUNTER_RESTART_KICK_VALUE, dw_wdt->regs +WDOG_COUNTER_RESTART_REG_OFFSET);return 0;

}static int dw_wdt_set_timeout(struct watchdog_device *wdd, unsigned int top_s)

{struct dw_wdt *dw_wdt = to_dw_wdt(wdd);int i, top_val = DW_WDT_MAX_TOP;/** Iterate over the timeout values until we find the closest match. We* always look for >=.*/for (i = 0; i <= DW_WDT_MAX_TOP; ++i)if (dw_wdt_top_in_seconds(dw_wdt, i) >= top_s) {top_val = i;break;}/** Set the new value in the watchdog. Some versions of dw_wdt* have have TOPINIT in the TIMEOUT_RANGE register (as per* CP_WDT_DUAL_TOP in WDT_COMP_PARAMS_1). On those we* effectively get a pat of the watchdog right here.*/writel(top_val | top_val << WDOG_TIMEOUT_RANGE_TOPINIT_SHIFT,dw_wdt->regs + WDOG_TIMEOUT_RANGE_REG_OFFSET);wdd->timeout = dw_wdt_top_in_seconds(dw_wdt, top_val);return 0;

}static void dw_wdt_arm_system_reset(struct dw_wdt *dw_wdt)

{u32 val = readl(dw_wdt->regs + WDOG_CONTROL_REG_OFFSET);/* Disable interrupt mode; always perform system reset. */val &= ~WDOG_CONTROL_REG_RESP_MODE_MASK;/* Enable watchdog. */val |= WDOG_CONTROL_REG_WDT_EN_MASK;writel(val, dw_wdt->regs + WDOG_CONTROL_REG_OFFSET);

}static int dw_wdt_start(struct watchdog_device *wdd)

{struct dw_wdt *dw_wdt = to_dw_wdt(wdd);dw_wdt_set_timeout(wdd, wdd->timeout);dw_wdt_ping(&dw_wdt->wdd);dw_wdt_arm_system_reset(dw_wdt);return 0;

}static int dw_wdt_stop(struct watchdog_device *wdd)

{struct dw_wdt *dw_wdt = to_dw_wdt(wdd);if (!dw_wdt->rst) {set_bit(WDOG_HW_RUNNING, &wdd->status);return 0;}reset_control_assert(dw_wdt->rst);reset_control_deassert(dw_wdt->rst);return 0;

}static int dw_wdt_restart(struct watchdog_device *wdd,unsigned long action, void *data)

{struct dw_wdt *dw_wdt = to_dw_wdt(wdd);writel(0, dw_wdt->regs + WDOG_TIMEOUT_RANGE_REG_OFFSET);if (dw_wdt_is_enabled(dw_wdt))writel(WDOG_COUNTER_RESTART_KICK_VALUE,dw_wdt->regs + WDOG_COUNTER_RESTART_REG_OFFSET);elsedw_wdt_arm_system_reset(dw_wdt);/* wait for reset to assert... */mdelay(500);return 0;

}static unsigned int dw_wdt_get_timeleft(struct watchdog_device *wdd)

{struct dw_wdt *dw_wdt = to_dw_wdt(wdd);return readl(dw_wdt->regs + WDOG_CURRENT_COUNT_REG_OFFSET) /dw_wdt->rate;

}static const struct watchdog_info dw_wdt_ident = {.options = WDIOF_KEEPALIVEPING | WDIOF_SETTIMEOUT |WDIOF_MAGICCLOSE,.identity = "Synopsys DesignWare Watchdog",

};static const struct watchdog_ops dw_wdt_ops = {.owner = THIS_MODULE,.start = dw_wdt_start,.stop = dw_wdt_stop,.ping = dw_wdt_ping,.set_timeout = dw_wdt_set_timeout,.get_timeleft = dw_wdt_get_timeleft,.restart = dw_wdt_restart,

};#ifdef CONFIG_PM_SLEEP

static int dw_wdt_suspend(struct device *dev)

{struct dw_wdt *dw_wdt = dev_get_drvdata(dev);dw_wdt->control = readl(dw_wdt->regs + WDOG_CONTROL_REG_OFFSET);dw_wdt->timeout = readl(dw_wdt->regs + WDOG_TIMEOUT_RANGE_REG_OFFSET);clk_disable_unprepare(dw_wdt->pclk);clk_disable_unprepare(dw_wdt->clk);return 0;

}static int dw_wdt_resume(struct device *dev)

{struct dw_wdt *dw_wdt = dev_get_drvdata(dev);int err = clk_prepare_enable(dw_wdt->clk);if (err)return err;err = clk_prepare_enable(dw_wdt->pclk);if (err) {clk_disable_unprepare(dw_wdt->clk);return err;}writel(dw_wdt->timeout, dw_wdt->regs + WDOG_TIMEOUT_RANGE_REG_OFFSET);writel(dw_wdt->control, dw_wdt->regs + WDOG_CONTROL_REG_OFFSET);dw_wdt_ping(&dw_wdt->wdd);return 0;

}

#endif /* CONFIG_PM_SLEEP */static SIMPLE_DEV_PM_OPS(dw_wdt_pm_ops, dw_wdt_suspend, dw_wdt_resume);static int dw_wdt_drv_probe(struct platform_device *pdev)

{struct device *dev = &pdev->dev;struct watchdog_device *wdd;struct dw_wdt *dw_wdt;struct resource *mem;int ret;dw_wdt = devm_kzalloc(dev, sizeof(*dw_wdt), GFP_KERNEL);if (!dw_wdt)return -ENOMEM;mem = platform_get_resource(pdev, IORESOURCE_MEM, 0);dw_wdt->regs = devm_ioremap_resource(dev, mem);if (IS_ERR(dw_wdt->regs))return PTR_ERR(dw_wdt->regs);/** Try to request the watchdog dedicated timer clock source. It must* be supplied if asynchronous mode is enabled. Otherwise fallback* to the common timer/bus clocks configuration, in which the very* first found clock supply both timer and APB signals.*/dw_wdt->clk = devm_clk_get(dev, "tclk");if (IS_ERR(dw_wdt->clk)) {dw_wdt->clk = devm_clk_get(dev, NULL);if (IS_ERR(dw_wdt->clk))return PTR_ERR(dw_wdt->clk);}ret = clk_prepare_enable(dw_wdt->clk);if (ret)return ret;dw_wdt->rate = clk_get_rate(dw_wdt->clk);if (dw_wdt->rate == 0) {ret = -EINVAL;goto out_disable_clk;}/** Request APB clock if device is configured with async clocks mode.* In this case both tclk and pclk clocks are supposed to be specified.* Alas we can't know for sure whether async mode was really activated,* so the pclk phandle reference is left optional. If it couldn't be* found we consider the device configured in synchronous clocks mode.*/dw_wdt->pclk = devm_clk_get_optional(dev, "pclk");if (IS_ERR(dw_wdt->pclk)) {ret = PTR_ERR(dw_wdt->pclk);goto out_disable_clk;}ret = clk_prepare_enable(dw_wdt->pclk);if (ret)goto out_disable_clk;dw_wdt->rst = devm_reset_control_get_optional_shared(&pdev->dev, NULL);if (IS_ERR(dw_wdt->rst)) {ret = PTR_ERR(dw_wdt->rst);goto out_disable_pclk;}reset_control_deassert(dw_wdt->rst);wdd = &dw_wdt->wdd;wdd->info = &dw_wdt_ident;wdd->ops = &dw_wdt_ops;wdd->min_timeout = 1;wdd->max_hw_heartbeat_ms =dw_wdt_top_in_seconds(dw_wdt, DW_WDT_MAX_TOP) * 1000;wdd->parent = dev;watchdog_set_drvdata(wdd, dw_wdt);watchdog_set_nowayout(wdd, nowayout);watchdog_init_timeout(wdd, 0, dev);/** If the watchdog is already running, use its already configured* timeout. Otherwise use the default or the value provided through* devicetree.*/if (dw_wdt_is_enabled(dw_wdt)) {wdd->timeout = dw_wdt_get_top(dw_wdt);set_bit(WDOG_HW_RUNNING, &wdd->status);} else {wdd->timeout = DW_WDT_DEFAULT_SECONDS;watchdog_init_timeout(wdd, 0, dev);}platform_set_drvdata(pdev, dw_wdt);watchdog_set_restart_priority(wdd, 128);ret = watchdog_register_device(wdd);if (ret)goto out_disable_pclk;return 0;out_disable_pclk:clk_disable_unprepare(dw_wdt->pclk);out_disable_clk:clk_disable_unprepare(dw_wdt->clk);return ret;

}static int dw_wdt_drv_remove(struct platform_device *pdev)

{struct dw_wdt *dw_wdt = platform_get_drvdata(pdev);watchdog_unregister_device(&dw_wdt->wdd);reset_control_assert(dw_wdt->rst);clk_disable_unprepare(dw_wdt->pclk);clk_disable_unprepare(dw_wdt->clk);return 0;

}#ifdef CONFIG_OF

static const struct of_device_id dw_wdt_of_match[] = {{ .compatible = "snps,dw-wdt", },{ /* sentinel */ }

};

MODULE_DEVICE_TABLE(of, dw_wdt_of_match);

#endifstatic struct platform_driver dw_wdt_driver = {.probe = dw_wdt_drv_probe,.remove = dw_wdt_drv_remove,.driver = {.name = "dw_wdt",.of_match_table = of_match_ptr(dw_wdt_of_match),.pm = &dw_wdt_pm_ops,},

};module_platform_driver(dw_wdt_driver);MODULE_AUTHOR("Jamie Iles");

MODULE_DESCRIPTION("Synopsys DesignWare Watchdog Driver");

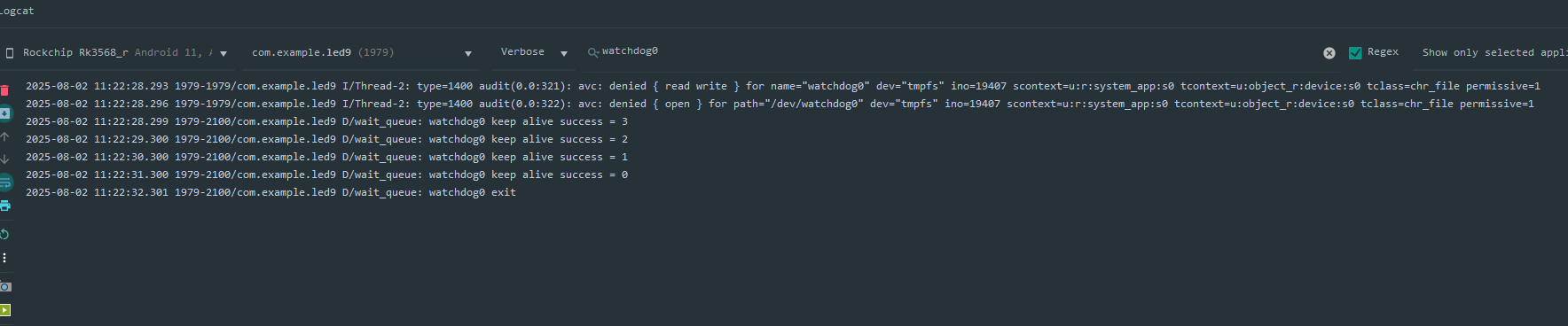

MODULE_LICENSE("GPL");四、验证

#define WATCHDOG_IOCTL_BASE 'W'#define WDIOC_KEEPALIVE _IOR(WATCHDOG_IOCTL_BASE, 5, int)

#define WDIOC_SETTIMEOUT _IOWR(WATCHDOG_IOCTL_BASE, 6, int)

extern "C"

JNIEXPORT jint JNICALL

Java_com_example_led9_MainActivity_watchdog(JNIEnv *env, jobject thiz) {int fd;// 打开设备fd = open("/dev/watchdog0", O_RDWR);if (fd == -1) {LOGD("watchdog0 无法打开设备");return -1;}int timeout = 2;if (ioctl(fd, WDIOC_SETTIMEOUT, &timeout) < 0){LOGD("watchdog0 set timeout error.");return -1;}int i = 4;while (i--){if (ioctl(fd, WDIOC_KEEPALIVE, NULL) < 0){LOGD("watchdog0 keep alive error.");return -1;}LOGD("watchdog0 keep alive success = %d", i);sleep(1);}LOGD("watchdog0 exit");close(fd);return 0;}

通过测试程序能发现,在超时时间内没有喂狗的话,系统会自动重启。