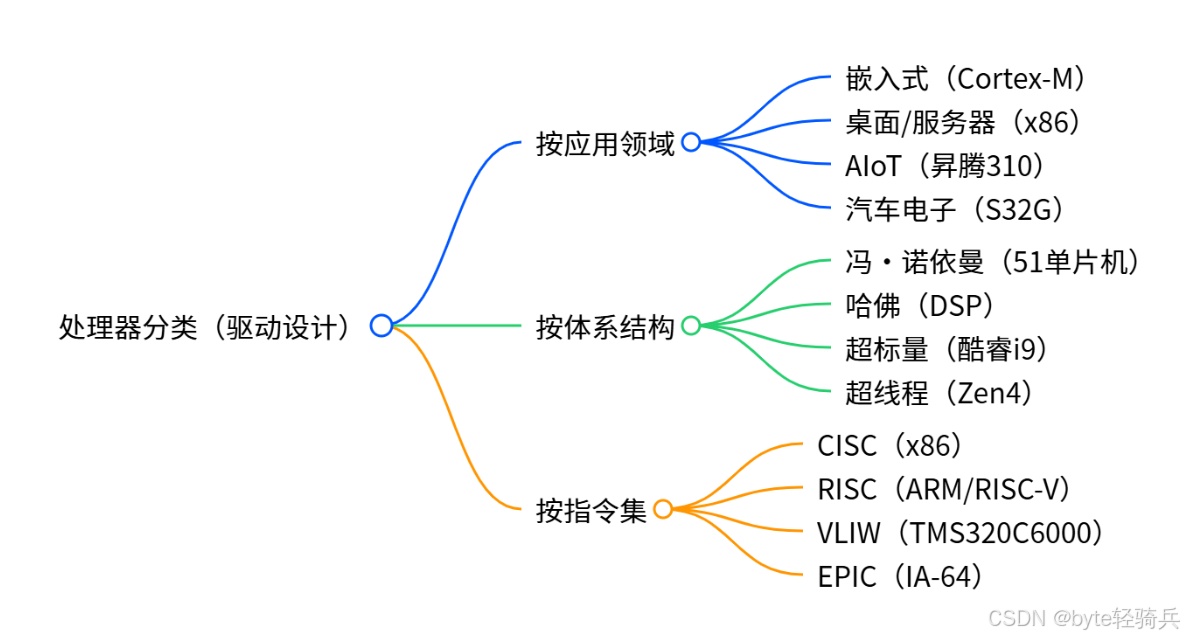

【驱动设计的硬件基础】处理器的分类

目录

一、按应用领域分类:处理器的 “职业选择”

1.1 嵌入式领域:小身材大能量

1.2 桌面 / 服务器领域:性能为王

1.3 AIoT(人工智能物联网)领域:边缘计算新宠

1.4 汽车电子领域:安全至上

二、按体系结构分类:处理器的 “设计哲学”

2.1 冯・诺依曼结构:“共享仓库” 的经典设计

2.2 哈佛结构:“专用通道” 的高效方案

2.3 超标量结构:“多条流水线” 的并行高手

2.4 超线程结构:“虚拟多核” 的性能 trick

三、按指令集分类:处理器的 “语言体系”

3.1 CISC(复杂指令集):“大而全” 的 “全能语言”

3.2 RISC(精简指令集):“小而精” 的 “高效语言”

3.3 VLIW(超长指令字):“并行执行” 的 “批发语言”

3.4 EPIC(显式并行指令计算):“智能批发” 的进化版

3.5 指令集对比表

四、实战:不同分类下的驱动开发差异

4.1 硬件环境

4.2 驱动开发对比

4.3 结果对比

五、未来:处理器分类的 “新趋势”

5.1 异构计算:“混合标签” 成主流

5.2 RISC-V 的 “标签革命”

六、结语

今天咱们就给处理器 “贴标签”,从应用领域、体系结构、指令集三个维度,彻底搞懂驱动开发绕不开的处理器分类。这些内容不是 “纸上谈兵”—— 当你在驱动里写request_irq(申请中断)、用dma_map_single(映射 DMA 内存)时,每一行代码都在和处理器的 “标签” 对话。

一、按应用领域分类:处理器的 “职业选择”

处理器就像打工人,不同领域需要不同 “技能”。驱动开发者要根据设备的需求(比如是要低功耗还是高性能),给处理器选对 “职业”。

1.1 嵌入式领域:小身材大能量

嵌入式设备(如智能手表、扫地机器人、工业 PLC)通常 “资源有限”(小内存、低功耗、严格成本控制),所以嵌入式处理器要 “小而精”。

①典型代表:ARM Cortex-M 系列

Cortex-M 是 ARM 专为嵌入式设计的低功耗处理器(如 Cortex-M4、M7),全球超过 90% 的微控制器(MCU)都用它。

驱动开发特点:

- 无 MMU(内存管理单元):驱动直接访问物理地址,需要手动管理内存(比如用

static变量避免堆分配);- 低功耗优先:驱动要控制外设进入睡眠模式(比如关闭未使用的 GPIO 时钟),甚至让 CPU 进入 “深度睡眠”(

WFI指令);- 实时性要求高:中断响应时间必须在微秒级(比如电机控制驱动,延迟超过 10μs 就会导致抖动)。

②真实案例:智能手环的心率驱动

某智能手环用 Cortex-M4 开发心率传感器驱动:

- 传感器每 20ms 上传一次数据,驱动通过 I2C 读取原始信号(红外和红光);

- 为了省电,无数据时 CPU 进入睡眠模式(仅保留 I2C 控制器时钟);

- 数据处理放在 “任务队列”(底半部),避免中断处理时间过长(ISR 只做标记)。

1.2 桌面 / 服务器领域:性能为王

桌面电脑(如 MacBook)和服务器(如阿里云主机)需要处理复杂任务(3D 渲染、数据库运算、AI 训练),所以处理器要 “性能怪兽”。

①典型代表:x86(Intel/AMD)、ARM 服务器芯片

x86 处理器(如 Intel 酷睿 i9、AMD 锐龙 9)凭借强大的浮点运算和多线程支持,长期垄断桌面 / 服务器市场;ARM 近年也推出了服务器芯片(如亚马逊 Graviton3),凭借低功耗抢占云市场。

驱动开发特点:

- 多核优化:驱动需要支持多线程(比如网络驱动的多队列处理,每个核心负责一个队列);

- 大内存支持:驱动要处理 GB 级别的数据(比如视频编辑软件的内存分配,用

vmalloc分配大块连续内存);- 兼容性优先:驱动需要适配不同操作系统版本(如 Windows 11 的 WDM 驱动、Linux 的内核模块)。

②真实案例:服务器的网卡驱动

某云服务器用 Intel 10GbE 网卡驱动:

- 驱动为每个 CPU 核心分配一个接收队列(RSS 技术),避免数据争用;

- 支持大页内存(2MB/1GB 页),减少 TLB(页表缓存)缺失,提升数据吞吐量;

- 兼容多种操作系统(通过条件编译

#ifdef LINUX/#ifdef WINDOWS)。

1.3 AIoT(人工智能物联网)领域:边缘计算新宠

AIoT 设备(如智能摄像头、语音助手、智能音箱)需要 “本地 AI 计算”(人脸识别、语音识别、场景检测),所以处理器要 “AI 友好”。

①典型代表:华为昇腾 310、高通 Sensing Hub

昇腾 310 是专为边缘 AI 设计的处理器,内置 NPU(神经网络处理器);高通 Sensing Hub 则集成了 DSP 和低功耗传感器,擅长语音唤醒、运动检测等轻量级 AI 任务。

驱动开发特点:

- NPU/DSP 协作:驱动需要把 AI 模型数据传给 NPU(比如用

dma_map_single映射模型文件到 NPU 内存),并处理计算结果;- 低延迟推理:优化数据传输路径(比如用共享内存代替拷贝),确保人脸识别延迟低于 100ms;

- 能效比关键:驱动动态调整 NPU 的工作模式(空闲时进入低功耗状态,检测到目标时唤醒)。

②真实案例:智能摄像头的人脸识别驱动

某智能摄像头用昇腾 310 开发人脸识别驱动:

- 摄像头数据通过 DMA 直接传到 NPU 内存(避免 CPU 参与);

- 驱动调用 NPU 的 API(如

aclModelExecute)加载人脸识别模型; - 识别结果通过共享内存传给上层应用(APP 显示 “主人已到家”);

- 无目标时,NPU 进入睡眠模式(功耗从 2W 降到 0.5W)。

1.4 汽车电子领域:安全至上

汽车电子(如自动驾驶、车载信息娱乐系统、电子刹车)对 “可靠性” 要求极高(人命关天),所以处理器要 “安全第一”。

①典型代表:恩智浦 S32G、德州仪器 TDA4

S32G 是汽车专用处理器,符合 ISO 26262 功能安全标准(ASIL-D 级,最高安全等级);TDA4 则集成了 GPU、DSP 和 NPU,擅长自动驾驶的环境感知。

驱动开发特点:

- 功能安全认证:驱动需要实现故障检测(比如寄存器看门狗)、冗余设计(关键信号双路传输);

- 实时性要求:中断响应时间必须在毫秒级(比如刹车信号处理延迟超过 50ms 就可能撞车);

- 宽温宽压:驱动适应 - 40℃到 125℃的环境(比如调整 ADC 的参考电压,避免温度漂移导致采样错误)。

②真实案例:自动驾驶的激光雷达驱动

某自动驾驶平台用 TDA4 开发激光雷达驱动:

- 激光雷达每秒发送 150 万点云数据,驱动通过 PCIe 接口高速接收;

- 驱动实现 “错误校正”(比如检测点云数据的 CRC 校验码,丢包时请求重传);

- 高温环境下(85℃),驱动动态降低 CPU 频率(从 2GHz 降到 1.5GHz),避免过热宕机。

二、按体系结构分类:处理器的 “设计哲学”

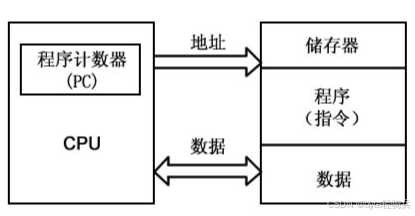

体系结构是处理器的 “底层设计哲学”,决定了它如何组织内部资源(如寄存器、总线、缓存)。驱动开发者需要理解这些设计,才能写出 “贴合硬件” 的代码。

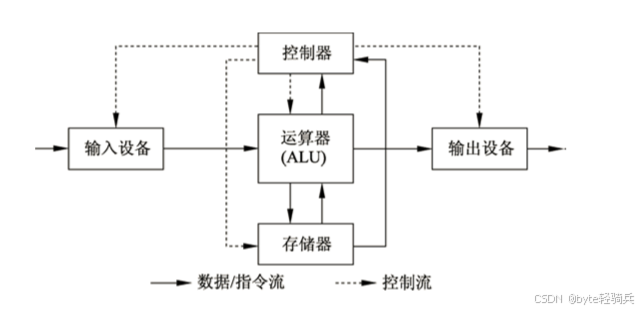

2.1 冯・诺依曼结构:“共享仓库” 的经典设计

冯・诺依曼结构是最传统的设计,指令和数据共用同一块内存(就像 “仓库里既放货物又放清单”),只有一根总线用于传输指令和数据。

①典型代表:51 单片机、早期 ARM7

51 单片机(如 STC89C52)是最经典的冯・诺依曼处理器,广泛用于玩具、小家电等简单设备。

驱动开发特点:

- 成本低:电路简单,适合资源有限的小设备;

- 速度慢:取指令和读数据分时占用总线,容易 “堵车”(比如读取传感器数据时,CPU 必须等待总线空闲);

- 驱动简单:内存访问逻辑统一(不需要区分指令内存和数据内存)。

2.2 哈佛结构:“专用通道” 的高效方案

哈佛结构把指令和数据分开存储(“货物仓库” 和 “清单仓库” 独立),有专用的指令总线和数据总线,适合高频数据处理。

典型代表:DSP(如 TI TMS320)、ARM Cortex-M(部分型号)

TI 的 TMS320C6000 系列 DSP 是哈佛结构的典型,广泛用于音视频编码、通信基站。

驱动开发特点:

- 速度快:指令和数据同时传输,吞吐量提升(比如音频解码时,CPU 可以同时取指令和读音频数据);

- 驱动复杂:需要分别处理指令内存(如 Flash)和数据内存(如 RAM)的访问(比如用

CODE_SECTION宏指定代码存储区域);- 适合实时性场景:高频信号处理时,不会因 “总线堵车” 导致延迟(比如无人机飞控的姿态解算)。

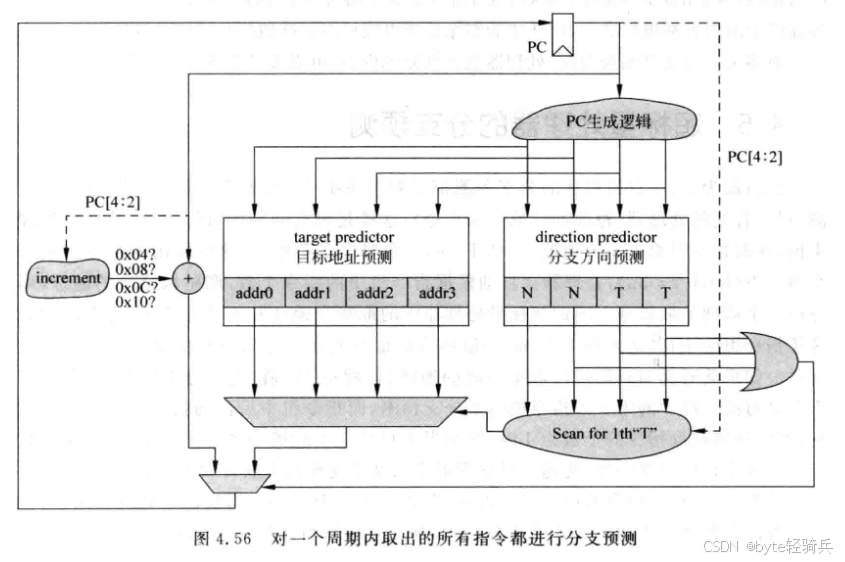

2.3 超标量结构:“多条流水线” 的并行高手

超标量结构有多个独立的流水线(“包子铺有 3 条流水线,同时蒸肉包、菜包、豆沙包”),可以同时执行多条指令,提升并行性能。

典型代表:x86(Intel 酷睿)、ARM Cortex-A(高端型号)

Intel 酷睿 i9 有 16 条流水线(8 条整数流水线 + 8 条浮点流水线),能同时执行 16 条指令。

驱动开发特点:

- 指令级并行:驱动的循环代码(如数据遍历)可以被高效执行(比如

for (i=0; i<1000; i++) sum += arr[i]会被分解到多条流水线);- 编译优化:需要配合编译器(如 GCC 的

-O3选项)生成并行度高的代码(比如自动展开循环);- 缓存优化:合理利用 L1/L2/L3 缓存(比如把常用变量放在 L1 缓存,减少访问时间)。

2.4 超线程结构:“虚拟多核” 的性能 trick

超线程(HT)技术让单个物理核心模拟两个逻辑核心(“一个人同时干两个人的活”),适合多任务场景(如一边打游戏一边直播)。

典型代表:Intel 酷睿 i 系列、AMD Zen 系列

Intel i5-13600K 有 6 个物理核心 + 12 个逻辑核心,AMD Ryzen 9 7950X 有 16 个物理核心 + 32 个逻辑核心。

驱动开发特点:

- 多线程支持:驱动可以创建更多线程(比如网络驱动的接收线程和发送线程,分别绑定不同逻辑核心);

- 资源竞争:两个逻辑核心共享物理核心的执行单元(如 ALU、缓存),驱动需要避免同时使用相同资源(比如用互斥锁保护共享变量);

- 任务分配:根据任务类型分配逻辑核心(比如把计算密集型任务放在不同物理核心,避免资源争用)。

三、按指令集分类:处理器的 “语言体系”

指令集是处理器能 “听懂” 的 “语言”,驱动代码最终会被编译成这些指令。不同指令集的 “语法” 差异极大,直接影响驱动的写法。

3.1 CISC(复杂指令集):“大而全” 的 “全能语言”

CISC(Complex Instruction Set Computer)的指令集 “大而全”,一条指令能完成复杂操作(如 “把数组 A 拷贝到数组 B”)。

典型代表:x86 指令集(Intel/AMD)

x86 指令集有 2000 多条指令(如MOVS“内存拷贝”、MUL“乘法”),向下兼容 30 年(老程序在新 CPU 上依然能跑)。

驱动开发特点:

- 代码密度高:复杂操作只需少量指令,适合内存有限的场景(比如早期 DOS 系统的驱动);

- 硬件复杂:处理器需要更多电路支持复杂指令,功耗较高(x86 桌面 CPU 功耗常超过 100W);

- 兼容性强:驱动可以在不同代际的 x86 处理器上运行(比如 Windows 驱动兼容 i3 到 i9)。

3.2 RISC(精简指令集):“小而精” 的 “高效语言”

RISC(Reduced Instruction Set Computer)的指令集 “小而精”,只保留最常用的简单指令(如 “取数”“加法”),复杂操作通过组合简单指令实现。

典型代表:ARM、RISC-V、MIPS

ARM 指令集只有 40 多条基本指令(如LDR“加载数据”、ADD“加法”),RISC-V 更精简(32 条基础指令),适合低功耗设备。

驱动开发特点:

- 硬件简单:处理器电路少,适合低功耗场景(如手机、物联网设备,ARM 芯片功耗常低于 1W);

- 流水线友好:简单指令更容易并行执行(适合超标量结构,比如 ARM Cortex-A78 的 8 级流水线);

- 编译优化依赖高:复杂操作需要编译器 “聪明” 地组合简单指令(如 GCC 的

-march选项指定处理器架构)。

3.3 VLIW(超长指令字):“并行执行” 的 “批发语言”

VLIW(Very Long Instruction Word)把多条简单指令打包成一个 “超长指令”,处理器同时执行这些指令(“一次批发多条任务”)。

典型代表:TI TMS320C6000 系列 DSP

TMS320C66x 的指令字长 128 位,能打包 8 条 16 位指令,适合高频信号处理(如 5G 基站的信道编码)。

驱动开发特点:

- 并行度极高:适合高频信号处理(如音频 / 视频编码,吞吐量是普通 DSP 的 3 倍);

- 编译难度大:需要专用编译器(如 TI 的 Code Composer Studio)生成超长指令;

- 灵活性差:指令打包后难以动态调整,适合任务固定的场景(如专用音视频芯片)。

3.4 EPIC(显式并行指令计算):“智能批发” 的进化版

EPIC(Explicitly Parallel Instruction Computing)是 VLIW 的 “智能版”,编译器在打包指令时会显式标记并行性(告诉处理器哪些指令可以同时执行)。

典型代表:Intel IA-64(安腾)、AMD X86-64(部分支持)

安腾处理器的指令字长 128 位,包含 3 条 41 位的指令和 1 位的 “停止位”(标记并行结束)。

驱动开发特点:

- 并行更高效:编译器自动识别可并行的指令,减少 “无效打包”(比如避免打包依赖前一条指令结果的指令);

- 生态弱势:安腾因生态问题已退出市场,目前主要用于高端服务器(如惠普超级计算机);

- 驱动适配难:需要专用编译器(如 Intel 的 IA-64 编译器),开发成本高。

3.5 指令集对比表

| 类型 | 代表指令集 | 特点 | 驱动适用场景 |

|---|---|---|---|

| CISC | x86 | 指令复杂、代码密度高、硬件复杂 | 桌面 / 服务器、需要兼容老程序 |

| RISC | ARM、RISC-V | 指令简单、硬件低功耗、流水线友好 | 手机、物联网、嵌入式设备 |

| VLIW | TMS320C6000 | 超长指令、并行度高、编译依赖强 | 专用信号处理(如 5G 信道编码) |

| EPIC | IA-64 | 显式并行、智能打包、生态弱势 | 高端服务器、超级计算机 |

四、实战:不同分类下的驱动开发差异

说了这么多理论,咱们用一个实际案例串起来:开发一个智能空调的温度传感器驱动,看看它在不同处理器分类下的适配差异。

4.1 硬件环境

- 方案 A:嵌入式领域,ARM Cortex-M3(冯・诺依曼结构,RISC 指令集);

- 方案 B:AIoT 领域,高通 Sensing Hub(哈佛结构,VLIW 指令集)。

4.2 驱动开发对比

①方案 A:Cortex-M3 驱动(嵌入式 + 冯・诺依曼 + RISC)

- 初始化:通过 I2C 接口配置温度传感器(设置采样率、分辨率),用

i2c_master_transfer函数写寄存器; - 数据采集:传感器每 500ms 上传一次数据,触发 Cortex-M3 的中断;

- 数据处理:ISR 读取原始数据(16 位 ADC 值),通过任务队列调用校准算法(如

temp = (adc_value * 3.3 / 4096 - 0.5) * 100); - 低功耗优化:无数据时,驱动控制 CPU 进入睡眠模式(

__WFI()指令),关闭 I2C 时钟,功耗从 10mA 降到 1mA。

②方案 B:高通 Sensing Hub 驱动(AIoT + 哈佛 + VLIW)

- 初始化:通过 SPI 接口配置传感器(SPI 比 I2C 更快,适合高频数据),用

spi_transfer函数传输数据; - 数据采集:传感器数据通过 DMA 直接传到 DSP 内存(地址

0x80000000),触发 DSP 的中断; - 数据处理:ISR 标记数据到达,DSP 用 VLIW 的 “浮点运算指令”(如

FMA“乘加”)快速计算温度值(支持同时处理 8 个采样点); - AI 增强:驱动调用 Sensing Hub 的 AI 引擎(如 “温度预测模型”),根据历史数据预测未来 10 分钟的温度,调整压缩机功率。

4.3 结果对比

- 方案 A:适合基础款空调(成本低,驱动代码简单),温度精度 ±0.5℃,功耗低;

- 方案 B:适合智能空调(支持温度预测、节能模式),温度精度 ±0.1℃,但驱动开发成本高(需要学习 VLIW 指令和 AI 引擎接口)。

五、未来:处理器分类的 “新趋势”

5.1 异构计算:“混合标签” 成主流

未来的设备会集成多种处理器(如通用 CPU+GPU+NPU+DSP),形成 “异构计算平台”。驱动需要适配不同 “标签” 的处理器(比如 CPU 管调度,GPU 管渲染,NPU 管 AI),这对驱动的 “跨平台适配能力” 提出了更高要求。

5.2 RISC-V 的 “标签革命”

RISC-V 作为开源指令集,允许用户自定义指令(如添加 AI 专用指令)。未来的处理器可能同时属于 “嵌入式 + 哈佛 + RISC-V 自定义指令集”,驱动开发者需要掌握 “定制指令集” 的适配方法(比如用内联汇编调用自定义指令)。

六、结语

从嵌入式的 “小而美” 到服务器的 “大而强”,从冯・诺依曼的 “经典” 到 RISC-V 的 “开源”,处理器的每一个 “标签” 都在诉说它的 “能力边界”。对于驱动开发者来说,理解这些标签(应用领域、体系结构、指令集),就像拿到了一把 “钥匙”—— 只有用对钥匙,才能打开硬件的 “能力之门”,写出高效、稳定的驱动代码。

处理器的分类体系: