微机原理与接口技术,期末习题(一)

接续上文:微机原理与接口技术,期末冲刺复习资料(六)-CSDN博客

点关注不迷路哟。你的点赞、收藏,一键三连,是我持续更新的动力哟!!!

持续关注我~~~主页,查看更多内容哟(希望你能在这里有所收获🤭)。点关注,不迷路,哈哈哈!~~~

主页:

一位搞嵌入式的 genius-CSDN博客![]() https://blog.csdn.net/m0_73589512?spm=1000.2115.3001.5343

https://blog.csdn.net/m0_73589512?spm=1000.2115.3001.5343

目录

9. 芯片、接口总结

🔎 补充术语说明

🔧 8255 可编程并行接口 —— 控制字格式说明

🧭 控制字格式(写入控制寄存器)

📘 控制模式简表

📌 示例控制字配置

🔧 8253 可编程定时器/计数器 —— 控制字格式说明

🧭 控制字格式(写入控制寄存器)

📘 控制字字段说明

📌 6种工作模式概览

📌 示例控制字配置

10. 习题讲解

10.1 微型计算机基础

10.2 半导体存储器

一、中断方式(Interrupt-Driven I/O)

核心逻辑

特点

二、DMA 方式(Direct Memory Access)

核心逻辑

特点

三、程序控制 I/O(扩展补充,含查询方式)

包含子类

四、通道方式(大型系统专属,了解即可)

核心逻辑

特点

总结(微机接口场景常用)

9. 芯片、接口总结

| 类别 | 芯片型号 | 类型/容量 | 主要引脚及功能 | 典型接口方式 | 详实说明 |

|---|---|---|---|---|---|

| CPU | 8086 | 16位微处理器 | AD0–AD15(地址/数据复用)、A16–A19、RD、WR、ALE、IO/M、INTR、NMI、HLDA、HOLD | 与系统总线直接连接,A16–A19+AD0–AD15 构成20位地址总线 | Intel第一代16位微处理器,最大可寻址1MB内存,分为最小/最大两种模式,支持段式内存管理和并行流水线结构。用于早期PC架构和教学系统。 |

| 8088 | 8位微处理器 | AD0–AD7、A8–A15、其余控制线与8086类似 | 适用于8位系统,数据线与外设共享 | 与8086功能基本兼容,仅数据总线降为8位,适合低成本系统,在IBM PC中广泛使用。 | |

| 并行接口 | 8255 | 可编程并行I/O接口 | PA0–PA7、PB0–PB7、PC0–PC7(含上下半控制位)、CS、RD、WR、A0、D0–D7 | 三个端口(A/B/C)用于连接LED、按键、步进电机、数码管等,地址A0选择端口 | 可编程三种工作方式:方式0为基本输入输出(无握手);方式1具握手信号(中断驱动);方式2支持A口双向传输。用于控制类实验和硬件接口控制。 |

| 定时器 | 8253 | 3 × 16位计数器 | CLKx、GATEx、OUTx(x=0~2);CS、RD、WR、A0–A1、D0–D7 | 3个通道通过A0–A1选择访问,OUT输出连接蜂鸣器/中断控制器等 | 可产生定周期中断、方波、精确定时,支持6种工作模式,如定长延时、中断触发等。常用于键盘扫描、蜂鸣器控制、时间控制等系统中。 |

| 中断控制器 | 8259A | 8通道中断控制器 | IR0–IR7、INT、CS、RD、WR、A0、CAS0–2、SP/EN、D0–D7 | INT连接CPU INTR,IRx连接外设中断源 | 主片控制8个中断源,可与多个从片级联扩展至64个。支持优先级管理、中断屏蔽、自动结束或手动结束等中断服务机制,适用于复杂多外设系统。 |

| SRAM | 6264 | 8K × 8bit | A0–A12、D0–D7、CS1/CS2(片选)、OE、WE | 地址线连接A0–A12,数据线接D0–D7,OE/WE控制读写 | 静态随机存储器,不需要刷新,读写速度快,适用于缓存、堆栈等临时数据存储场合,但掉电即失数据。 |

| DRAM | 2164A | 64K × 1bit | 地址线复用、RAS、CAS、WE、数据线Din/Dout | 地址需分行列传送,需专用控制电路支持刷新 | 动态随机存储器,需周期性刷新,单位容量成本低,适用于大容量主存结构,教学场合常用作存储层深入理解对象。 |

| EPROM | 2764 | 8K × 8bit | A0–A12、D0–D7、OE(读使能)、CE(片选)、PGM(编程) | 接系统地址/数据总线,需高压(通常12.5V)编程 | 紫外线擦除型只读存储器,掉电不失数据,适用于固化程序(如BIOS等)。写入需专用烧录器,通过紫外灯擦除重写。 |

| EEPROM | 98C64 | 8K × 8bit | A0–A12、D0–D7、CE、OE、WE、READY/BUSY | 类似SRAM方式访问,写入需写命令并检测READY/BUSY引脚 | 电擦除可编程只读存储器,掉电数据保持,可反复写入,适合嵌入式程序存储与设置参数保存等用途。 |

| Flash | 常见如 W29C | 64K~512K | A0–An、D0–D7、CE、OE、WE、RESET | 与EEPROM类似,需先擦后写 | Flash 为 EEPROM 的升级版,常用于程序代码存储(如Bootloader、固件),写入前需块擦除。适用于STM32、嵌入式系统中。 |

| A/D转换器 | ADC0809 | 8位逐次逼近 A/D | IN0–IN7(模拟输入)、ADDA–C(通道选址)、ALE、START、EOC、OE、CLK、D0–D7 | 模拟输入接传感器,数字输出连接数据总线 | 支持多路输入,逐次逼近型转换,转换时间约100μs,适用于温度、电压、光强采集等模拟信号数字化处理。 |

| 译码器 | 74LS138 | 3线选8线输出 | A0–A2(地址选择)、G1、G2A、G2B(使能)、Y0–Y7(输出) | A0–A2接地址线,用于RAM/ROM/外设片选 | 常用于I/O地址或存储器地址分段译码,为外设或存储器选择信号提供控制。三输入八输出,低电平有效输出。 |

🔎 补充术语说明

-

CS / CE(Chip Select):片选信号,激活芯片

-

OE(Output Enable)/RD(读):使能输出(通常为低电平有效)

-

WE(Write Enable)/WR(写):使能写入(通常为低电平有效)

-

ALE:地址锁存使能(用于区分地址与数据)

-

EOC:End of Conversion,指示A/D转换完成

-

INTR / INT:中断请求线(输入/输出)

-

GATE / OUT / CLK(8253):启动门控、输出、计数时钟输入

-

PGM(EPROM):编程控制信号,高压编程时使用

-

READY/BUSY(EEPROM):写操作是否完成的指示

🔧 8255 可编程并行接口 —— 控制字格式说明

🧭 控制字格式(写入控制寄存器)

lua复制编辑D7 D6 D5 D4 D3 D2 D1 D0| | | | | | | || | | | | | | +---- PC0(C口低位)模式| | | | | | +--------- B口模式(0:输入,1:输出)| | | | | +-------------- C口高4位模式(0:输出,1:输入)| | | | +------------------- A口模式位0(方式)| | | +------------------------ A口模式位1(方式)| | +----------------------------- A口方向(0:输入,1:输出)| +---------------------------------- 控制 C口(1:控制字有效)+-------------------------------------- 固定为1,表示写入控制字模式

📘 控制模式简表

| 位 | 含义 |

|---|---|

| D7 | 始终为1,表示控制字写入模式 |

| D6–D5 | A口的工作方式(方式0/1/2) |

| D4 | A口方向(1=输出,0=输入) |

| D3 | C上(PC4-PC7)方向(1=输入,0=输出) |

| D2 | B口方向(1=输出,0=输入) |

| D1 | C下(PC0-PC3)方向(1=输入,0=输出) |

| D0 | 不使用(通常写为0) |

📌 示例控制字配置

| 功能设置 | 控制字(十六进制) | 说明 |

|---|---|---|

| A/B/C全部输出,方式0 | 0x80 | D7=1,方式0,全部为输出 |

| A口方式1输入,B口方式0输出 | 0x9A | A口=输入/方式1,B=输出,C上=输入,C下=输出 |

| A口方式2输出(双向),B口方式0输入 | 0xB6 | A口=方式2,B=输入,C上下分别为控制信号 |

🔧 8253 可编程定时器/计数器 —— 控制字格式说明

🧭 控制字格式(写入控制寄存器)

D7 D6 D5 D4 D3 D2 D1 D0| | | | | | | || | | | | | | +---- 位0:BCD(二进制/BCD模式)| | | | | | +--------- 位1–2:计数器读/写方式| | | | | +-------------- 位3–5:计数器工作模式(0–5)| | | +------------------------ 位6–7:选择通道(计数器0~2)

📘 控制字字段说明

| 位段 | 作用 |

|---|---|

| D7–D6 | 通道选择:00=计数器0,01=计数器1,10=计数器2,11=非法 |

| D5–D4 | 读写方式:00=无效,01=低字节,10=高字节,11=先低后高 |

| D3–D1 | 工作方式:05(模式05),6/7等价于2/3 |

| D0 | 计数方式:0=二进制,1=BCD计数 |

📌 6种工作模式概览

| 模式 | 名称 | 功能描述 |

|---|---|---|

| 0 | 中断等待 | 初始为低,计数完后OUT为高(一次) |

| 1 | 可重触发单脉冲 | 输入GATE高时触发一次低脉冲 |

| 2 | 方波生成器 | OUT周期为 N 个 CLK,脉冲宽度固定 |

| 3 | 方波发生器(对称) | 常用来驱动蜂鸣器,输出为对称矩形波 |

| 4 | 软件触发脉冲 | 写控制字后启动,计数完 OUT 变高 |

| 5 | 硬件触发脉冲 | GATE为高时开始计数,计数完 OUT 变高 |

📌 示例控制字配置

| 功能设置 | 控制字(二进制) | 控制字(十六进制) | 说明 |

|---|---|---|---|

| 通道0,模式3,16位递减计数,二进制 | 00110110 | 0x36 | 通常用于方波/蜂鸣器 |

| 通道1,模式2,低+高字节,BCD计数 | 01111111 | 0x7F | 高精度延时 |

| 通道2,模式0,仅写低字节 | 10110001 | 0xB1 | 延时中断触发,OUT一次拉高 |

10. 习题讲解

10.1 微型计算机基础

-

微型计算机系统主要由:微处理器、存储器、总线、I/O接口、输入输出设备、软件系统构成。

-

I/O接口是:主机和外设之间的接口

-

CPU包含了计算机的:运算器、控制器和内部寄存器

-

带奇偶校验的ASCLL码是:将最高位作为校验位

核心考察 ASCII 码的奇偶校验机制,具体涉及:

-

ASCII 码的基本结构:原始 7 位表示字符,扩展后用 8 位(含校验位 )。

-

奇偶校验原理:通过额外设置 1 个校验位(本题是最高位 ),保证数据传输 / 存储中 “1” 的个数符合奇偶规则,用于简单检错 。

-

校验位的位置约定:明确在 ASCII 码奇偶校验场景下,校验位固定占用最高位,而非其他位 。

-

-

正数的补码就是原码;负数的补码就是需要按位取反加1

-

判断符号数加减运算溢出,依据是最高位(符号位)和次高位的进(借)位状态。若二者不同,说明结果溢出;相同则未溢出 。

-

二进制转换成BCD码的规则就是:将二进制转换成10进制,然后再讲每个十进制数转换成为4位二进制数。

-

指令流水线指的就是:微处理器同时执行多条指令

-

单元类型 具体组成部件 / 功能 EU(执行单元) 算术逻辑单元(ALU):执行算术、逻辑运算 通用寄存器组(AX、BX、CX、DX 等):暂存操作数、中间结果 标志寄存器(FLAGS):记录运算结果状态(如进位、溢出等 ) EU 控制电路:协调指令执行,向 BIU 申请总线操作 BIU(总线接口单元) 段寄存器(CS、DS、ES、SS ):提供段基址 指令指针(IP):存放下一条指令偏移地址(代码段专用 ) 地址加法器:计算 20 位物理地址(段基址 + 偏移地址 ) 指令队列:预取指令暂存,实现 EU、BIU 并行工作 总线控制逻辑:管理内存、I/O 总线访问(读写控制 ) 作用简述:

-

EU 专注指令执行(运算、寄存器操作 );

-

BIU 负责总线交互(取指令、读写数据,生成物理地址 ),二者并行提升效率 。

-

-

控制标志位:ITOF这三个

-

总线的基本功能就是:传输同步、仲裁控制、总线驱动

-

8086 微处理器的总线周期与 READY 信号功能,核心是理解

READY引脚对总线周期的调控作用:-

READY是内存 / 外设向 CPU 反馈 “是否准备好数据” 的信号; -

若

READY=0,表示内存 / 外设未就绪,CPU 需插入等待周期(Tw ) ,延长总线周期等待数据,直到READY=1再继续传输。

-

-

冯诺依曼基本原理:存储程序

10.2 半导体存储器

-

高速缓存(Cache)是为解决 CPU 与主存速度差异,提高 CPU 访问内存的速度 。

-

访问存储器时,地址先输出有效,选通存储单元后,数据才有效 。

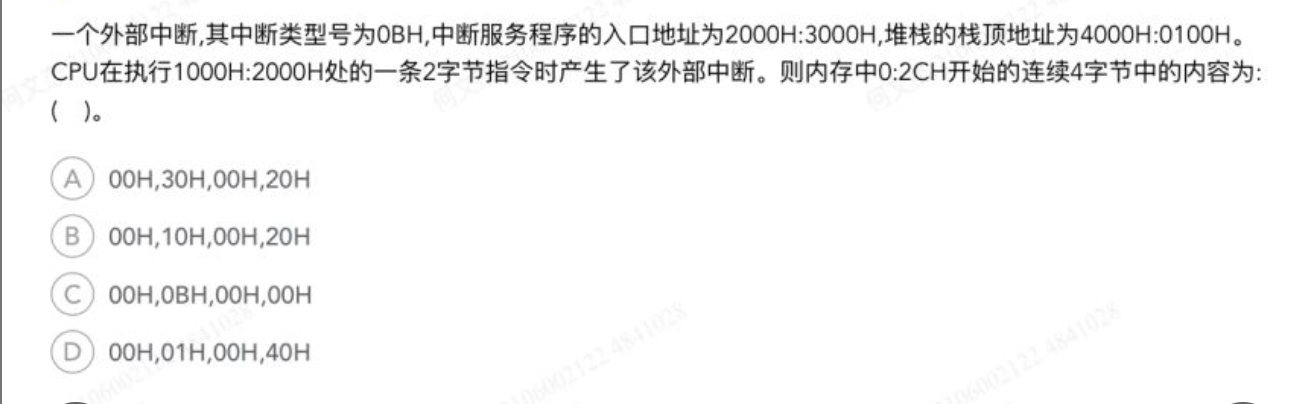

解: 中断发生时,需保存断点(CS、IP )和标志寄存器。原指令地址 (1000H:2000H),下条指令地址 (1000H + (2000H + 2) = 1000H:2002H)(因指令 2 字节 ),断点 CS=1000H、IP=2002H;中断向量表中,类型号 0BH 对应地址存服务程序入口 (2000H:3000H),栈顶地址 (4000H:0100H),入栈顺序是标志寄存器、CS、IP ,但本题看内存 (0:2CH)(中断向量表,类型号 0BH 对应地址 (0:0BH×4 = 0:2CH) ),存服务程序入口的偏移地址和段地址,即 3000H(偏移 )、2000H(段 ),对应字节 (00H,30H,00H,20H) 。

-

三态门可用于读取开关状态(高 / 低电平 ),作为输入接口;计数器用于计数,译码器用于地址译码,锁存器用于暂存数据输出,均不适合单纯读开关状态 。

-

一、中断方式(Interrupt-Driven I/O)

核心逻辑

外设准备好数据后,通过硬件信号(如 8259A 中断控制器 )主动向 CPU 发中断请求;CPU 响应后,暂停当前程序,转去执行中断服务程序(完成数据读写 ),执行完再返回原程序。

特点

优点 缺点 1. CPU 效率高:无需持续查询外设状态,可并行处理其他任务; 2. 实时性强:外设请求能及时响应,适合异步、突发数据(如键盘按键、串口接收 ); 3. 支持多外设:通过中断优先级管理,可同时响应多个设备。 1. 硬件复杂:需中断控制器(如 8259A )、中断请求线,增加电路设计难度; 2. 软件开销:中断服务程序有现场保护、恢复操作,频繁中断会影响主程序效率; 3. 存在中断延迟:需等待 CPU 完成当前指令、响应中断。 二、DMA 方式(Direct Memory Access)

核心逻辑

由DMA 控制器(DMAC,如 8237 ) 接管系统总线,直接控制内存与外设间的数据传输,全程无需 CPU 参与指令执行,仅在传输开始 / 结束时通知 CPU 。

特点

优点 缺点 1. 传输速率极快:省略 CPU 干预,直接通过总线传输,适合高速、大数据量场景(如硬盘读写、显存刷新 ); 2. CPU 完全解放:传输期间 CPU 可执行其他任务(但总线被占用,无法访问内存 ); 3. 支持块传输:可一次性传输连续内存块,效率远高于字节级交互。 1. 硬件成本高:需独立 DMA 控制器,增加系统复杂度; 2. 总线竞争:DMA 传输时 CPU 失去总线控制权,若设计不当会影响实时性; 3. 配置复杂:需初始化 DMAC(设置传输地址、长度、方向等 ),软件调试难度大。 三、程序控制 I/O(扩展补充,含查询方式)

包含子类

-

无条件传送:假设外设始终就绪,直接读写(如简单 LED 输出 ),本质是查询方式的极端简化(跳过查询 )。

-

查询方式(题目提及 ):CPU 主动轮询外设状态寄存器,就绪后才传输,优缺点与前文中断、DMA 对比明显。

四、通道方式(大型系统专属,了解即可)

核心逻辑

在大型计算机中,设置I/O 通道(专用处理器 ),CPU 只需下达通道指令(如 “从硬盘读数据到内存” ),通道自主管理外设、调度 DMA 传输,完成后再反馈 CPU 。

特点

-

高度并行:CPU、通道、外设可同时工作,适合多外设、高吞吐量场景(如服务器 );

-

成本极高:需独立通道处理器、复杂总线仲裁,仅在大型系统中使用,微机接口课程中极少深入。

总结(微机接口场景常用)

方式 核心优势 典型应用场景 查询方式 实现简单(无额外硬件) 低速、对实时性无要求外设(如开关检测 ) 中断方式 平衡 CPU 效率与实时性 键盘、串口、定时器中断等 DMA 方式 极致传输速度 硬盘、显卡、高速数据采集 -

-

软件中断核心是指令触发

-

8253 中,方式 2(速率波 形 )和方式 4(软件触发选通 )可软件启动(写计数初值 )或硬件启动(门控信号触发 );方式 0、1、3、5 启动条件单一,选 C (注:核心记方式 2、4 支持双启动 )。

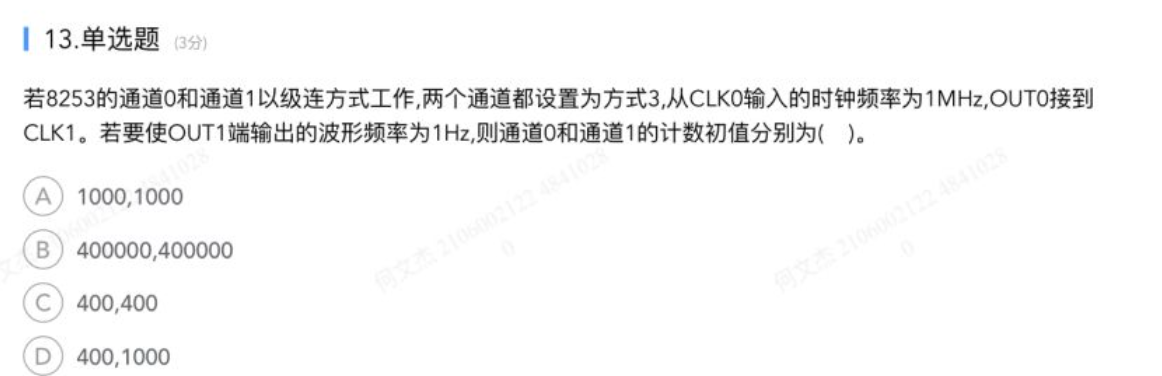

级联分频是 “乘法关系”,目标分频倍数 = 通道 0 计数初值 × 通道 1 计数初值

因为:计数初值(各计数初值的乘积) = 输入频率/输出频率

-

8086 中断向量表从

00000H开始,共 256 个中断向量,每个向量占 4 字节(高 2 字节是段地址,低 2 字节是偏移地址 ) -

INTR(可屏蔽中断 )需要读取中断类型码; -

NMI(不可屏蔽中断 )类型码固定为02H,无需读取。