PCIe—TS1/TS2 之Polling.Active(一)

前文

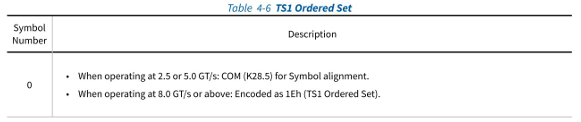

训练序列有序集用于比特对齐、符号对齐以及交换物理层参数。2.5GT/s和5GT/s速率时,训练序列有序集不会加扰,只用8b/10b 编码。但到8GT/s及以上速率时,采用128b/130b编码,符号有可能加扰有可能不加扰,具体参阅SPEC物理层章节,后续可能会写。

训练序列(TS1或TS2或ModifiedTS1或ModifiedTS2)是连续传输的,并且只能被SKP有序集(Section4.2.7)或对于2.5GT/s 以外的数据速率由EIEOS有序集中断(Section4.2.4.3)。

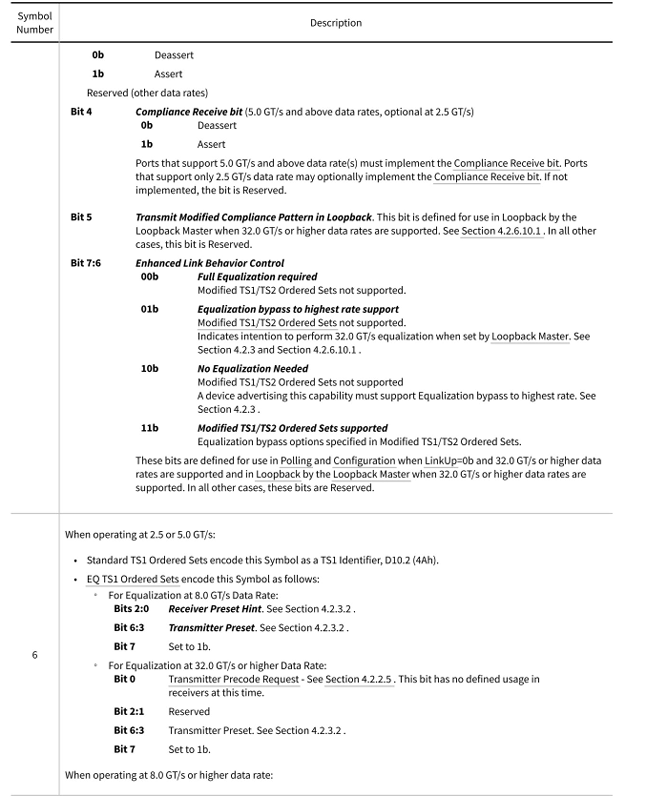

当支持8.0GT/s或更高的数据速率时,使用8b/10b编码的TS1(或TS2)有序集(即2.5或5.0GT/s数据速率)可以是标准TS1 (或TS2)有序集(即,对于TS1有序集,Symbol6是D10.2,对于TS2有序集,是D5.2)或EQTS1有序集(或EQTS2有序集) (即,Symbol6的bit7是1b)。传输EQTS1有序集的能力是特定于实现的。支持8.0GT/s或更高数据速率的端口必须接受LTSSM 状态中的TS1(或TS2)类型,除非明确要求查找特定类型。不支持8.0GT/s数据速率的端口允许(但不是必需)接受EQTS1(或 TS2)有序集。

当支持16.0GT/s和更高数据速率时,使用128b/130b编码(即8.0GT/s或更高数据速率)的TS2可以是标准TS2有序集(即Symbol 7 为45h)或128b/130bEQTS2(即,Symbol7的bit7为1b)。除非明确要求查找特定类型,否则支持16.0GT/s或更高数据速 率的端口必须在LTSSM状态中接受任一TS2类型。允许(但不是必需)不支持16.0GT/s数据速率的端口接受128b/130bEQTS2 有序集。 使用8b/10b 编码时,仅当Symbol6与先前的TS1或TS2有序集的Symbol6相匹配时,才将TS1或TS2有序集视为连续(传输过 程中不能Symbol6的值不能随意改动)

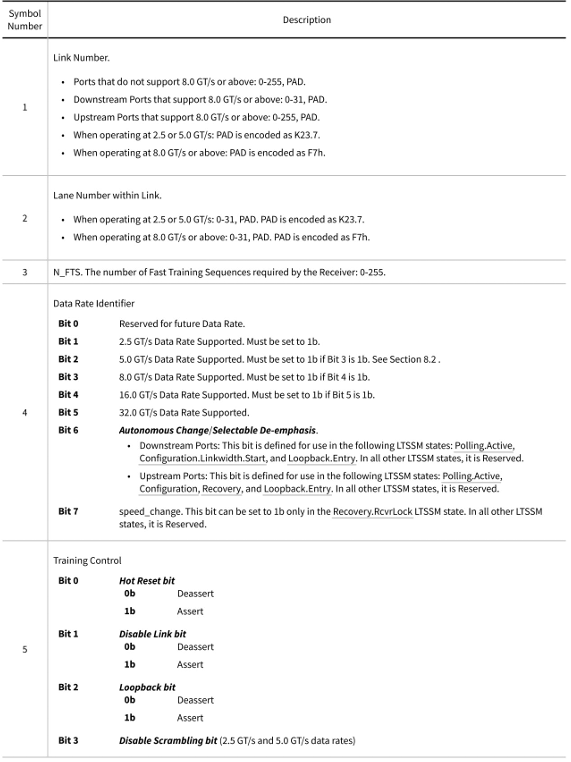

打算协商备用协议或传递一个TrainingSetMessage的组件必须在Configuration.Lanenum.Wait,Configuration.Lanenum.Accept 和 Configuration.Complete 子状态中使用 Modified TS1/TS2 Ordered Set,而不是 TS1/TS2 OrderedSet。为了可以发送 ModifiedTS1/TS2 Ordered Set,组件必须在Polling.Active,Polling.Configuration,TS1/TS2 Ordered Set 中将 TS1 和 TS2 有序集的 Enhanced Link behavior Control 字段设置为 11b, Configuration.Linkwidth.Start 和 Configuration.Linkwidth.Accept 子状态,并执行 LinkUp = 0b 时过渡到 Configuration.Lanenum.Wait 子 状 态 中 概 述 的 步 骤 。 如 果 链 路 伙伴不支持 Modified TS1/TS2 Ordered Set , 则 从 Configuration.LaneNum.Wait 开始,标准 TS 应停止在Enhanced LinkbehaviorControl 字段中发送 11b 并切换到适当的编码。

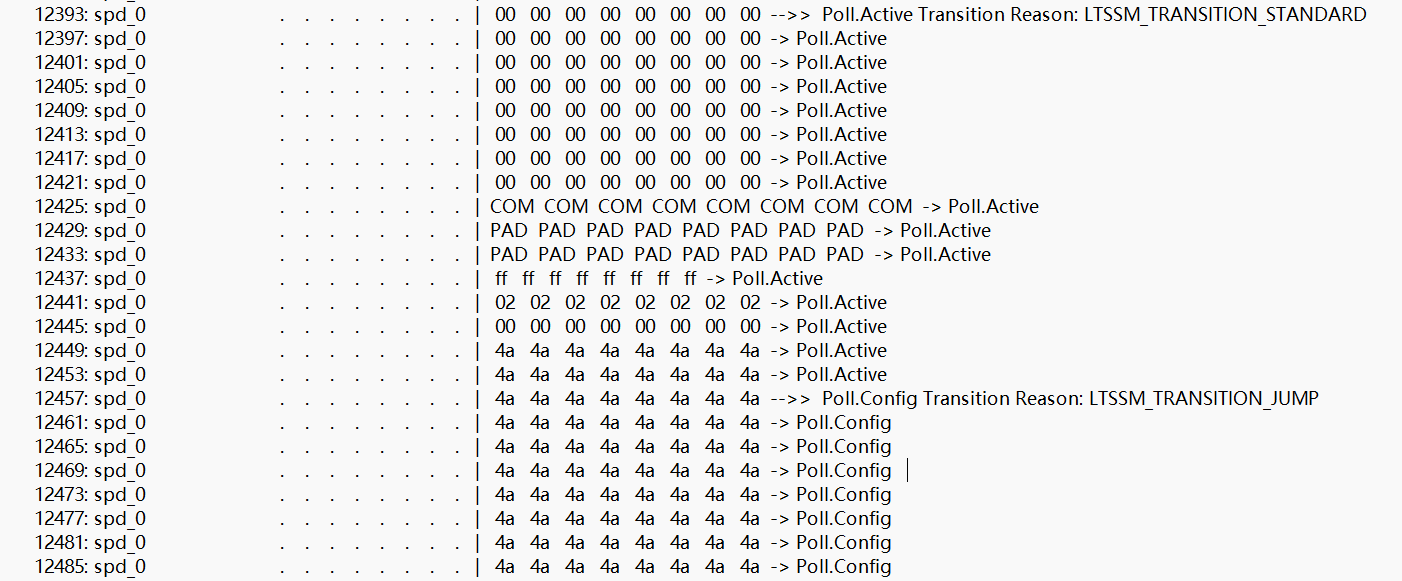

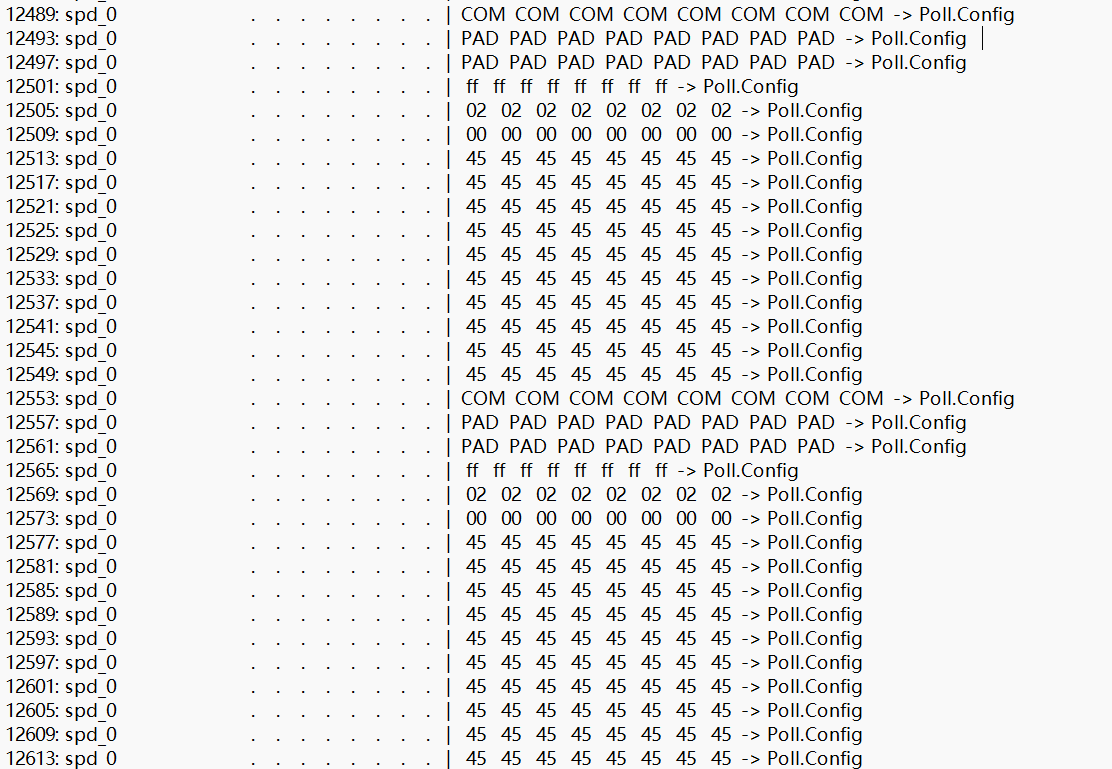

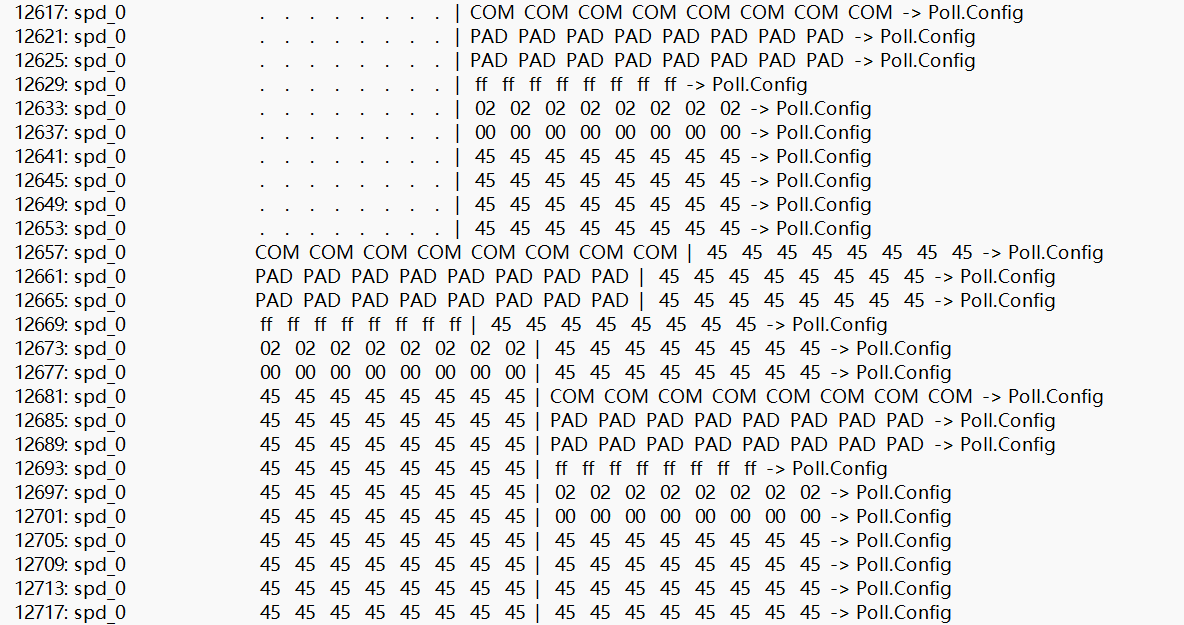

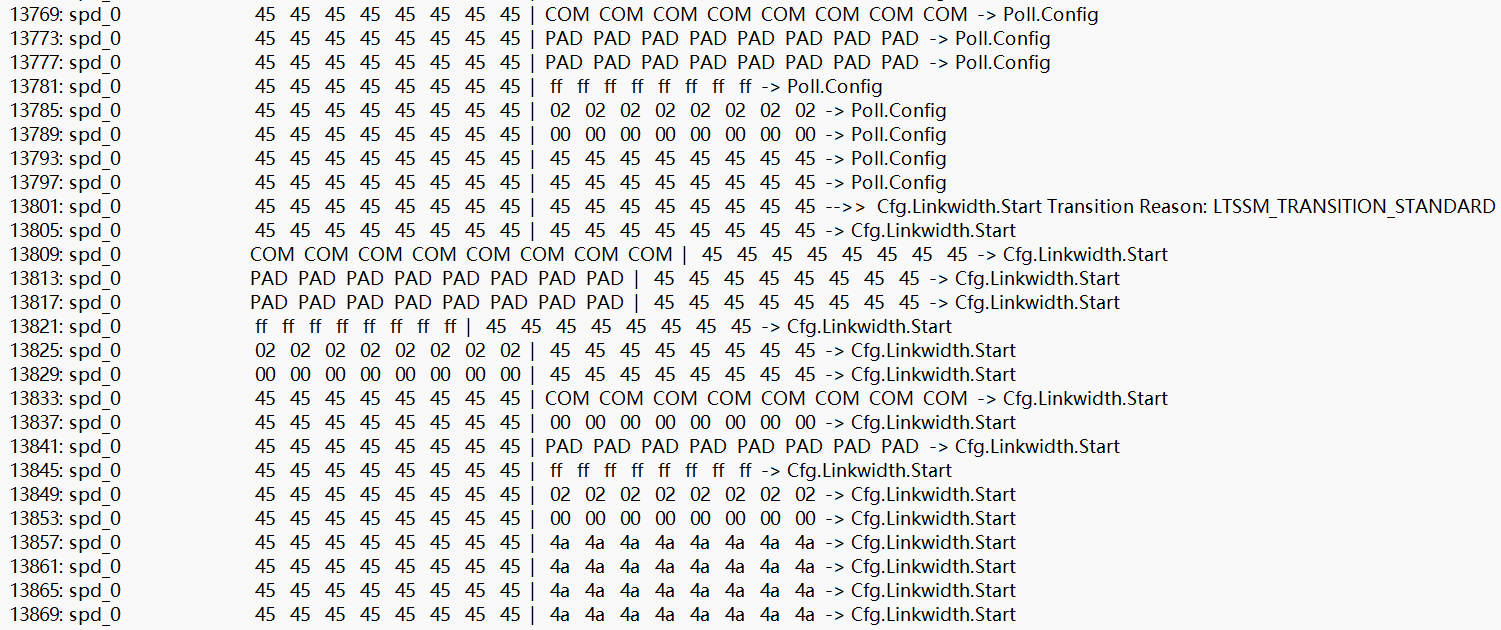

给出一个polling阶段OS的在lane上的发送示例:

直至双方协商polling完毕后,进入下一个状态

直至双方协商polling完毕后,进入下一个状态

Polling概述

在PCIe的 LTSSM状态机中,Polling态进Configuration状态是一个关键的步骤,标志着链路两端已经建立了基本的物理层通信,并准备开始协商链路的工作参数(如链路宽度和操作速率)。Polling状态成功进入 Configuration状态的条件和过程:

1. 完成接收器检测和锁定 (Receiver Detection and Locking

在 Polling.Active 子状态,每个端口(按照距离CPU的远近分为下游端口和上游端口)都会在所有配置的 Lane 上交替发送 TS1 (Training Sequence 1) 有序集。

这些 TS1 序列有两个主要目的:

* 接收器检测 (Receiver Detection):确认对端确实存在一个活动的接收器。

* 位锁定 (Bit Lock) 和 符号锁定 (Symbol Lock):接收端的物理层 (PHY) 使用传入的 TS1 序列来锁定发送端发送数据的比特边界(位锁定)和识别 COM (Comma) 符号以确定符号边界(符号锁定)。这是正确解码后续数据的基础。

2. 交换 TS1 序列并达成基本协议 (Exchange TS1s and Basic Agreement):

两端设备通过接收对方发送的 TS1 序列,不仅确认了对方的存在和活动状态,还能从TS1中携带的信息字段获取对方的基本能力:

* Link Number:通常是未配置的(0xFF)。

* Lane Number:发送该TS1的物理Lane的编号(在 Polling 阶段通常是未配置的,如 0x1F 或 PAD 值)。

* Rate ID:发送端支持的最高链路速率(Gen1, Gen2, Gen3, Gen4 等)。

* 其他控制位:如 Disable Link、Loopback 等(通常不设置)。

* 最关键的是,两端通过持续接收有效的 TS1 序列确认链路在物理层是连通的,并且双方都支持至少一个共同的链路速率(通常是 Gen1,作为基础速率)。

3. 进入 Configuration 状态的条件 (Transition Condition):

LTSSM 从 Polling 状态(具体是 Polling.Active)进入 Configuration 状态需要满足以下核心条件:

* 在 `N_FTS` 个连续时间内(通常是一个预设的超时值,例如 24ms),在所有配置的 Lane 上,本地接收器持续检测到来自对端的有效 TS1 有序集。这里的“有效”意味着:

** 接收到的 TS1 的符号被正确解码(依赖于之前完成的位锁定和符号锁定)。

** TS1中包含的 `Link` 和 `Lane` 编号信息表明对方设备存在且正在尝试建立链路(通常 `Link=0xFF`, `Lane=0x1F` 或 PAD)。

* 本地接收器的位锁定 (Bit Lock) 和符号锁定 (Symbol Lock) 已经成功完成。这是正确接收和理解 TS1 的前提。

4. 状态转换:

一旦上述条件满足(即在规定时间内稳定地接收到有效的 TS1,且本端锁定成功),LTSSM 就会触发状态转换。 状态机从Polling.Active退出,并进入Configuration.Linkwidth.Start子状态 (Configuration 状态下的第一个子状态)。

5. 设备是怎么知道bit锁定和symbol锁定?

在 PCIe 链路训练过程中,接收端设备无法直接通过解析接收到的 TS1 内容本身来“知道”发送端是否完成了位锁定 (Bit Lock) 或块锁定/符号锁定 (Block/Symbol Lock)。相反,接收端通过自身成功完成位锁定和块锁定,并能够持续、正确地解析接收到的 TS1 有序集的内容,从而推断出链路状态良好,并触发状态转换。发送端则通过接收来自对端的、内容正确的 TS1 来推断对方已经锁定。

1. 位锁定 (Bit Lock) 和块锁定/符号锁定 (Block/Symbol Lock) 的本质:

位锁定 (Bit Lock):这是接收端物理层 (PHY) 时钟和数据恢复电路 (CDR) 的功能。CDR 利用接收到的数据流来调整其本地采样时钟的相位,使其能够准确地在每个比特位的中心位置进行数据重采样。成功完成位锁定意味着接收器能够可靠地区分出数据流中的单个比特 `0` 和 `1`。

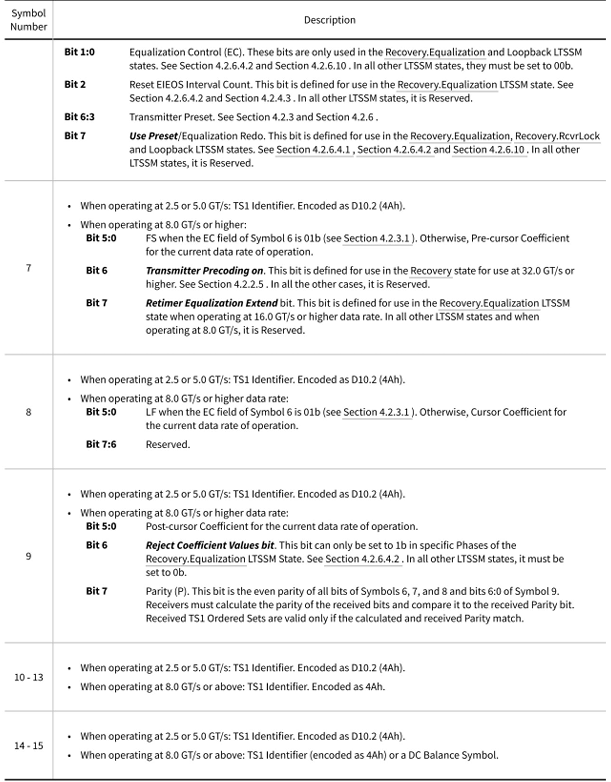

块锁定/符号锁定 (Block/Symbol Lock):PCIe 使用 8b/10b (Gen1, Gen2) 或 128b/130b (Gen3+) 编码。接收器需要识别编码方案中定义的“特殊控制符号”来找到符号边界。对于 8b/10b,关键的控制符号是 `COM` (Comma, K28.5)。`COM` 符号具有独特的、在数据流中不会出现的比特模式(如 `0011111010` 或 `1100000101`)。接收器在数据流中搜索这些独特的 `COM` 模式。一旦连续检测到几个有效的 `COM` 符号(通常是 3 个),并且它们出现在预期的间隔位置(例如,每 16 个 10-bit 符号出现一次,因为 TS1 是 16 个符号的有序集),接收器就确定了符号边界,完成了块锁定/符号锁定。这意味着接收器能正确地将连续的比特流分割成一个个独立的 10-bit (或 130-bit block) 符号进行解码。

2. 怎么利用TS1 的信息交换?含有那些信息?

* TS1 有序集是链路训练期间交换的主要信息单元。它包含重要的字段,如:

* `Link Number` (通常初始为 `0xFF` - Unconfigured)

* `Lane Number` (通常初始为 `0x1F` - Unassigned 或 PAD)

* `Rate ID` (支持的速率)

* `N_FTS` (需要多少个 Fast Training Sequences 用于后续速率切换的时钟补偿)

* 其他控制位 (如 Disable Link, Loopback, Hot Reset 等)。

* 关键:TS1 的有序集结构本身(特别是包含的 `COM` 符号)是实现块锁定/符号锁定的关 键信号源。

3. 如何“知道”锁定完成 (接收端视角):

* 接收端自身硬件完成锁定: 接收端的 PHY 层电路在接收到对端发送的TS1 流后,会在内部执行位锁定和搜索 `COM` 符号的过程。

* 锁定成功的标志是能正确解析 TS1 内容:因为只有当接收端 PHY 成功完成了位锁定和块锁定,它才能:

A. 准确地将比特流分割成符号 (`COM` 和其他符号)。

B. 正确解码每个符号(将 10b 解码为 8b 数据/控制符,或识别 130b block)。

C. 识别出接收到的有序集确实是 TS1(因为它能识别出 `COM` 符号以及紧随其后的特定数据模式)。

D. 提取出 TS1 中包含的有效信息(`Link Number`, `Lane Number`, `Rate ID` 等)。

状态机转换的依据:LTSSM 在 Polling 状态(Polling.Active)监测接收逻辑。如果接收逻辑报告在配置的所有 Lane 上,在 `N_FTS` 个连续时间内(例如 24ms),持续接收到内容有效且符合预期的 TS1 有序集(例如,`Link=0xFF`, `Lane=0x1F` 或 PAD,且无错误标志),那么 LTSSM 就认为:

* 物理层连接可靠(信号质量足够好)。

* 本端接收器已经成功完成了位锁定和块锁定**(因为只有这样它才能持续正确地解析 TS1 的内容)。

* 对端设备存在且也在积极发送 TS1(意味着对端很可能也检测到了本端的存在并完成了其接收端的锁定)。

* 因此,接收端“知道”锁定完成(主要是自己的锁定完成)是通过其自身 PHY 能够持续、正确、无错误地解析出对端发来的 TS1 内容来体现的,因为这种持续正确的解析是接收端内部完成了锁定的直接体现。

4. 发送端视角 & 对端的锁定状态:

* 发送端只是按照协议要求在 Polling.Active 状态持续发送 TS1 有序集。

* 发送端无法直接感知自己发送的信号是否被对端成功锁定,它只能通过接收来自对端的 TS1来间接判断。

* 如果发送端在接收通道上也开始持续接收到内容正确且符合预期的 TS1 有序集(意味着发送端自己的接收PHY也完成了锁定,那么发送端的 LTSSM 就会认为满足了进入Configuration状态的条件。

A.当发送端持续接收到有效的TS1 时,发送端推断对端锁定完成,对端设备发送TS1这个行为隐含了对端已经检测到了本端的存在,并且很可能对端的发送逻辑已经准备完毕。更重要的是,本端的接收器能够正确解析这些TS1,意味着本端接收器的位锁定和块锁定已经完成。虽然发送端无法直接确认对端接收器的锁定状态,但通过对端持续发来有效的TS1,可以推断对端的发送逻辑是正常工作的,并且本端到对端的链路也是通的(因为对端需要检测到本端的TS1才会进入发送 TS1状态)。

B.最终双方都持续接收到有效 TS1 是双向链路完成polling到下一个config的转移

举个简单的比方来说:设备不是通过“读取”TS1里的某个特定字段来知道锁定完成的。而是它发现自己能稳定地“听懂”(正确解析)对方发来的TS1“话语”时,就证明自己的“耳朵”(接收PHY)已经调整好了(完成了位锁定和块锁定)。同时,听到对方在持续说话(发TS1),就知道对方也在积极沟通。当双方都持续听到对方清晰的话语(有效TS1)一段时间后,就认为物理层沟通基础已经打好,可以进入下一阶段(Configuration)商量具体细节了。

Polling详细解剖

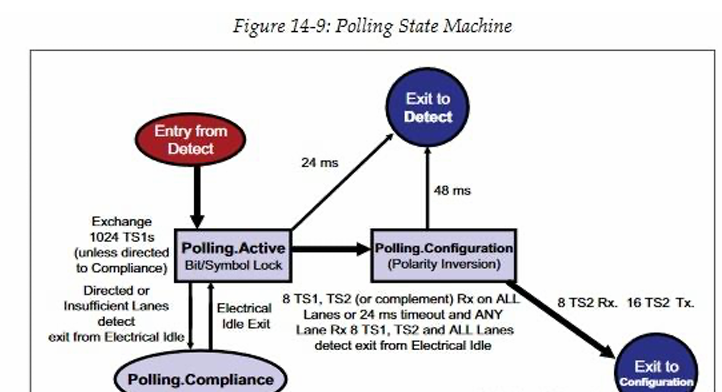

上面简单了说了一些基本常识,下面细节一点,当LTSSM 进⼊轮询状态时,链路处于电⽓空闲状态,不过,轮询状态期间会在链路两端之间交换 TS1 和 TS2 有序集。轮询状态的主要⽬的是使链路两端的设备能够听懂对⽅在说些什么,换句话说,他们需要各⾃在对⽅的发送⽐特流上,建⽴⽐特和符号锁定状态,并且解决极性翻转 (polarity inversion)恢复之类的事宜。在这些⼯作完成后,设备们才能够正确地接收对⽅发出的 TS1 和 TS2 有序集。下图展示了轮询状态的 各个⼦状态:

Polling.Active 期间

⼀旦链路双⽅的共模电压稳定在发送余量( Transmit Margin)域中允许的范围内之后,发送⽅会发送⾄少 1024 个连续的 TS1 有序集。因为链路双⽅退出检测状态的时刻可能不同,所以 TS1 命令序列的交换不是同步的。在 Gen1(2.5GT/s) 速率下,发送 1024 个 TS1 序列花费 64us 。

Active 次状态下,有⼀些值得注意的细节: 必须在 TS1 序列的通道(Lane)和链路编号(Link number)字段中使⽤PAD字符设备需要通告(advertise)⾃⼰⽀持的所有速率,哪怕设备并不打算使⽤这些速率;接收⽅使⽤接收到的 TS1 序列实现⽐特锁定和符号锁定(低于 8GT/s 的速率)或者块锁定(8GT/s 速率)

为什么至少要发送1024个TS1,并至少接收8个为准?

接收端的符号锁定电路需要连续检测到一定数量的有效 `COM` 符号(通常是 3 个),并且它们出现在预期的间隔位置(例如,每 16 个符号出现一次,因为一个 TS1 有序集包含 16 个符号),才能确认成功锁定。

1024 个 TS1 提供了海量的 `COM` 符号机会:每个 TS1 有序集至少包含 1 个 `COM` 符号(通常是第一个符号)。发送 1024 个 TS1 就意味着发送了至少 1024 个 `COM` 符号。这么做的目的:

A.这个巨大的数量确保了即使在存在严重的噪声、干扰或信号完整性问题的极端情况下,接收端也有极高的统计概率能够在其接收到的信号流中找到足够数量(远多于最低要求的 3 个)的有效 `COM` 符号序列,从而成功实现并确认符号锁定。它大大降低了因随机噪声或瞬时干扰导致锁定失败的可能性。

B.提供足够的稳定时间:接收端的时钟数据恢复 (CDR) 电路需要时间来收敛并稳定地锁定到发送端的比特率(位锁定)。而且符号锁定电路也需要在锁定后,持续观察一段时间以确认锁定的稳定性和正确性。

1024 个 TS1 的时间窗口,在 PCIe Gen1 (2.5 GT/s) 基础速率下:

* 一个 TS1 有序集有 16 个符号。

* 每个符号是 10 比特(8b/10b 编码)。

* 发送一个 TS1 需要 `16 symbols * 10 bits/symbol / 2.5e9 bits/sec = 64 ns`。

* 发送 1024 个 TS1 需要 `1024 * 64 ns = 65.536 μs`。

在 Gen2 (5.0 GT/s) 下,时间减半为 `~32.768 μs`。这个时间量级(几十微秒)对于典型的 CDR 和符号锁定电路来说,是一个合理的稳定时间窗口。它允许电路克服初始抖动、适应通道特性并达到稳定状态。

C.确保通道检测的确定性,在 `Polling` 状态之前是 `Detect` 状态。`Detect` 状态负责初步检测对端是否存在接收器。而1024 个 TS1 的要求,是对 `Detect` 状态结果的最终确认。它要求链路不仅在 `Detect` 瞬间被认为“存在”,还必须能在相对较长(微秒级)的时间内持续稳定地传输和接收训练序列,避免因瞬时连接或噪声尖峰导致的误检测。

8个连续的 TS1” 是锁定成功后的稳定性验证:

即使接收端在某个瞬间报告了锁定,也需要确认这种锁定是持续稳定的,而不是瞬态或错误的。而8 个连续的 TS1 要求,是在发送方发送完其设定的 TS1 序列(至少 1024 个)之后,接收方必须在所有检测到的通道 (Lane) 上,连续无误地接收到 8 个完整的 TS1 有序集(如果存在极性反转,接收到的就是 TS1 的补集,但能被正确识别为有效 TS1)。这么做的目的:

A.验证位锁定的稳定性:连续正确接收 8 个 TS1(每个 TS1 包含 160 比特 Gen1/2)需要 CDR 电路在整个接收过程中都保持精确的位锁定。

B.验证符号锁定的稳定性:每个TS1 中的 `COM` 符号必须被连续、正确地识别8次。

C.验证通道均衡初步有效性 (可选):在支持接收端均衡 (`RxEQ`) 的 `Polling.RxEQ` 子状态中,这 8 个连续的 TS1 也用于验证接收端应用的初始均衡设置是否足够好,能支持无错误接收。如果在此阶段有错误,状态机可能不会立即进入 Configuration,而是尝试调整均衡或进入 Recovery。

D.确保参数一致性:接收到的这 8 个 TS1 的内容(`Link`, `Lane`, `Rate ID` 等)必须是一致的,表明对端设备在稳定发送相同的配置信息

Active转移至Polling.Configuration

在发送⽅发送完 1024 个 TS1 ⾥最后⼀个 TS1 序列之后,如果所有检测到的通道都收到了 8 个连续的训练序列(如果存在极性翻转的话,那么 收到的就是训练序列的补集),并且这些训练序列满⾜以下条件之⼀的 话,状态机进⼊ Polling.Configuration 状态:

A.接收到的 TS1 的链路和通道字段全部被设置为全填充字符 (PAD),并且 Compliance Receive ⽐特设置为 0b (符号 5 的 ⽐特 4)

B.接收到的 TS1 的链路和通道字段都被设置为全填充字符,并且 Loopback ⽐特设置为 1b (符号 5 的 ⽐特 2)

C.接收到的 TS2 的链路和通道字段都被设置为全填充字符.

如果上述条件都没能满⾜,那么在 24ms 的超时之后,在接收到某个 TS1 之后,已经发送了 1024 个 TS1 序列,只需要任意检测到的通道接 收到了 8 个连续的TS1 序列或者 TS2 序列,通道以及链路编号是填充符 号,并且满⾜以下条件之⼀(译注:其实以下条件和超时前的判断条件 ⼀致),那么状态机进⼊ Polling.Configuration 状态。

A. 接收到的 TS1 的链路和通道字段全部被设置为全填充字符 (PAD),并且 Compliance Receive ⽐特设置为 1b (符号 5 的 ⽐ 特 4)

B.接收到的 TS1 的链路和通道字段都被设置为全填充字符,并且 Loopback ⽐特设置为 1b (符号 5 的 ⽐特 2)

C.接收到的 TS2 的链路和通道字段都被设置为全填充字符

备用机制(降级lane number)

如果在任意通道上都没有满⾜上述条件的情况出现,那么如果⾃进⼊ Polling.Active 状态以来,有超过预定数量的通道上检测到⾄少⼀次退出电⽓空闲的现象(这是为了防⽌⼀个或者多个失效的发送端或者接收端 导致链路不能能进⾏配置),那么也能进⼊ Polling.Configuration 状 态。

这个机制是 PCIe LTSSM 状态机在Polling.Active子状态下,当无法通过常规的 TS1 交换条件进入 Configuration 状态时的一种容错和恢复路径。它允许链路在部分通道(Lane)出现故障时,仍有可能继续训练过程,尝试建立部分宽度的可用链路,而不是完全失败。以下进行详细解释:

1. 常规进入 Configuration 状态的条件失败:

* 在 Polling.Active 状态,设备会持续发送 TS1 并监听接收到的 TS1。

* 进入 Configuration 状态的条件是:在 `N_FTS` 时间窗口内,在所有配置的 Lane上,持续、稳定地接收到有效的 TS1 有序集,并且本端接收器也完成了位锁定和符号锁定。

如果在任意通道上都没有满足上述条件的情况出现:这意味着在 `N_FTS` 超时期限内,至少存在一个 Lane上未能持续接收到有效的 TS1 序列(例如,完全没收到、收到无效 TS1、收到 TS2、错误太多、锁定失败等)。

2. 备选条件:检测“退出电气空闲” (Exit from Electrical Idle):**

* 当主要条件不满足时,状态机不会立即宣告失败(如进入 Detect 或 Loopback 等恢复状态),而是检查一个备选条件, 这个条件是自进入 Polling.Active 状态以来,在超过某个“预定数量”的Lane 上,检测到至少一次“退出电气空闲” (Exit from Electrical Idle) 的现象。

退出电气空闲?

* 电气空闲 (Electrical Idle, EI)是 PCIe 物理层的一种低功耗状态。在 EI 状态下,发送器停止发送差分信号,并将差分电压驱动到接近 0V (共模电压不变)。

* 退出电气空闲 (Exit from EI)是指发送器离开 EI 状态,开始发送有效的差分信号(如 TS1)的过程。这个过程会在链路上产生一个明显的、可检测的电气瞬变(差分电压从 ~0V 跃升到正常的信号电平)。

如何检测“退出电气空闲”?

* 接收端的物理层 (PHY) 电路包含电气空闲退出检测器 (Electrical Idle Exit Detector, EIED)。EIED 监测差分线路上的电压变化。当检测到差分电压在特定时间内超过一个预设的阈值(通常远低于正常信号幅度,但明显高于 EI 噪声水平),它就认为检测到了一次“退出电气空闲”事件。通常这个检测发生在信号解码之前,不依赖于位锁定、符号锁定或 TS1 内容解析。它是一种非常底层的、对物理信号存在性的探测。

设计这个机制的意义防止一个或者多个失效的发送端或者接收端导致链路不能进行配置,这是该机制的核心目标。

* 场景1 (发送端失效):某个 Lane 的对端发送器可能完全故障,无法发送任何信号(包括 TS1),在常规条件下,这个 Lane 永远收不到 TS1,会阻止整个链路进入 Configuration。

* 场景2 (接收端失效):某个 Lane 的本端接收器可能故障(如位锁定/符号锁定电路损坏),导致它无法正确解析任何信号,即使对端发送了有效的 TS1,它也无法报告“接收到有效 TS1”。

* 检测到退出电气空闲”的含义:在一个 Lane 上检测到 Exit EI 事件,表明**该 Lane 的对端发送器很可能在工作**(它至少尝试发送了信号)。同时它也表明该 Lane 的物理连接(包括本端接收器的基础模拟前端)很可能基本完好,能够检测到这个电气瞬变。

解释一下什么是超过预定数量的通道” (Predetermined Number of Lanes):预定数量” 由具体实现决定 (Implementation Defined):这意味着设计者可以根据系统需求和容错策略来设定这个阈值。

* 基于链路宽度:例如,对于 x16 链路,阈值可能设为 12 或 14 个 Lane (即允许 2-4 个 Lane 故障)。对于 x4 链路,阈值可能设为 3 或 4 个 Lane (允许 0-1 个故障)。

* 最小可用宽度: 阈值可能设定为支持链路最低可用宽度所需的 Lane 数(例如,PCIe 支持 x1, x2, x4, x8, x16,即使配置为 x16,如果检测到 8 个可用 Lane,也可能尝试建立 x8 链路)。

* 只要足够数量的 Lane 表现出“有活跃发送器存在”(检测到 Exit EI),就认为链路有希望建立部分连接,值得尝试进入 Configuration 状态进行进一步的协商和可能的降级(Lane 缩减)。

状态转换

如果主要条件不满足(即至少一个 Lane 没收到连续有效的 TS1),但备选条件满足(即超过预定数量的 Lane 检测到至少一次 Exit EI),那么状态机将进入 Configuration 状态(Configuration.Linkwidth.Start)。Configuration 子状态机(特别是 Linkwidth 协商)会负责识别和排除那些有问题的 Lane,最终建立可用的(可能是缩减宽度的)链路。在进入 Configuration 状态后,设备会继续尝试进行链路宽度协商(Link Number 和 Lane Number 分配)。在这个过程中,那些未能满足主要条件的 Lane(即未能正确交换 TS1 的 Lane)很可能在 Configuration 状态中被标记为失败(例如,分配到 `Link=0xFE` 的“坏 Lane 集合”中,最终链路会以缩减的宽度(例如,x8 而不是 x16)向上层报告 L0 状态。

还是举个例子吧:当正常“握手”(交换TS1)因为一两条“线”(Lane)坏了而失败时,PCIe协议提供了一个备选方案:检查大部分“线”上是否有对方“喊话”的迹象(检测到退出电气空闲)。如果有足够多的“线”能听到对方“喊了一嗓子”,就认为还有救,于是进入下一阶段(Configuration)去具体商量哪些“线”还能用,最终可能建立一条比预期窄但还能工作的“路”(链路)。这个机制显著提高了PCIe链路在面对个别通道硬件故障时的生存能力。

Active转移至Polling.Compliance

如果 Link Control 2 寄存器中的Enter Compliance⽐特被设置为1, 那么进⼊Polling.Compliance。或者如果在进⼊ Polling.Active 状态之前,该⽐特已经被置位,那么将直接从 Active 状态进⼊ Compliance 状 态,不会在 Active 状态中发送任何 TS1 序列。若未设置 Enter Compliance bit,在 Polling.Active 等待 24ms 后,满足以下任一条件,再次判断进⼊ Compliance 状态的条件:

A.所有的通道在进⼊ Active 状态后,都没有检测到对端退出电⽓空闲状态,即无活动信号。(这意味着对端是⼀个被动测试负载,⽐如在⾄少⼀个通道 上挂载了⼀个测试电阻,将强制使所有通道进⼊ Compliance 状 态。)

B.接收到 8 个连续的 TS1 ,其链路和通道字段全部被设置为全填充字符(PAD),并且 Compliance Receive ⽐特设置为 1b (符号 5 的 ⽐特 4),并且 Loopback ⽐特设置为 0b (符号 5 的 ⽐特 2)。

为何需要 24ms 等待?

-

这是

Polling.Active状态的超时窗口(N_FTS典型值)。 -

确保有足够时间检测对端是否存在正常设备(若能收到有效 TS1,则进入常规链路训练)。

-

若超时后仍无有效信号或收到特定测试序列,则判定为测试环境。

未检测到退出电气空闲 (Condition A)

-

现象: 所有 Lane 的接收端始终处于电气空闲 (Electrical Idle) 状态。

-

原因: 对端是被动测试负载(如:

-

在差分线上连接

50Ω电阻到地(模拟接收端)。 -

无信号发送能力,因此无法触发 "Exit Electrical Idle" 事件。

-

-

意义: 强制进入 Compliance 状态以执行接收端电气测试(如差分电压、共模噪声等)。

Active转移至 Detect State

如果在 24ms 之后,没有满⾜进⼊ Polling.Configuration 状态或者 Polling.Compliance 状态的条件,那么返回 Detect 状态。