1、cadence从零开始让一个VCO起振——基本设置

怎么放元件,设参数等其他基础操作跳过了,如果不会可以查其他的资料或在评论区讨论。

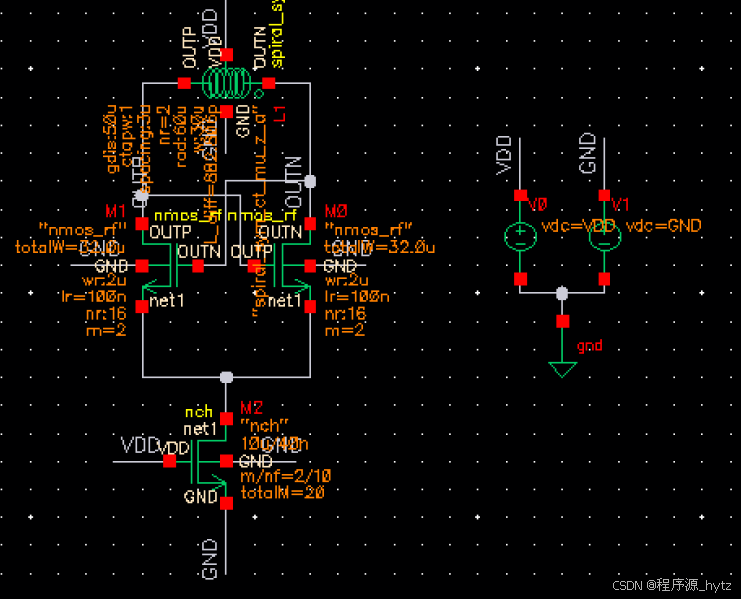

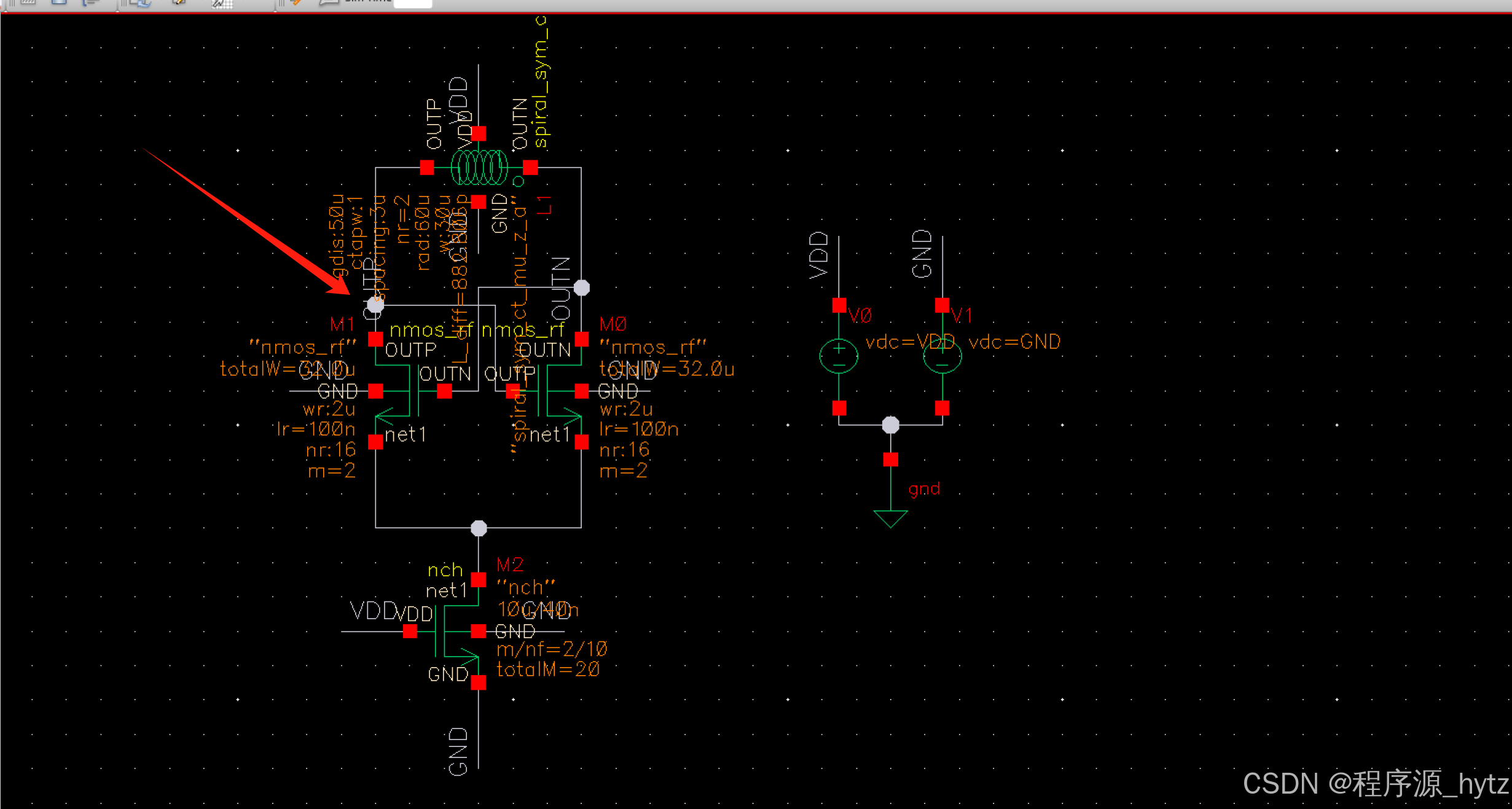

1、先在原理图schematic搭一个最简单的并联谐振VCO:(管子取什么工艺都可以,理想模拟库也可以,这里为方便我用的是tsmc 40nm)

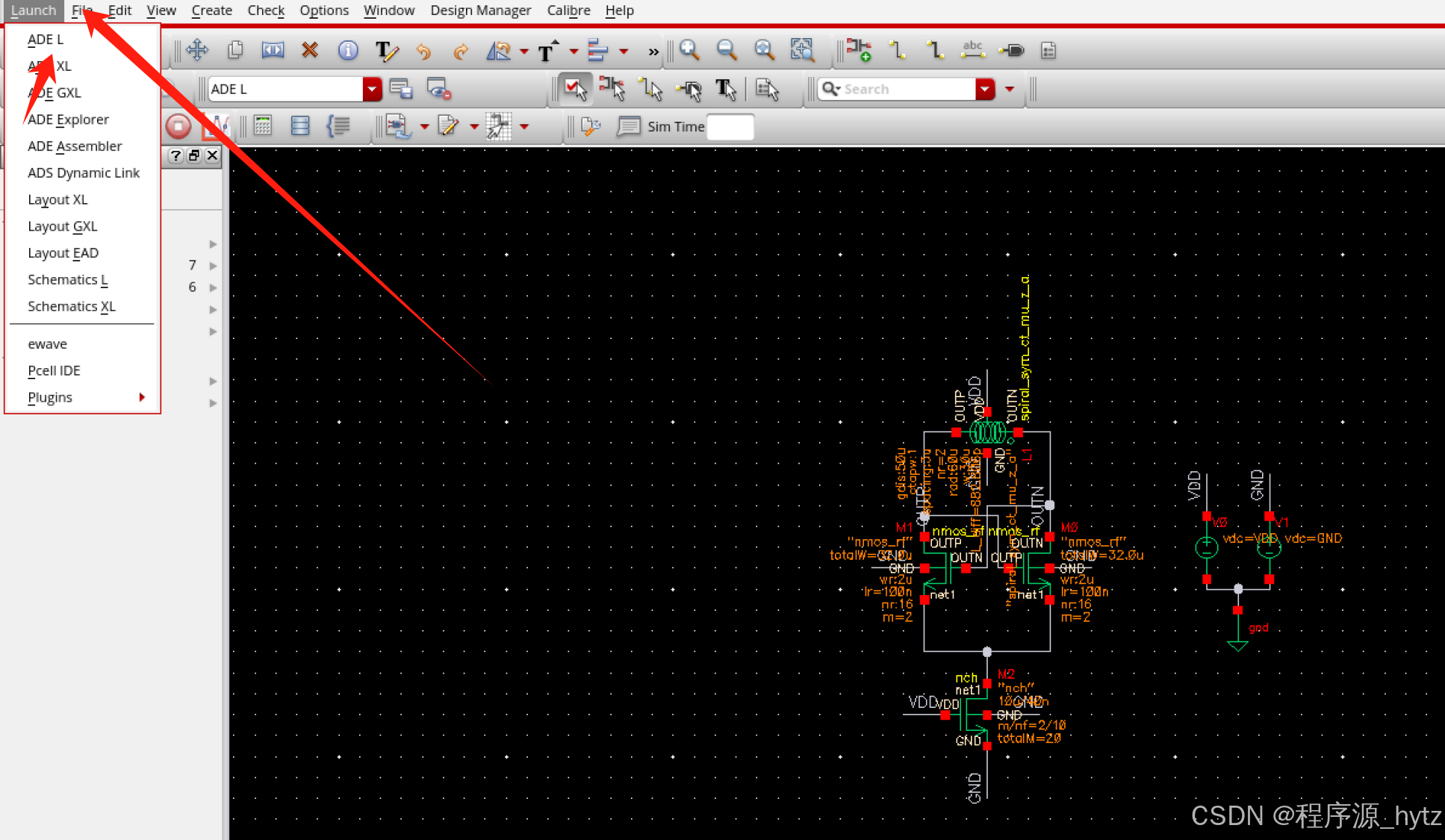

2、找到界面左上角“Launch”,打开仿真ADE L

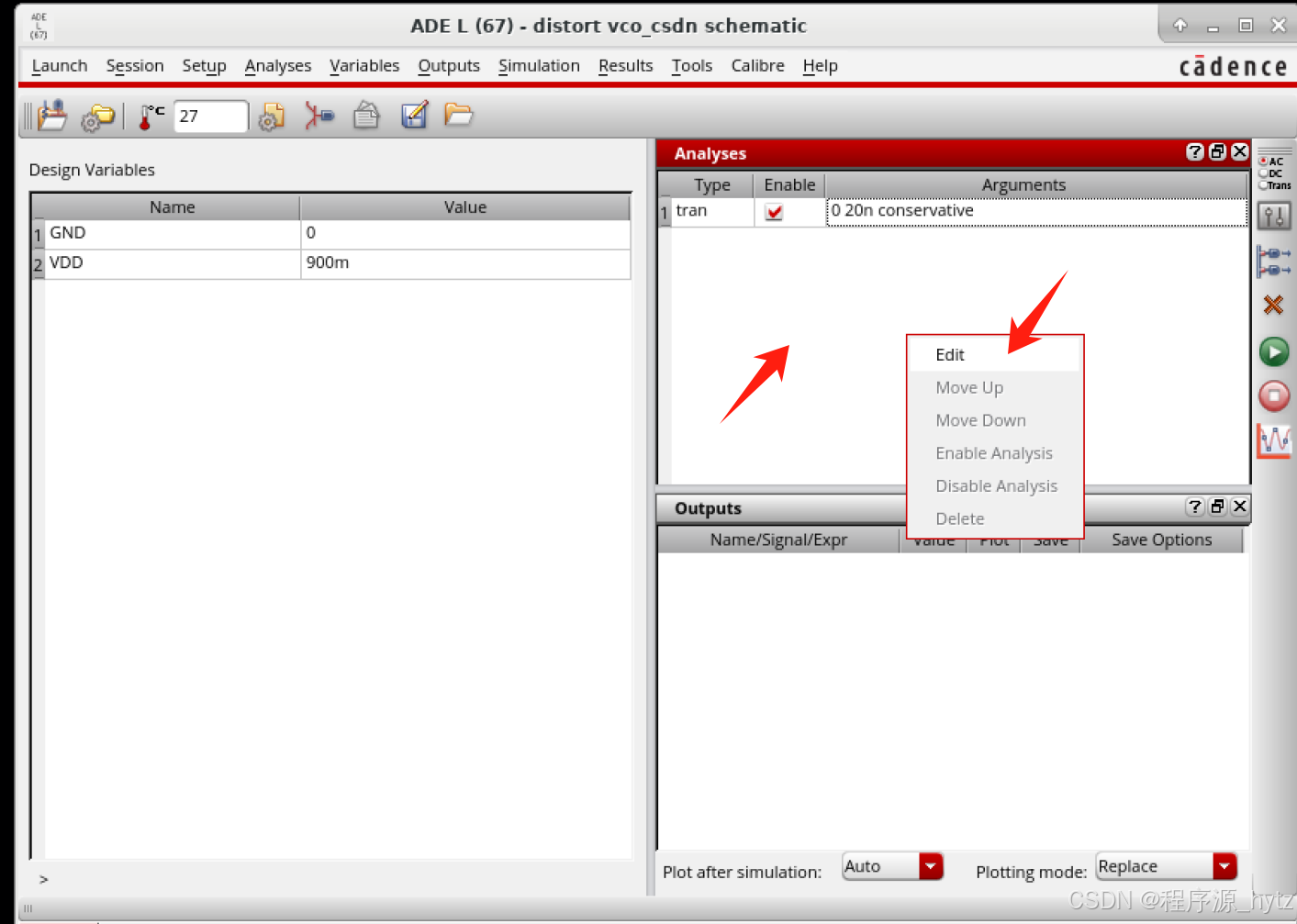

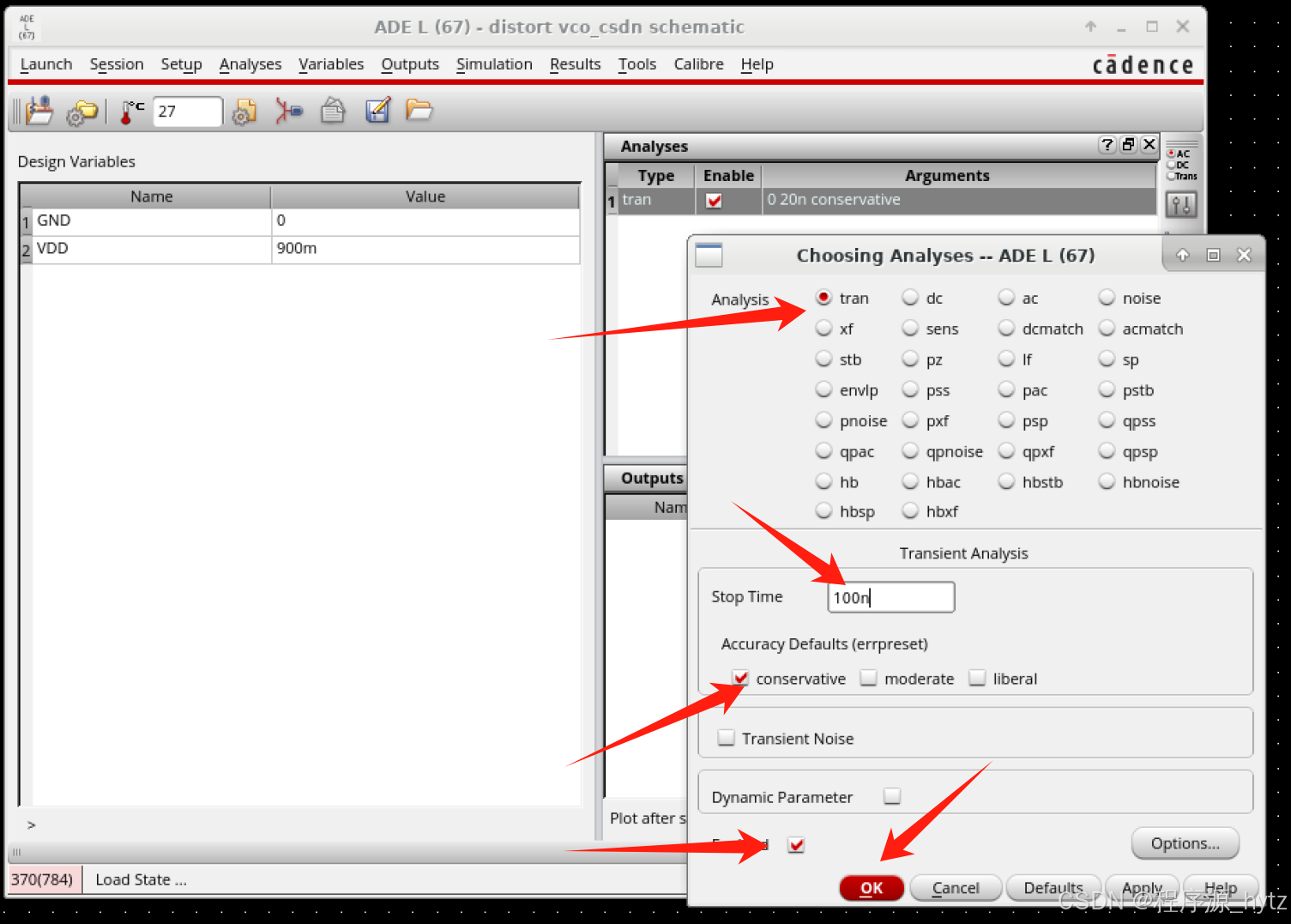

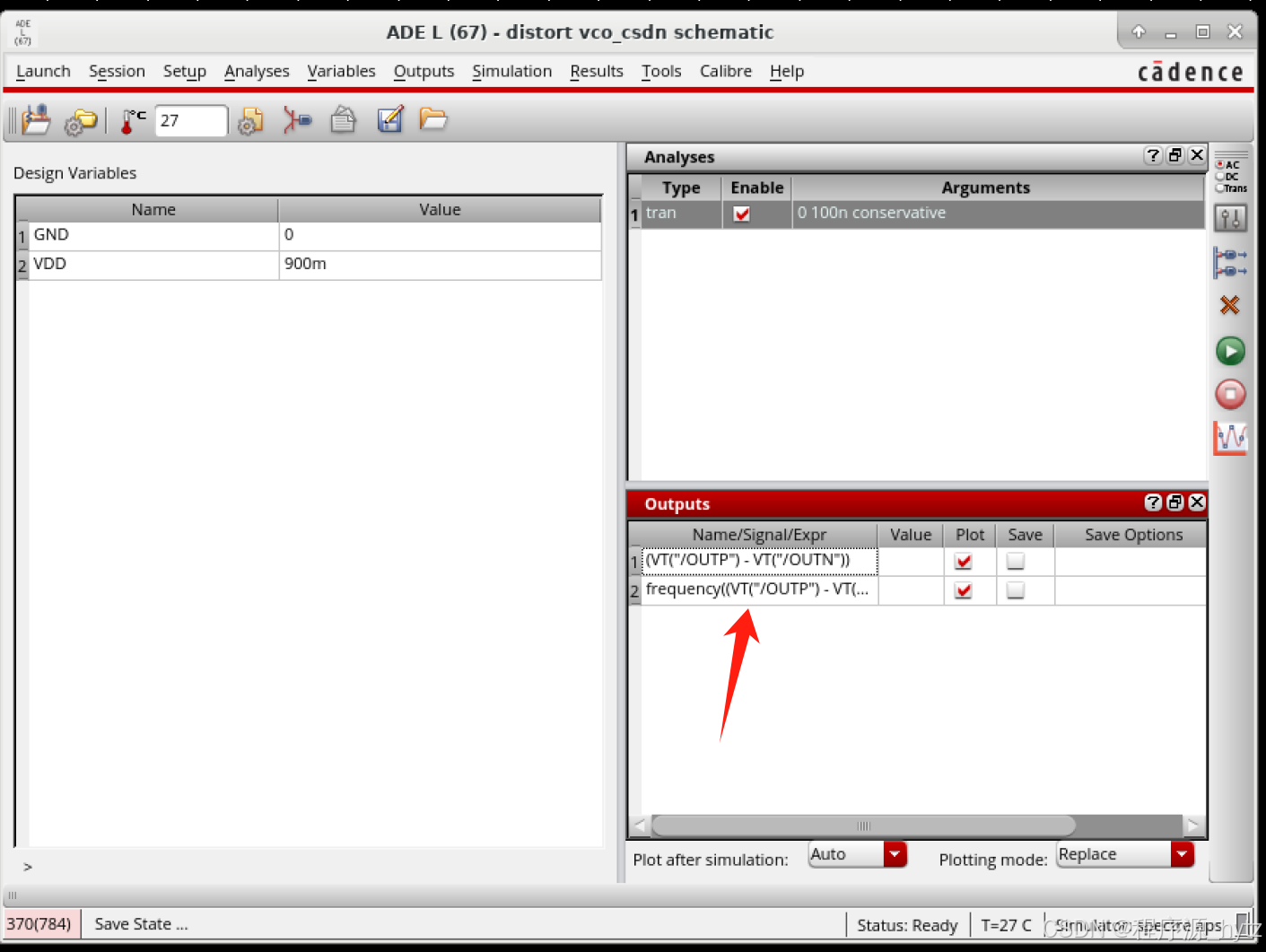

3、在analyses空白处右键,点击edit,进行如下设置,点ok确定。

(tran是瞬态仿真,即仿真出来是随时间变化的信号波形,stop time是信号时间长短,一般如果是1G谐振频率以上100n可以看到重复的谐振波了。conservative、moderate、liberal是仿真的准确度,从左到右依次降低,最后点一下enabled,并点击OK)

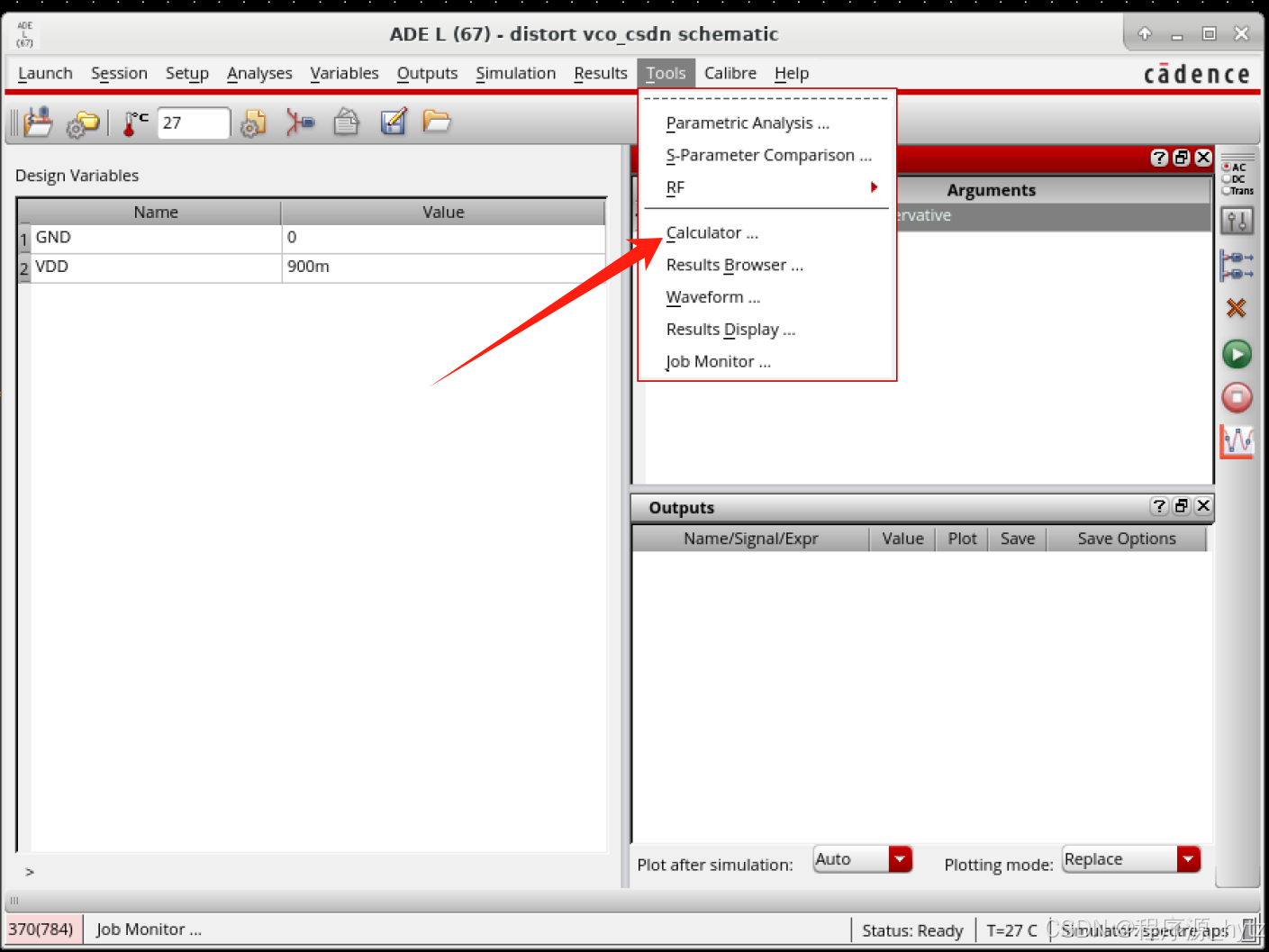

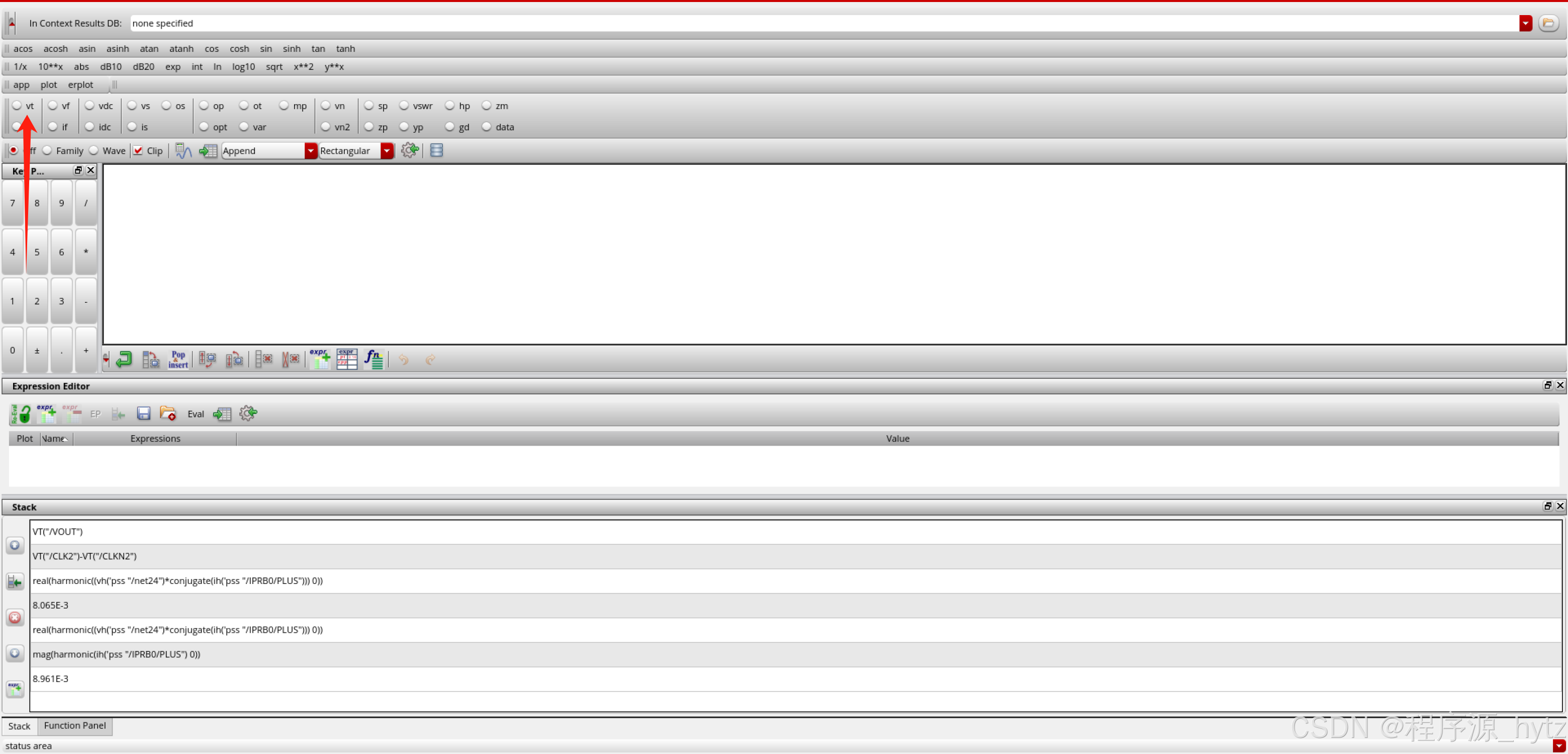

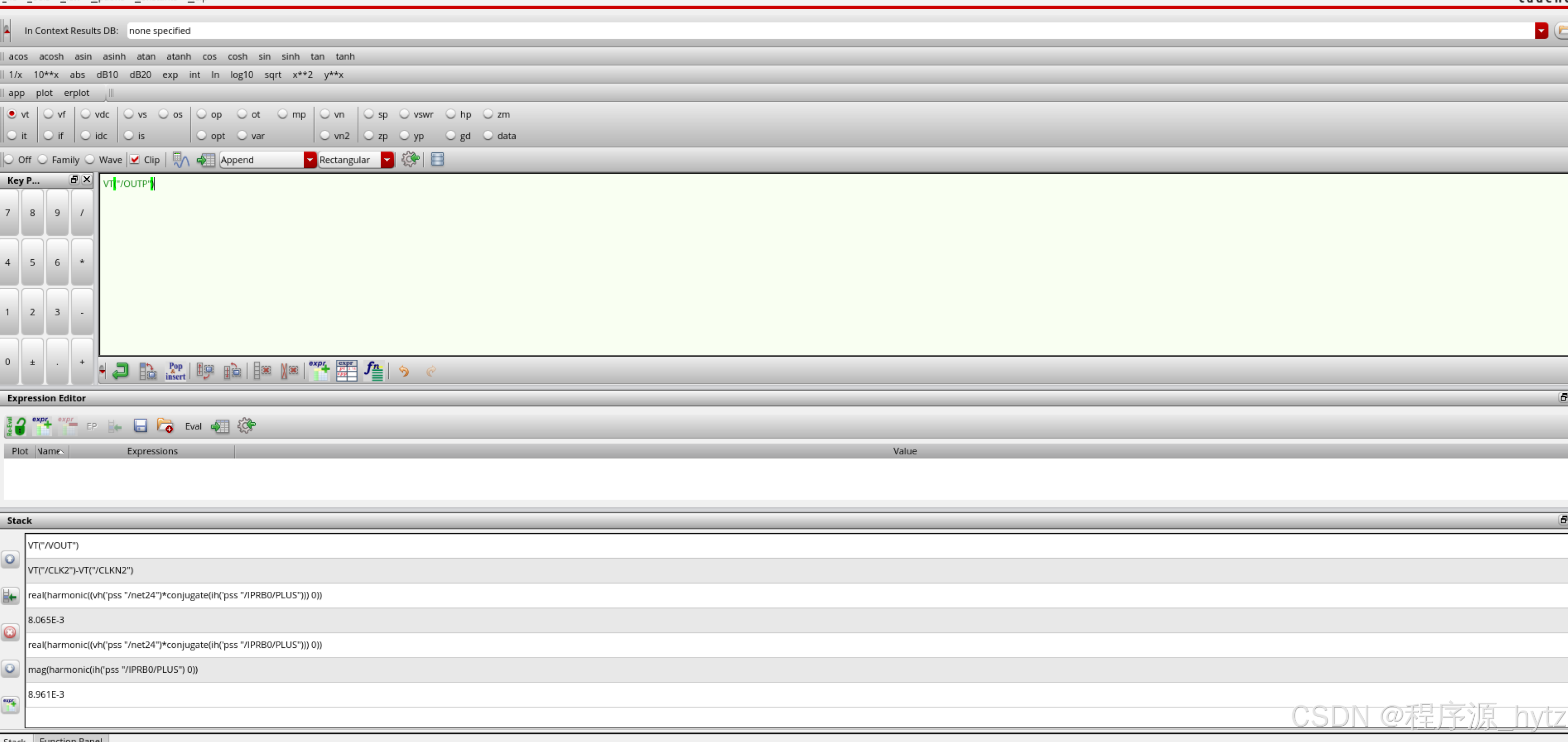

4、现在设置仿真的输出,即我们要查看哪些仿真数据。点击tools中的calculator,然后点左上角的Vt,它会跳转回原理图界面,这个时候我们点击一下输出端,,它会再跳转回calculator。

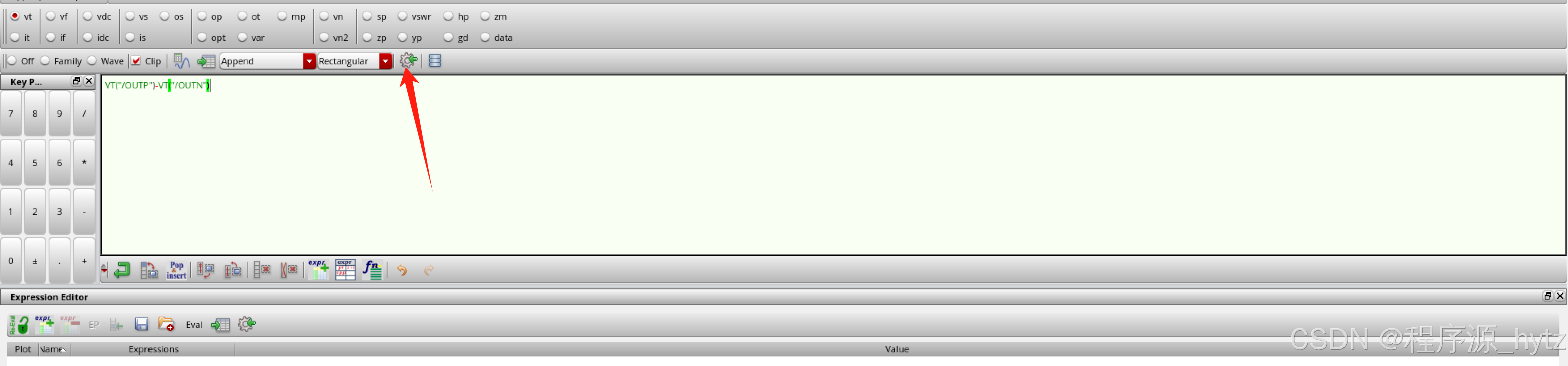

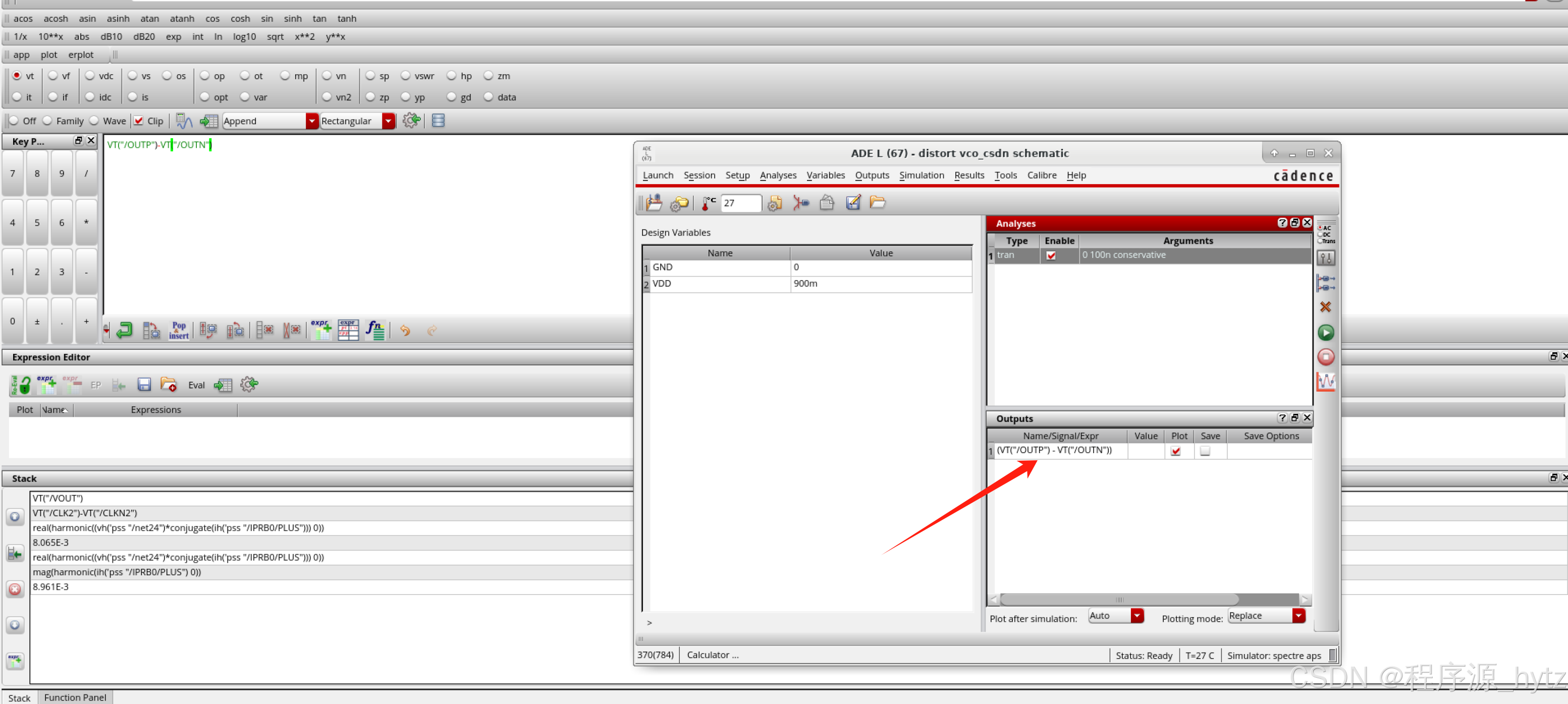

5、因为该VCO是交叉耦合结构,差分输出,所以对另一端的输出进行同样的操作。然后在calculator中点一下左侧的减号“-”,再点一下一个像轮子一样的东西,返回ADE L,你就会看到差分输出的表达式显示在OUTPUT栏。

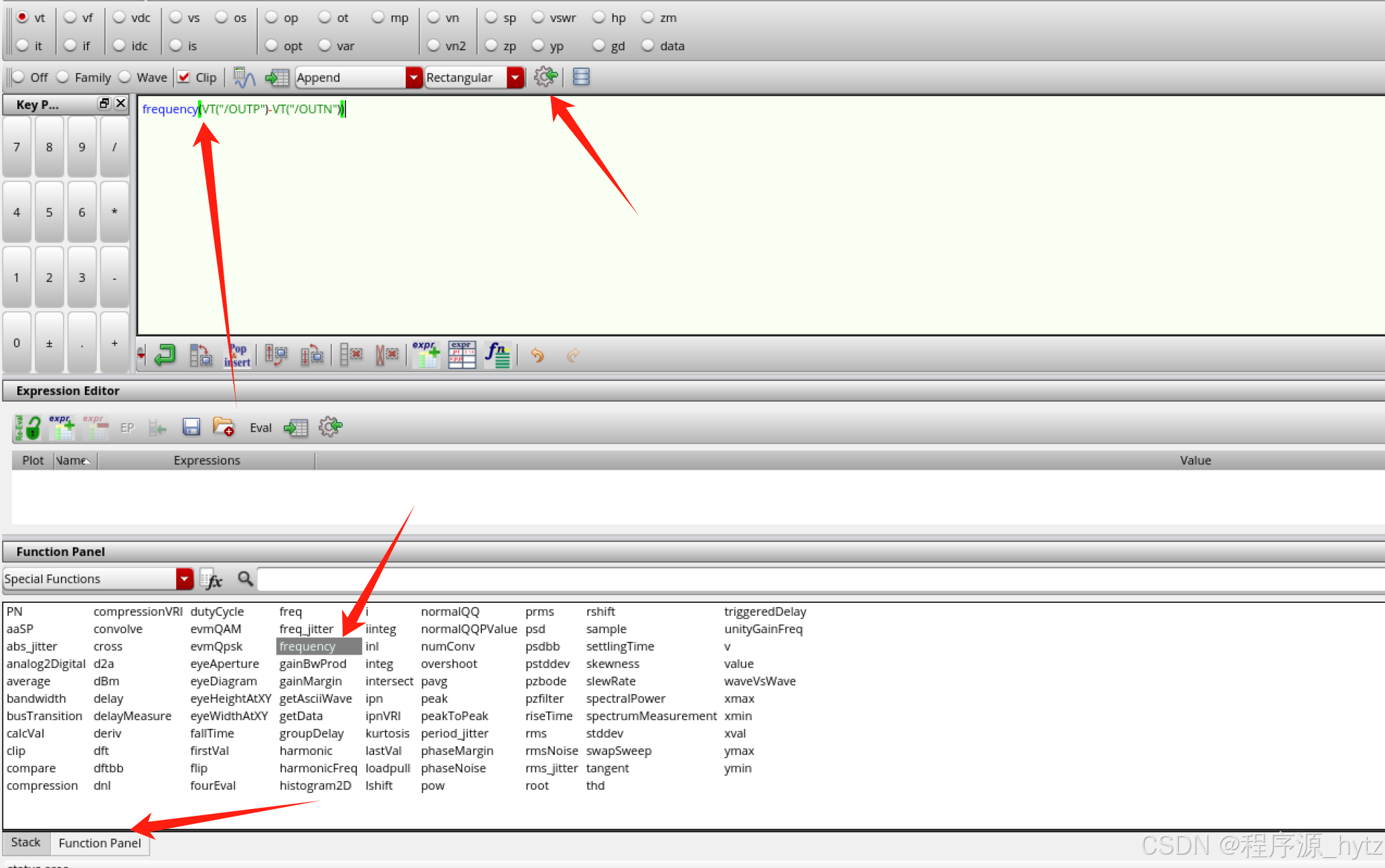

6、我们最基本的除了看时域输出波形,我们还得知道谐振频率。比较简单的方法是在calculator中点击左下角的“function panel”,然后点击里面的frequency。可以看到上面的输入栏已经在原来的基础上加上了“frequency”这个函数,再点一下轮子就会同样的在ADE L outputs中看到频率的表达式。

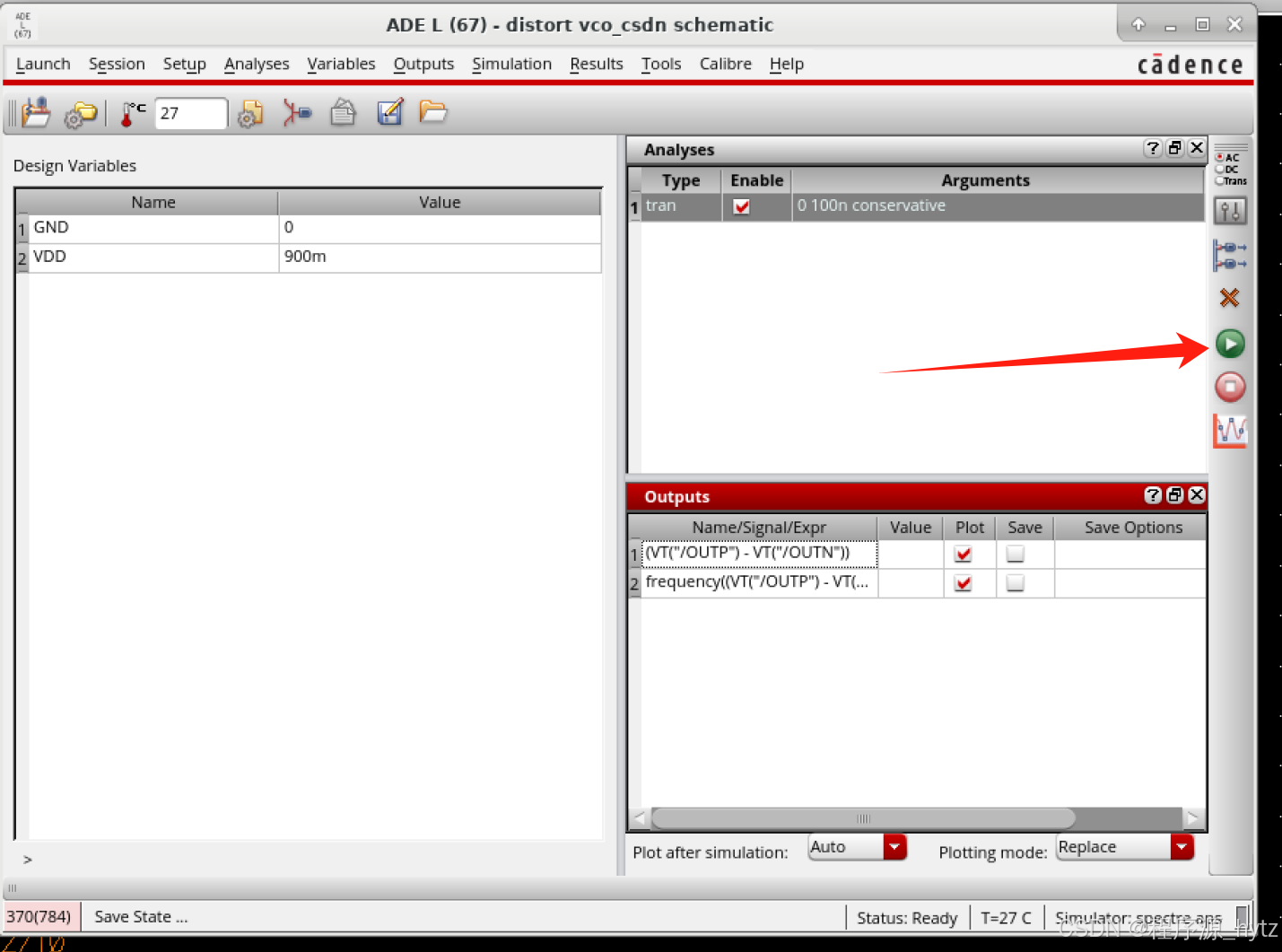

7、至此基本的设置已经完成,点击右侧的绿色箭头就可以运行仿真,查看结果。但是尝试之后发现出现各种问题,比如报错,或者没报错但是没有信号波形输出,只有直直的一条直流。常见的问题请见下一条帖子。