PCB 通孔是电容性的,但不一定是电容器

哼?……这是什么意思?……

多年来,流行的观点是 PCB 通孔本质上是电容性的,因此可以用集总电容器进行建模。虽然当信号的上升时间大于或等于过孔不连续性延迟的 3 倍时,这可能是正确的,但我将向您展示为什么不再适合这样思考;继续使用这种方法对高速通道进行建模甚至有风险。

让我们通过说 via 是具有过大寄生电容或电感的传输线来开始讨论。当过孔的阻抗等于连接到它们的传输线的特性阻抗时,它们被认为是透明的。在几乎所有情况下,通过多层 PCB 的通孔都是电容性的,因为通孔桶和反焊盘之间存在分布电容。因此,它们最终的阻抗低于连接到它们的走线。与任何其他传输线一样,当信号的上升沿遇到较低的阻抗时,它将在不连续性的长度上引起负反射。

回到正题,最好用图 1 中总结的示例来演示。考虑在长 50 欧姆传输线的远端有一个过孔。过孔有一个短的直通部分和一个长的短截线部分。通孔截面为 15 mils,短截线为 269 mils,总通孔长度为 284 mils。这对于现代背板设计来说并不罕见。

对于这种特定的过孔几何形状,阻抗为 33 欧姆,超出的过孔电容为 1.9pf。即使源极有 50ps 的快速上升时间,当信号到达远端的过孔时,上升时间也会因有损电介质引起的色散而降低。在此示例中,在 23 英寸之后,上升时间已降至大约 230ps。

如果过孔不连续性的总延迟 (TD) 为 60 ps,则过孔处的 230 ps 上升时间大于 3TD (180ps)。正如预期的那样,当使用等于过剩电容的集总电容器对过孔进行建模,并将其与传输线过孔模型进行比较时,使用 230ps 上升时间时,反射的 TDR 图几乎相同。

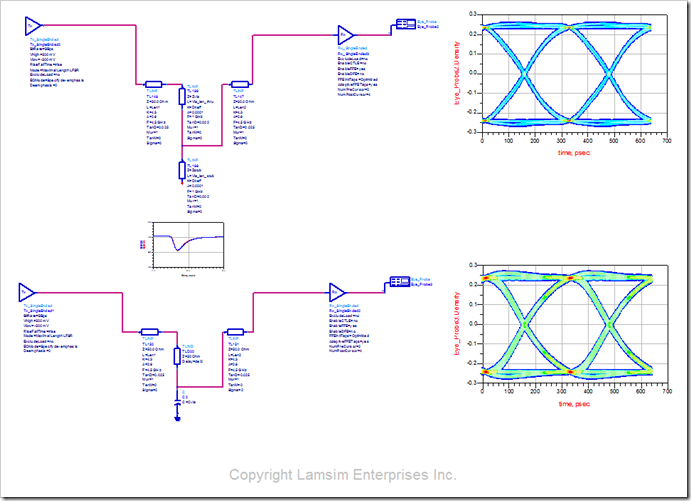

图 1:23 英寸后的 Via 型号 TDR 比较。顶部拓扑将 33 欧姆传输线用于过孔的直通和短截线部分。底部拓扑结构对过孔进行建模,其中一条 50 欧姆传输线表示直通部分的延迟,一个 1.9pf 电容器表示过剩的电容。使用 Agilent ADS 进行建模和仿真。

到目前为止一切都很好,对吧?嗯,也许是这样。了解的唯一方法是进一步探索此拓扑并比较眼图。假设您的电路需要以 3.125 GB/s 的 XAUI 速率工作。您可以通过添加驱动程序和接收器来修改这两个拓扑。仿真后,您最终会得到如图 2 所示的眼图。

图 2 3.125Gb/s 时的眼图比较。顶部拓扑将 33 欧姆传输线用于过孔的直通和短截线部分。底部拓扑结构对过孔进行建模,其中一条 50 欧姆传输线表示直通部分的延迟,一个 1.9pf 电容器表示过剩的电容。使用 Agilent ADS 进行建模和仿真。

还是好的。那么,你可能会问,你的意思是什么?

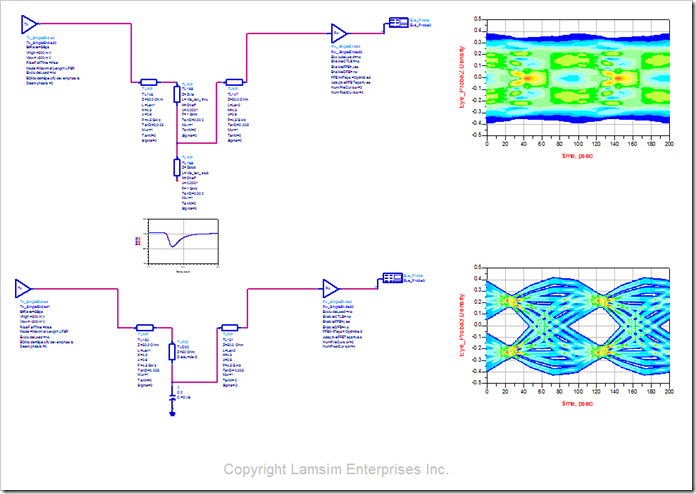

你说得对,你评论说有一个很好的反射匹配,眼睛睁得大大的。啊,但现在让我们假设你想在未来以 10GB/s 的速度运行它。因此,您需要调高发射器的比特率,并再次仿真两种拓扑。但这一次,您会得到一些意想不到的结果,如图 3 所示。

图 3 10Gb/s 时的眼图比较。顶部拓扑将 33 欧姆传输线用于过孔的直通和短截线部分。底部拓扑结构对过孔进行建模,其中一条 50 欧姆传输线表示直通部分的延迟,一个 1.9pf 电容器表示过剩的电容。使用 Agilent ADS 进行建模和仿真。

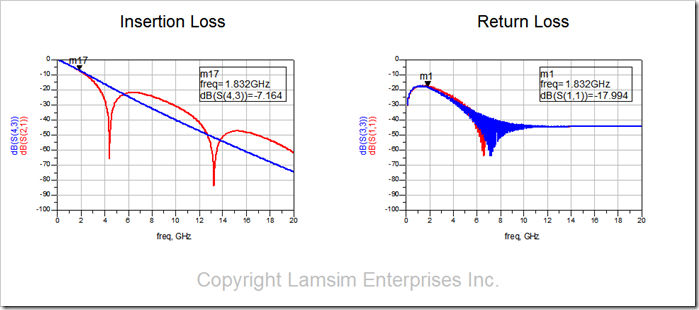

哎哟!这里发生了什么?查看 TDR,通道末端的反射看起来相同,那么为什么接收眼不匹配呢?要回答这个问题,我们真的需要看一下两个通道的 S 参数图。图 4 显示了两种拓扑的插入和回波损耗。红色是传输线模型,蓝色是电容器模型。

图 4 两种拓扑的插入和回波损耗。红色曲线是传输线过孔模型,蓝色曲线是电容器模型。

插入损耗图表示传输的输出功率与频率的关系,而回波损耗是反射功率与频率的关系。在时域中,插入损耗和回波损耗分别等效于 TDT 和 TDR 图。如您所见,Return loss 匹配得非常好;就像我们之前观察到的 TDR 图一样,但只有当我们查看插入损耗图时,图 3 眼图差异的真正原因才会很明显。

请注意,第一个谐振零点位于大约 4.5 GHz。这个 null 表示四分之一波谐振频率 fo,是由于长 269 mil 的过孔短截线。13.5GHz 的另一个零点是 fo 的 3 次谐波。短截线长度越长,谐振频率越低。当比特率的一半或接近一半时存在 null,则眼睛将受到破坏。在我们的示例中,4.5GHz 大约是 10GB/s 的一半,从图 3 中可以看出,结果眼图是完全闭合的。

但 S 参数告诉我们更多。我们可以使用它们来确认之前使用的经验法则,即信号的上升时间大于或等于通过过孔不连续性延迟的 3 倍。

如果您研究回波损耗图,您会发现高达 1.83GHz 的匹配非常出色。这是 capacitor 模型适合的有效带宽。换句话说,1.83GHz 的带宽意味着您可以使用等效的电容器模型作为比特率高达 3.6GB/s 的过孔。

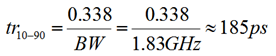

公式 1 通常用于将 3dB 带宽转换为等效的 10-90 上升时间。用 1.83 GHz 代替 3dB 带宽,上升时间约为 185 ps。

方程 1

当您将 185 ps 除以 3 时,最终得到大约 62ps,而通过我们最初确定的过孔的传播延迟约为 60ps。

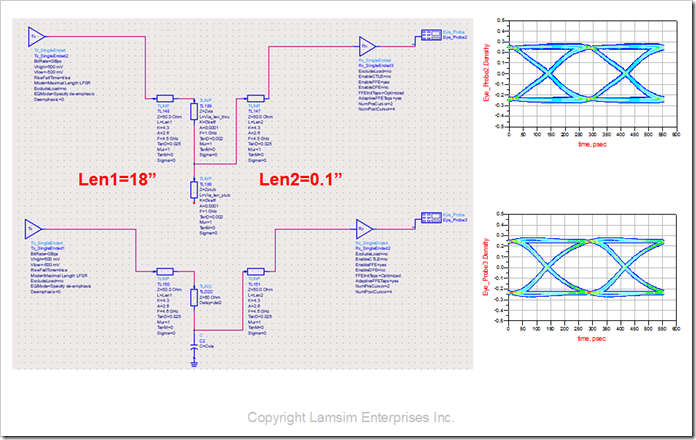

图 5 是传输线长度减少到 18 英寸以将上升时间缩短到 185 ps 的仿真摘要。如您所见,3.6 Gb/s 的传输线过孔模型眼图刚刚开始失真,而电容器模型仍然相对平滑;证实了我们的带宽经验法则。使用电容器作为超过此比特率的通孔模型将导致乐观的结果,并在您的 10 Gig 原型进入实验室时产生漫长的夜晚。

所以现在你明白我说的通孔是电容的,但不一定是电容器的意思了。

图 5 3.6Gb/s 时的眼图比较。顶部拓扑将 33 欧姆传输线用于过孔的直通和短截线部分。底部拓扑结构对过孔进行建模,其中一条 50 欧姆传输线表示直通部分的延迟,一个 1.9pf 电容器表示过剩的电容。使用 Agilent ADS 进行建模和仿真。