非接触式互连:当串扰是您的朋友时

在正常的 PCB 设计中,由于电磁耦合,串扰通常是两条或多条彼此靠近的走线的不良影响。在任何高速设计中,我们通常将其视为我们的敌人,并竭尽全力避免它。那么,你可能会问,相声怎么能成为你的朋友呢?

为了回答这个问题,我想先带您回到 1994 年的秋天。这是跨背板运行高达 33 MHz 的宽并行总线的时代。正如我们今天所知道和喜爱的那样,高速串行、点对点接口和 serdes 技术在一些聪明的年轻工程师眼中只是一闪而过。

Nortel(当时又名 Northern Telecom)正在寻求更换 DMS Supernode 平台的计算模块机架,因为预计几年后它将耗尽动力。为了解决这个问题,系统架构师决定需要一个可扩展的、多处理的、共享内存的计算架构来取代它。

我的工作是开发一个概念,将所有这些卡打包在一个架子上,然后设计一个背板来互连所有东西。很快就发现,单个共享总线无法支持多处理所需的带宽。多条并行总线也无法解决问题,因为缺乏所有 I/O 所需的高密度背板连接器技术。即使我们有一个合适的连接器,并且它可以神奇地安装在卡槽的范围内,那么背板的层数也会呈指数级增长。

不,还需要其他东西。幸运的是,我当时工作的北电的研发实验室贝尔北方研究公司(BNR)有一个先进的技术团队,他们喜欢在沙子里玩耍。我记得有一天我去参加一个会议,看到一些关于他们正在使用的一些巧妙技术的演示。

他们所做的一个演示是关于一种独特的非接触式互连技术。我立即看到了技术为我们的架构提供的实际应用,它立即成为了我的朋友。它使我们能够最终发明一种获得专利的专有点对多点互连解决方案,每对运行速度为 1GB/s [1]。

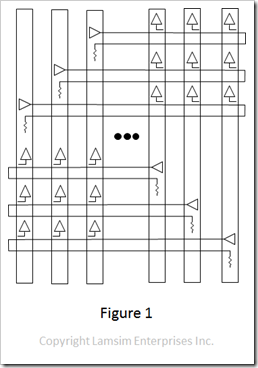

非接触式技术实际上依赖于受控的电磁耦合,或者简单的串扰。参见图 1。在这个简单的高级框图中,机架上的每张卡都会通过背板以差分方式传输数据。当差分对穿过卡槽的连接器区域时,发射信号被边沿耦合到相邻的小走线,长约 3/4 英寸,连接到相应的接收器引脚。在最后一个卡插槽之后,传输差分对交换层,在那里它们返回原始卡并被终止。

这种架构的美妙之处在于,每张卡只需要一组发射器即可将其数据广播到所有其他卡。由于每张卡都有足够的接收器来侦听其他卡,因此点对多点互连实现了相当于多点对多点架构;但没有额外引脚和 PCB 层的开销。此外,使用简单、廉价的 1 毫米连接器实现了 2GB/s 的有效线速;与紧凑型 PCI 标准选择的相同。

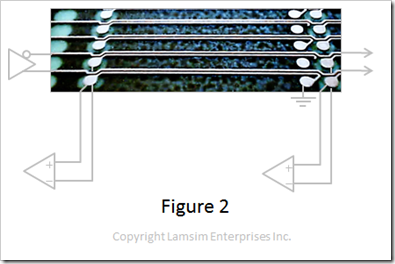

图 2 是层压和钻孔前背板的内层双面芯的照片。它更详细地显示了耦合器。圆形焊盘用于连接器过孔,用于将耦合器走线连接到连接器引脚。左侧的焊盘行用于一个卡槽,而右侧的焊盘行用于另一个卡槽。

如果我们查看从左下角进入图片的两条跟踪,我们可以看到它们是如何通过 connector 字段路由的。这两条走线是差分对的一部分,其中每条走线都作为单端走线布线,即彼此之间没有耦合。当这些走线接近第一排焊盘时,它们会向下点动到最小间距,以确保与连接到焊盘的耦合器走线紧密耦合。紧密的间距继续确保与下一组焊盘的最大耦合,其中 pattern 在右下角再次出现星形。此模式在每个差分对的照片中一直重复。

您可能会敏锐地注意到,底部的耦合器走线在每一端都连接到焊盘,而它上面的配对耦合器则没有。当两条共面并行走线彼此靠近时,会产生两种类型的串扰;向后或近端串扰 (NEXT);以及前向或远端串扰 (FEXT)。

随着传输信号在照片中从左到右传播,信号的上升沿在耦合长度的开头启动 NEXT。NEXT 电压在等于上升时间除以传播延迟的两倍的临界长度后饱和;其中 RiseTime 以秒为单位,propagation delay 以每单位长度的秒为单位。它保持饱和的时间是耦合长度时间延迟的两倍。由于差分信号,相应耦合器上的 NEXT 电压是相反的相位。

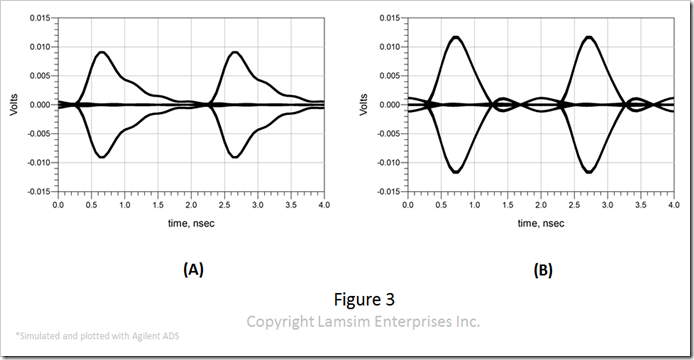

在 coupler pin处,存在由 via 引起的反射。由于远端的耦合器在特性阻抗中未端接,并且保持开路状态,因此由于耦合器通过反射回接收器的任何二次反射,同样具有相反的相位。当两个反射回到接收器时,它们将相加,并为眼睛增加额外的噪声,从而产生符号间干扰,如图 3(A) 中的肩部所示。通过保持一端开路,并将另一端短接到地,意味着任何次级噪声将具有相同的相位,当它们到达接收器时,它们将抵消,从而消除码间干扰并增加眼图幅度,如图 3(B) 所示。

您会注意到,眼图波形与我们习惯看到的传统眼图不同。相反,当耦合长度与 bit time 相比较短时,我们观察到典型的 NEXT 眼图。中间也有一条线。

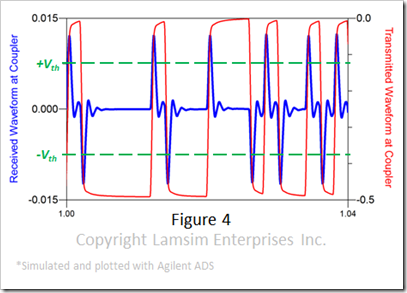

图 4 可以帮助解释原因。蓝色波形是响应红色传输波形的 NEXT 电压,位于耦合器的近端。请注意,在传输波形的边缘转换处只有脉冲。上升沿产生正脉冲,下降沿产生负脉冲。每个脉冲的持续时间是耦合器长度时间延迟的两倍。

接收器使用简单的峰值检测器和锁存器将信号重新生成回原始波形。正峰值检测器检测到正向脉冲。当它超过正电压阈值 (+Vth) 时,它将锁存输出设置为逻辑高电平。输出保持高电平,直到负脉冲超过负峰值检测器的负阈值 (-Vth),并将锁存器复位至逻辑低电平。

这就是 crosstalk 如何成为您的朋友!当然,小耦合串扰信号意味着我们必须防止来自板载其他数字信号的 CROSSTALK。但这不是 mixed signal layout design rules 无法解决的问题。……等一会!……我们都是同一个敌人?……..谁会想到一句古老的谚语,“我的敌人的敌人就是我的朋友”[原文如此],在这里也适用呢?