缺乏经验的 PCB 过孔建模方法

您是一名背板设计人员,被指派设计一种新的高速、多千兆位串行链路架构,从多个线卡到背板上的多个交换矩阵交换卡。这些链路必须在第一天以 6GB/s 的速度运行,并且为 10GB/s (IEEE 802.3KR) 做好产品演进的准备。时间表很紧,您需要提出一个背板架构,以允许程序的其余部分按计划进行。

你想出了一个你认为可行的概念,但背板很厚,有 30 多层。卡槽之间有一些超过 30 英寸的长痕迹和一些小于 2 英寸的短痕迹。重复使用您在上次设计中使用的相同连接器的压力很大,但您的直觉告诉您,它的设计可能不足以适合这种高速应用。

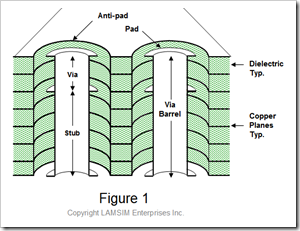

最后,您担心用于背板连接器的差分过孔封装的大小和设计,因为您知道它们可能会对接收信号的质量造成破坏。您希望通过 connector field 最大化 routing 通道,这需要您缩小反焊盘尺寸,以便布线将被参考平面覆盖,但您无法轻易量化这样做对 via 的影响。

根据经验,您已经尽了所有能想到的办法,在不进行仿真的情况下使过孔尽可能透明。去除内层上的无功能焊盘,并计划通过短线对连接器进行背钻会有所帮助,但这足够吗?您心里知道,回答这些问题并帮助您入睡的最佳方法是输入数字。

因此,您决定对通道进行建模和仿真。但要做到这一点,你需要精确的过孔模型来插入你最喜欢的电路仿真器。但是你怎么得到这些呢?你以前都听说过;“对于高速,对 Via 进行建模的最佳方法是使用 3D 电磁场求解器”。虽然这可能是真的,但如果您无法使用这样的工具,因为成本超过您的公司愿意花费,或者因为您没有专业知识或时间来学习如何构建可以信任的模型来及时做出决策,该怎么办?

最重要的是,3D 场求解器通常会生成 S 参数行为模型。由于它们仅代表给定结构的一个样本,因此无法使用单个行为模型执行假设、最坏情况、最小/最大分析。因此,需要对模型进行多次迭代;导致进一步延迟获得您的答案。

另一方面,电路模型是实际设备的原理图表示。对于任何物理结构,都可以有多个电路模型来描述它。所有这些都可以提供相同的性能,最高可达一定的带宽。在电路仿真器中运行时,它可以预测结构的可测量性能。这些模型可以参数化,以便快速探索最坏情况分析。

电路模型的问题在于,您通常需要一个行为模型来校准它,或者需要使用解析方程来估计参数。但是,正如我的朋友 Eric Bogatin 经常说的那样,“现在是一个不错的答案!总比迟到的好答案好”。

过去,如果没有行为模型来校准差分通孔结构,几乎不可能开发差分通孔结构的电路模型。这些行为模型是通过经验公式、测量数据或使用 3D 电磁场求解器开发的。

现在,还有另一种方法。我给它起了个绰号,“缺乏经验的 PCB过孔建模方法”。以下是它的工作原理。

差分过孔结构剖析: