7系列 之 SelectIO 资源

背景

《ug471_7Series_SelectIO.pdf》介绍了Xilinx 7 系列 SelectIO 的输入/输出特性及逻辑资源的相关内容。

第 1 章《SelectIO Resources》介绍了输出驱动器和输入接收器的电气特性,并通过大量实例解析了各类标准接口的实现。

第 2 章《SelectIO Logic Resources》介绍了输入输出数据寄存器及其双倍数据速率(DDR)操作,以及可编程输入延(IDELAY)和可编程输出延迟(ODELAY)。

第 3 章《Advanced SelectIO Logic Resources》介绍了ISERDESE2 、OSERDESE2与IO_FIFO。

了解了这个手册充分介绍的SelectIO架构和资源,以及所支持的电平标准。就可以利用相应的架构和资源实现与不同电平标准、通信速率间的外设建立起联系。

系列目录与传送门

- 基于Xilinx的7系列,

- 笔者学习、研究FPGA的过程、笔记,记录为:《凡人修FPGA传》。

说明1:本系列基于文档文档《ug471_7Series_SelectIO.pdf》而写,翻译和感悟,会出现中英文混合的情况。

说明2:虽然文中会出现一些原文的部分截图,非常支持并推荐大家去看原汁原味的官方文档

说明3:在查阅相关资料过程中,发现一些关于相关知识点的介绍零零散散,本系列会对其进行整合,力求详尽。

说明4:本博客是笔者用来记录学习过程的一个形式,并非专业论文。因此,在本博客中不会太注重图文格式的规范。

说明5:如果文章有误,欢迎诸位道友指出、讨论,笔者也会积极改正,希望大家一起进步!

文章目录

- 背景

- 系列目录与传送门

- 前言

- 1、I/O Bank

- 1.1 ··· I/O Bank是什么?

- 1.2 ··· 7系列中的I/O Bank

- 2、SelectIO 资源

- 2.1 ··· 资源介绍

- 2.2 ··· I/O Bank 规则

- 2.3 ··· SelectIO 引脚的供电电压

- 3、7系列FPGA的 DCI技术 与 IN_TERM约束

- 3.1 ··· 7 Series FPGA DCI—Only available in the HP I/O banks

- 3.2 ··· Uncalibrated Split Termination in High-Range I/O Banks (IN_TERM)

- 4、7系列 FPGA 的 SelectIO 属性与约束

- 4.1 ··· DCI_CASCADE 约束

- 4.2 ··· Location 约束

- 4.3 ··· IOSTANDARD 属性

- 4.4 ··· IBUF_LOW_PWR 属性

- 4.5 ··· Output Slew Rate 属性

- 4.6 ··· Output Drive Strength 属性

- 4.7 ··· IBUF, OBUFT, and IOBUF 的 PULLUP/PULLDOWN/KEEPER 属性

- 4.8 ··· Differential Termination 属性

- 4.9 ··· Internal Vref

- 4.10 ··· VCCAUX_IO 约束

- 5、同一Bank中的 I/O Standards 组合规则

- 6、参考文献

前言

本文对应的是《ug471_7Series_SelectIO.pdf》的第 1 章 < SelectIO Resources > 部分,是对7系列FPGA的所带有的逻辑资源的一个概述与介绍。

1、I/O Bank

1.1 ··· I/O Bank是什么?

在 Xilinx 的 FPGA 中,Bank 是芯片内部边缘划分的物理区域,是一堆有相同特性的 IO的合集,是一组物理上相邻、功能上相关的 I/O 引脚及其配套资源(如时钟、电源、阻抗匹配等)的集合,也是 FPGA 芯片内部管理 I/O 功能的基本单元。

I/O banks are collections of I/O blocks (IOBs), with configurable SelectIO™ drivers and receivers, supporting a wide variety of standard interfaces, both single-ended and differential.

同一Bank内所有I/O引脚共用相同的供电电压,不同Bank可配置不同电压标准。

每个Bank包含专用资源,如:时钟网络资源有BUFG(全局时钟缓冲器)和BUFR(区域时钟缓冲器),专用接口资源有DCI(数字控制阻抗)和ODT(片上终端电阻)。

1.2 ··· 7系列中的I/O Bank

7系列FPGA中有高性能(high-performance,HP)和高范围(high-range,HR)两类I/O Bank。

注意:HR I/O bank 不支持 DCI。

HP I/O Bank 旨在满足高速存储器和其他芯片间接口的性能要求,其电压最高可达 1.8V。HR I/O bank 则旨在支持更广泛的 I/O 标准,电压最高可达 3.3V。

在逛CSDN时,看到这么一个说法,如以下截图所示,供诸位道友参考。

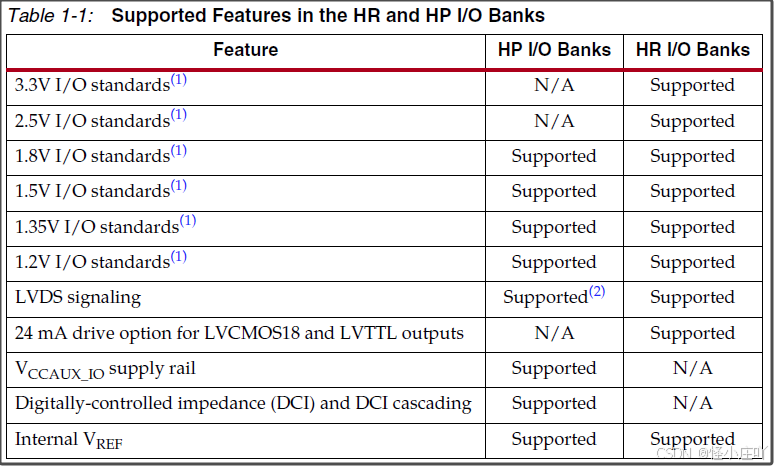

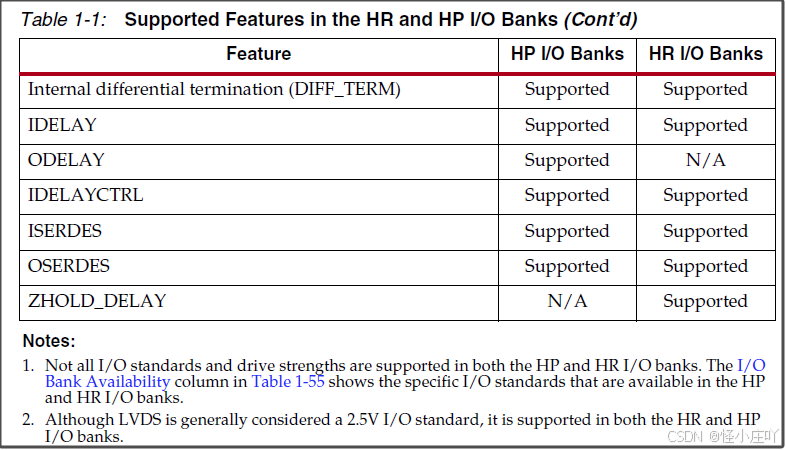

表1-1,突出显示了 HP 和 HR I/O bank 所支持的特性。7 系列 FPGA 包含 HR 和 HP I/O bank 的不同组合。

2、SelectIO 资源

2.1 ··· 资源介绍

“All 7 series FPGAs have configurable SelectIO drivers and receivers, supporting a wide variety of standard interfaces. The robust feature set includes programmable control of output strength and slew rate, on-chip termination using digitally-controlled impedance (DCI), and the ability to internally generate a reference voltage (INTERNAL_VREF).”

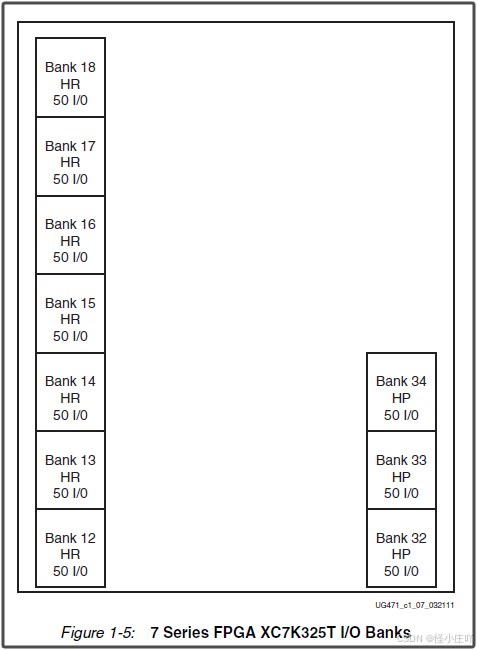

除少数例外,每个 I/O Bank 包含 50 个 SelectIO 引脚。

每个 Bank 两端的两个引脚仅能用于单端 I/O 标准(single-ended I/O standards)。在大多数器件中,single-ended (only) IOBs 是每个 I/O bank 两端的两个引脚。其余 48 个引脚既可以用于单端标准,也可以通过将两个 SelectIO 引脚组合成正 / 负(P/N)对的方式用于差分标准。

每个 SelectIO 资源都包含输入、输出和三态驱动器。

SelectIO 引脚可以配置为各种 I/O 标准,包括单端和差分 I/O 标准。

• 单端 I/O 标准(例如,LVCMOS、LVTTL、HSTL、PCI 和 SSTL)

• 差分 I/O 标准(例如,LVDS、Mini_LVDS、RSDS、PPDS、BLVDS 以及差分 HSTL 和 SSTL)

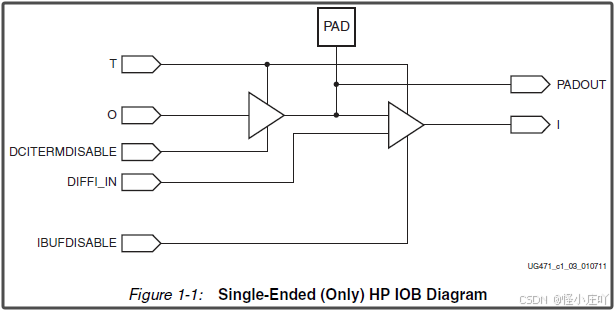

图 1-1 ,为 single-ended (only) HP I/O block (IOB) 框图。

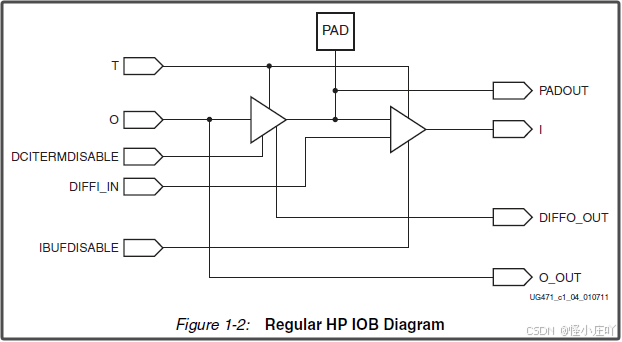

图 1-2 ,为 regular HP IOB 框图。

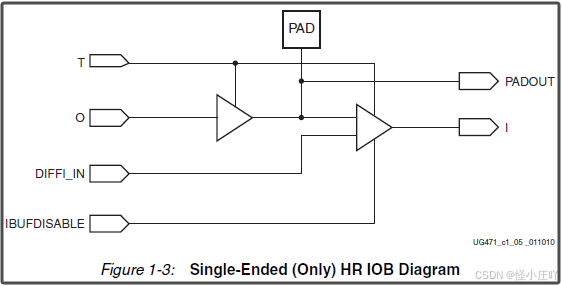

图 1-3 , single-ended (only) HR IOB 框图。

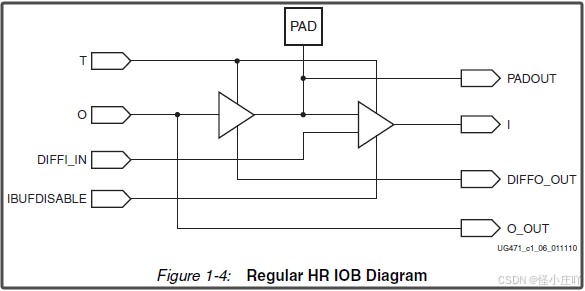

图 1-4 ,为 regular HR IOB 框图。

在 HP 和 HR I/O bank 中,the single-ended (only) 和 regular IOBs 基本等同,区别在于 single-ended (only) IOBs 没有用于差分输出信号的连接。

HP bank多一个可以控制数控阻抗(DCI)的信号DCITERMDISABLE,其余结构都一样。其中PAD是FPGA的金属管脚,该管脚可作为输入也可作为输出,通过I、O信号实现单端输入、输出,DIFF_IN和IDFFO_OUT实现差分输入、输出,但是差分信号需要两个管脚进行配合实现。(《GMII转RGMII(一)IOB相关原语介绍》)

每个 IOB 都直接连接到一个 ILOGIC/OLOGIC 对,该对包含用于数据的输入和输出逻辑资源、 IOB的三态控制。

2.2 ··· I/O Bank 规则

在 7 系列器件中,一个 I/O BANK 由 50 个 IOB 组成。BANK 的数量取决于器件的大小和封装引脚分布。

图1-5 是一个柱状布局示例,展示了 XC7K325T 的 I/O BANK。

正如上图1-5所示,一共10个BANK,7个HR,3个HP。并不是每个系列FPGA都会有HP,例如A7200T也有10个BANK,但只有9个BANK有IO,且均为HR。

正如上图1-5所示,一共10个BANK,7个HR,3个HP。并不是每个系列FPGA都会有HP,例如A7200T也有10个BANK,但只有9个BANK有IO,且均为HR。

2.3 ··· SelectIO 引脚的供电电压

- Vcco

Vcco 电源是 7 系列 I/O 电路的主要电源。

对于给定的 I/O bank,所有 Vcco 引脚必须连接到电路板上的同一外部电压源。因此,给定 I/O bank内的所有 I/O 必须共用相同的 Vcco 电平。

Vcco 电压必须符合 I/O 标准分配给该 I/O bank的要求。不正确的 Vcco 电压可能导致功能丧失或损坏器件。

在 HP I/O bank中,如果 I/O 标准的电压要求小于 1.8V,但施加的 Vcco 大于 2.5V,器件会自动进入过压保护模式。使用正确的 Vcco 电平重新配置器件可恢复正常运行。

- Vref

带有差分输入缓冲器的 single-ended I/O 标准需要一个输入参考电压(reference voltage,Vref)。当 I/O bank内需要 Vref 时,该bank的两个多功能 Vref 引脚必须用作 Vref 电源输入。

7 系列 FPGA 可以通过启用 INTERNAL_VREF 约束,选择使用内部生成的参考电压。

- Vccaux

全局辅助电源(global auxiliary supply rail,Vccaux),主要用于为 7 系列 FPGA 内部各种模块的互连逻辑供电。

在 I/O bank中,Vccaux 还用于为某些 I/O 标准的输入缓冲电路供电。这些标准包括所有 1.8V 及以下的单端 I/O 标准,以及一些 2.5V 标准(仅适用于 HR I/O 组)。

此外,Vccaux轨为用于差分和 Vref I/O 标准的 bank内差分输入缓冲电路供电。

- Vccaux_io

辅助 I/O 电源(auxiliary I/O supply rail,Vccaux_io)仅存在于 HP I/O BANK 中,为 I/O 电路供电。

对于 LVDS 接口,Vccaux_io 使用哪种电压电平供电无关紧要。默认的 1.8V 电压可降低功耗,并且在 I/O 方面提供几乎相同的性能。当单端驱动器支持的最快比特率需要略微提高性能时,可以选择 2.0V。

对于 I/O 网络和原语,有一个名为 VCCAUX_IO 的设计约束,如果要将任何 BANK 的 Vccaux_io 引脚设置为 2.0V,则应在设计中指定该约束。

在 Kintex-7 和 Virtex-7 器件封装中,Vccaux_io 引脚以三到四个 HP I/O BANK为一组进行内部连接。

同一 Vccaux_io组中的所有 I/O 引脚,其网络或原语上的 VCCAUX_IO 约束必须兼容。分组连接在一起的所有 Vccaux_io引脚应连接到电路板上的同一电压。Kintex-7 器件的 FBG 封装包含 Vccaux_io 引脚,但内部是不连接的。这些封装中的所有 HP I/O BANK 改为由主 Vccaux轨供电。

3、7系列FPGA的 DCI技术 与 IN_TERM约束

3.1 ··· 7 Series FPGA DCI—Only available in the HP I/O banks

关于这部分,详见笔者的另一篇博客《7 Series FPGA DCI—Only available in the HP I/O banks》。

注意:正如标题所写:7 Series FPGA DCI—Only available in the HP I/O banks。

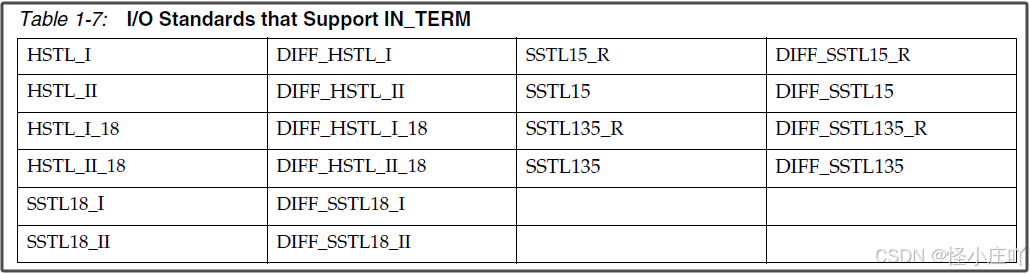

3.2 ··· Uncalibrated Split Termination in High-Range I/O Banks (IN_TERM)

HR I/O bank 有一个可选的片上分离终端特性,该特性与 HP I/O banks 中的 三态分离终端DCI 特性极为相似。

和 HP bank 中的三态分离终端 DCI 一样,HR bank 使用 两个阻值为目标阻值两倍的内部电阻 构建了一个戴维南等效电路。其中,一个电阻连接到 Vcco,另一个连接到地,从而为中点 Vcco/2 提供了一个戴维南等效终端电路。在输入端,终端始终存在;在双向引脚上,只要输出缓冲器处于 三态,该终端就存在。

然而,这个 Uncalibrated Split Termination选项 与 3-state split-termination DCI 之间存在一个重要区别:使用 DCI 时,会针对 VRN 和 VRP 引脚上的外部参考电阻进行校准,而此特性采用的是内部电阻,且没有校准程序来补偿温度、工艺或电压的变化。该选项的目标戴维南等效电阻值为 40Ω、50Ω 和 60Ω。

与 DCI termination 的另一个不同之处在于,在设计中启用这个 uncalibrated termination 的方式有所不同。在 HP I/O banks中,通过为 I/O 引脚分配 T_DCI I/O 标准来启用 3-state split-termination DCI 选项;而在 HR I/O banks 中,通过为 I/O 引脚网络分配 IN_TERM 约束来启用uncalibrated split-termination 选项。这可以通过多种方式来实现,包括在源硬件描述语言(HDL)设计中、在用户约束文件(UCF)、网络约束文件(NCF)或 Xilinx 约束文件(XCF)中,或者在 PlanAhead™软件中进行设置。

在 HR banks 中,IN_TERM 约束可以设置为 NONE(默认值)、UNTUNED_SPLIT_40、UNTUNED_SPLIT_50 或 UNTUNED_SPLIT_60。UCF 语法的一个示例如下:

NET "pad_net_name"IN_TERM = "UNTUNED_SPLIT_50";

4、7系列 FPGA 的 SelectIO 属性与约束

通过与某些 7 系列 FPGA I/O 资源功能相关联的属性 / 约束,可实现对这些功能的配置(例如位置约束、输入延迟、输出驱动强度和转换速率)。

4.1 ··· DCI_CASCADE 约束

DCI_CASCADE 约束用于标识 DCI 级联时 master bank 及其对应的 slave banks。

在 UCF 文件中,DCI_CASCADE 属性采用以下语法:

CONFIG DCI_CASCADE = “ …”;

例如:

CONFIG DCI_CASCADE = “11 13 15 17”;

4.2 ··· Location 约束

位置约束(LOC)必须用于指定被实例化的 I/O 原语的 I/O 位置;说白了,就是指定引脚位置。位置约束的可能取值为所有外部端口标识符(例如,A8、M5、AM6 等)。这些取值取决于器件和封装尺寸。

在 UCF 文件中,LOC 属性采用以下语法:

INST <I/O缓冲器实例化名称> LOC = “<EXTERNAL_PORT_IDENTIFIER>”;

例如:

INST MY_IO LOC=R7;

4.3 ··· IOSTANDARD 属性

IOSTANDARD 属性可用于为所有 I/O 缓冲器选择 I/O 标准的值。

IOSTANDARD 属性在 UCF 文件中采用以下语法:

INST <I/O缓冲器实例化名称> IOSTANDARD=””;

单端 I/O 的 IOSTANDARD 默认值为 LVCMOS18,差分 I/O 的默认值为 DIFF_HSTL_II_18。

4.4 ··· IBUF_LOW_PWR 属性

IBUF_LOW_PWR 属性适用于以下输入场景:

• 1、所有具有差分输入的 I/O 标准,包括:

LVDS、LVDS_25、PPDS_25、RSDS_25、MINI_LVDS_25、BLVDS_25、DIFF_HSTL(所有变体)、DIFF_SSTL(所有变体)、DIFF_MOBILE_DDR、DIFF_HSUL(所有变体)

• 2、所有基于 Vref 的输入(如 HSLVDCI、SSTL、HSTL 和 HSUL)

• 3、所有输入和双向原语

IBUF_LOW_PWR 属性允许在性能与功耗之间进行可选权衡。性能变化体现在输入缓冲器的延迟中,可通过该设计的静态时序报告进行测量;功耗变化可使用 XPower Estimator(XPE)或 XPower Analyzer(XPA)工具进行估算。

该属性默认设置为 TRUE,即采用低功耗模式而非高性能模式实现输入缓冲器。IBUF_LOW_PWR 属性应用于 I/O 缓冲器实例,在 UCF 文件中采用以下语法:

INST <I/O缓冲器实例化名称> IBUF_LOW_PWR = [ TRUE | FALSE ];

4.5 ··· Output Slew Rate 属性

“slew rate”是压摆率,指信号从低电平到高电平或高电平到低电平的变化速率,影响信号的边沿陡峭程度和可能的电磁干扰。

多种属性值提供了为 I/O 输出缓冲器选择所需压摆率的选项。对于 LVCMOS、LVTTL、SSTL、HSTL、MOBILE_DDR 和 HSUL 输出缓冲器,包括差分版本,可通过 SLEW 属性指定所需的转换速率。

对于高频内存接口等高性能应用,指定 FAST slew rate 可能至关重要。然而,若设计不当(如终端匹配、传输线阻抗连续性和交叉耦合问题未处理),更快的转换速率也可能导致信号反射或噪声加剧。

SLEW 属性的允许值为:

• SLEW = SLOW(默认值)

• SLEW = FAST

SLEW 属性在 UCF 文件中采用以下语法:

INST <I/O缓冲器实例化名称> SLEW = “<SLEW_VALUE>”;

默认情况下,每个输出缓冲器的压摆率设置为 SLOW。此默认设置用于在切换非关键信号时将电源总线的瞬变最小化。

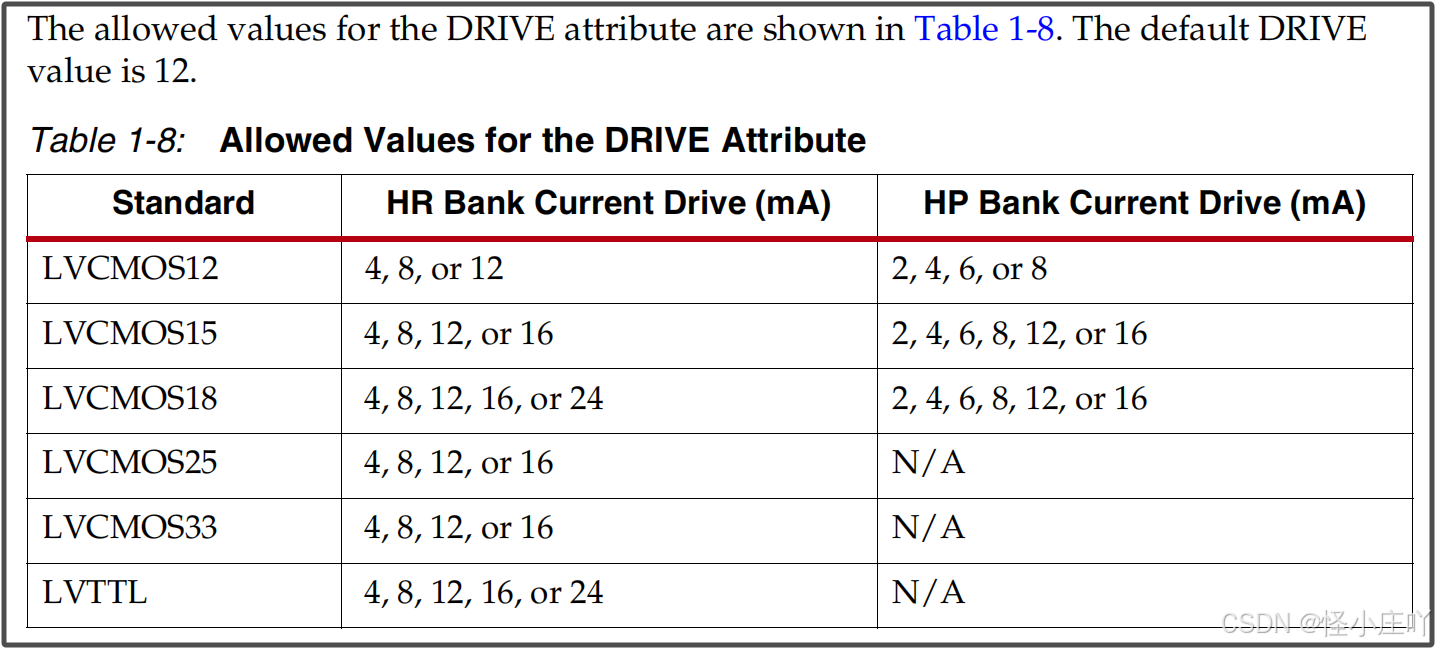

4.6 ··· Output Drive Strength 属性

对于 LVCMOS 和 LVTTL 输出缓冲器(OBUF、OBUFT 和 IOBUF),可通过 DRIVE 属性指定所需的驱动强度(drive strength),单位为 mA。

DRIVE 属性在 UCF 文件中采用以下语法:

INST <I/O缓冲器实例化名称> DRIVE = “<DRIVE_VALUE>”;

4.7 ··· IBUF, OBUFT, and IOBUF 的 PULLUP/PULLDOWN/KEEPER 属性

输入缓冲器(如 IBUF)、三态输出缓冲器(如 OBUFT)和双向缓冲器(如 IOBUF)可以配备弱(weak)上拉电阻、弱下拉电阻或弱 “保持(keeper)” 电路。

通过在缓冲器的相关网络中添加以下可能的约束值,即可启用此功能:

• PULLUP(上拉)

• PULLDOWN(下拉)

• KEEPER(保持)

可使用BITSTREAM.CONFIG.UNUSEDPIN属性为未使用的 I/O 全局设置逻辑电平。

4.8 ··· Differential Termination 属性

当被用作输入时,差分终端(DIFF_TERM)属性支持差分 I/O 标准。它用于开启或关闭内置的 100Ω 差分终端。7 系列器件中的片上输入差分终端相较于使用分离电阻(discrete resistor)具有显著优势,它能完全消除接收端的stub,从而极大地提升信号完整性。

此外,它还具有以下特点:

• 与 DCI 终端相比,功耗更低。

• 不使用 VRP/VRN 引脚(DCI 相关引脚)。

此属性可应用于以下 I/O 标准的输入引脚:

LVDS、LVDS_25、MINI_LVDS_25、PPDS_25、RSDS_25

对于 LVDS,I/O 组的 Vcco 必须连接到 1.8V;对于其他差分 I/O 标准,Vcco 必须连接到 2.5V,以提供 100Ω 的有效差分终端。DIFF_TERM 仅适用于输入,且只能在合适的 Vcco 电压下使用。

DIFF_TERM 属性可以在 UCF 约束文件中指定,也可以通过在实例化的 IBUFDS、IBUFGDS、IBUFDS_DIFF_OUT 或 IOBUFDS_DIFF_OUT 原语的通用映射(VHDL)或内联参数(Verilog)中设置相应值来指定。

DIFF_TERM 属性的允许值为:

• DIFF_TERM = TRUE

• DIFF_TERM = FALSE(默认值)

DIFF_TERM 属性在 UCF 文件中使用以下语法:

INST <I/O_BUFFER_INSTANTIATION_NAME> DIFF_TERM = “[TRUE|FALSE]”;

4.9 ··· Internal Vref

7系列FPGA可以(可选)在内部生成I/O bank的 Vref 。内部生成无需在印刷电路板(PCB)上提供特定的 Vref 电源,并释放特定I/O bank中的多用途 Vref 引脚,使其可用作普通I/O引脚。当7系列FPGA是板/系统中唯一需要特定 Vref 电压供电的期间,或者给定 I/O bank 中I/O引脚不足时,可考虑采用这种方式。内部生成的 Vref(INTERNAL_VREF)来自Vccaux。每个bank只有一个 Vref 平面,因此每个 I/O bank 只能将可选的INTERNAL_VREF设置为整个bank的单一电压电平。

约束INTERNAL_VREF一次只能分配给一个bank。

示例1:I/O Bank 14 采用 HSTL_II(1.5V)标准 ,需要0.75V的参考电压,对INTERNAL_VREF使用以下约束:

INTERNAL_VREF_BANK14 = 0.75;

示例2:I/O Bank 15 采用HSTL_II_18(1.8V)标准,需要0.9V的参考电压,对INTERNAL_VREF使用以下约束:

INTERNAL_VREF_BANK15 = 0.90;

使用INTERNAL_VREF的规则:

• 每个bank只能设置一个Vref值。

• INTERNAL_VREF只能设置为给定I/O标准的标称参考电压值(nominal reference voltage value)。

• INTERNAL_VREF的有效设置为:0.60、0.675、0.75、0.90。

• 在bank中使用INTERNAL_VREF时,该bank中的 多用途Vref 引脚可以用作普通I/O。

在同一个bank中组合I/O标准的规则也适用于INTERNAL_VREF。

4.10 ··· VCCAUX_IO 约束

VCCAUX_IO 是适用于 I/O 网络和原语的约束。如果要将任何 HP banks的 VCCAUX_IO 引脚设置为 2.0V,则应在设计中指定该约束。VCCAUX_IO 的默认值为 DONTCARE,但也可以设置为 NORMAL(1.8V)或 HIGH(2.0V)。

如果某一给定组的 VCCAUX_IO 引脚要以 2.0V 供电,那么该bank中至少有一个 I/O 网络或原语的 VCCAUX_IO 约束应设置为 HIGH,而该bank中的所有其他 I/O 网络和原语必须设置为 HIGH 或 DONTCARE。如果某一bank的 VCCAUX_IO 引脚要以 1.8V 供电,那么该bank中至少有一个 I/O 网络或原语的此约束应设置为 NORMAL,并且该组中的所有其他 I/O 网络和原语应设置为 NORMAL 或 DONTCARE。

在 VHDL 中,与 IOB 原语实例化相关的 VHDL 约束声明如下:

attribute VCCAUX_IO of {component_name | label_name}:

{component | label} is “{NORMAL|HIGH|DONTCARE}”;

在 Verilog 中,Verilog 约束应紧跟在 IOB 原语的模块或实例化之前。Verilog 约束的指定方式如下:

(* VCCAUX_IO = {NORMAL|HIGH|DONTCARE}*)

UCF and NCF Syntax

NET “net_name” VCCAUX_IO=(0|NORMAL|HIGH|DONTCARE);

INST “instance_name ” VCCAUX_IO=(NORMAL|HIGH|DONTCARE);

5、同一Bank中的 I/O Standards 组合规则

关于 Xilinx 7系列FPGA 所支持的不同I/O标准,详见《7系列 之 I/O标准和终端技术》。

在同一 bank 中组合不同的输入、输出和双向标准时,必须遵守以下规则:

-

1、仅组合输出标准

具有相同输出 Vcco 要求的输出标准可在同一 bank 中组合。

兼容示例:

SSTL15_I 和 LVDCI_15 输出

不兼容示例:

SSTL15(输出 Vcco=1.5V)和 LVCMOS18(输出 Vcco =1.8V)输出 -

2、仅组合输入标准

具有相同 Vcco 和 Vref 要求的输入标准可在同一 bank 中组合。

兼容示例:

LVCMOS15 和 HSTL_II 输入

不兼容示例:

LVCMOS15(输入 Vcco=1.5V)和 LVCMOS18(输入 Vcco=1.8V)

不兼容示例:

HSTL_I_DCI_18(输入 Vref=0.9V)和 HSTL_I_DCI(输入 Vref=0.75V) -

3、组合输入与输出标准

具有相同 Vcco 要求的输入和输出标准可在同一 bank 中组合。

兼容示例:

LVDS_25 输出和 LVCMOS25 输入

不兼容示例:

LVDS_25 输出(输出 Vcco=2.5V)和 HSTL_I_DCI_18 输入(输入 Vcco=1.8V) -

4、组合双向标准与输入 / 输出标准

当双向 I/O 与其他标准组合时,需确保双向标准满足前三条规则。 -

5、组合 DCI I/O 标准的额外规则

任意 HP I/O 组(或使用 DCI 链式连接时的组群)中,只能使用一个 DCI 目标电阻值(控制驱动输出阻抗或分离终端)。

不兼容示例:

HSUL_12_DCI 输出(40Ω 输出阻抗)和 SSTL12_T_DCI 输入(100Ω/100Ω 分段终端)

6、参考文献

1、《ug471_7Series_SelectIO.pdf》

2、《FPGA中Bank和Clock Region之前有什么关系?》

3、《GMII转RGMII(一)IOB相关原语介绍》

4、《FPGA理论基础1一一一简单的硬件知识》

5、《GMII转RGMII(一)IOB相关原语介绍》