软件设计师教程——第一章 计算机系统知识(下)

前言

在竞争激烈的就业市场中,证书是大学生求职的重要加分项。中级软件设计师证书专业性强、认可度高,是计算机相关专业学生考证的热门选择,既能检验专业知识,又有助于职业发展。本教程将聚焦核心重点,以点带面构建知识体系,秉持“以考促学”理念,助力大家高效备考、顺利通关。

一、指令系统

定义

指计算机所能执行全部指令的集合,它描述了计算机全部的控制信息和“逻辑判断”能力

一条指令包括:操作码、地址码

分类

根据地址码代表的地址类型,指令系统可以分为:

1.立即寻址

立即寻址是指指令中直接包含操作数(立即数),处理器执行指令时直接使用该立即数,无需访问

内存获取操作数

2.直接寻址

直接寻址是指令中直接给出操作数在内存中的地址,CPU依据此地址直接对内存进行读写操作

3.间接寻址

间接寻址是指指令中给出的是操作数地址的地址,CPU需先获取该中间地址中的值,再据此访问内

存得到操作数

4.寄存器寻址

寄存器寻址是指令直接指定寄存器来进行操作数或结果的存取,因寄存器在CPU内,访问快,能提

升数据处理效率

5.寄存器间接寻址

寄存器间接寻址是指指令指定的寄存器存放操作数地址,CPU依此地址访问内存取操作数,常用于

处理数组等数据结构

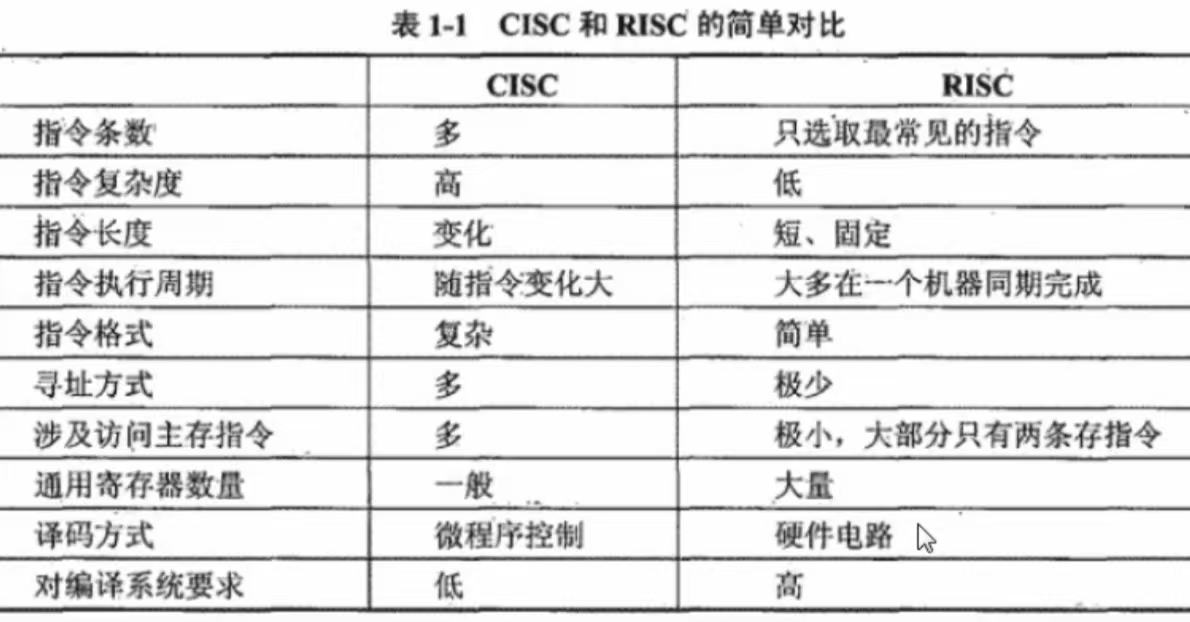

CISC与RISC

CISC(复杂指令集计算机)

定义

为提高操作系统的效率,人们最初选择向指令系统中添加更多、更复杂的指令来实现,导致指令集

越来越大。这种类型的计算机,称为CISC(复杂指令集计算机)

主要特点

(1)指令数量多:

指令系统拥有大量的指令,有100-250条

(2)指令使用频率相差悬殊:

最常使用的是一些比较简单的指令,80%的时候使用的是20%指令

(3)支持很多种寻址方式:

通常为5-20种

(4)变长的指令:

指令长度不是固定的,变长的指令增加指令译码电路的复杂性

(5)指令可以对存储器单元中数据直接进行处理:

典型的CISC处理器通常都有指令能够直接对内存单元中的数据进行处理,其执行速度较慢

RISC(精简指令集计算机)

定义

对指令数目和寻址方式做精简,指令的指令周期相同,采用流水线技术,指令并行执行程度更好。这类是RISC(精简指令集计算机)

主要特点

(1)指令数量少:

优先选取使用频率最高的一些简单指令以及一些常用指令,避免使用复杂指令

(2)指令的寻址方式少:

通常只支持寄存器寻址方式、立即数寻址方式以及相对寻址方式

(3)指令长度固定,指令格式种类少:

因为RISC指令数量少,格式相对简单,其指令长度固定,指令之间各字段的划分比较一致,译码相对容易

(4)只提供了Load/Store指令访问存储器:

只提供了从存储器读数Load和把数据写入存储器Store两条指令,其余所有的操作都在CPU的寄存器间进行

(5)以硬布线逻辑控制为主:

为了提高操作的执行速度,通常采用硬布线逻辑来构建控制器

(6)单周期指令执行:

因为简化了指令系统,很容易利用流水线技术使得大部分指令在一个机器周期内完成

(7)优化的编译器:

RISC精简指令集使编译工作简单化

对比图:

二、存储系统

定义

存储器是计算机系统中的记忆设备,用来存放程序和数据、计算机中全部信息,包括输入的原始数据、计算机程序、中间运行结果和最终运行结果都保存在存储器中

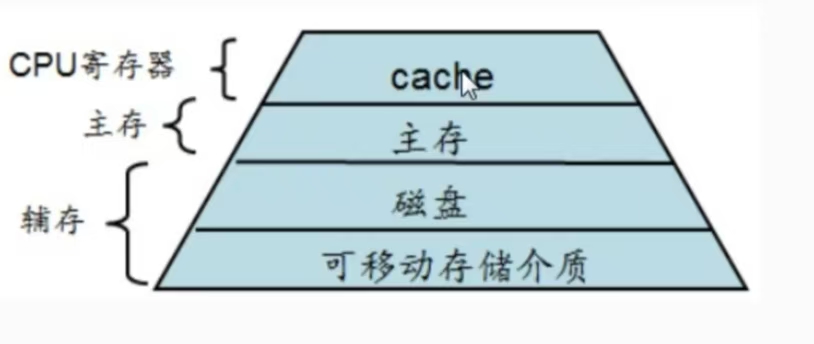

分类

(容量:由低到高;速度:由快到慢)

寄存器

Cache(高速缓冲存储器)

主存储器

辅存储器

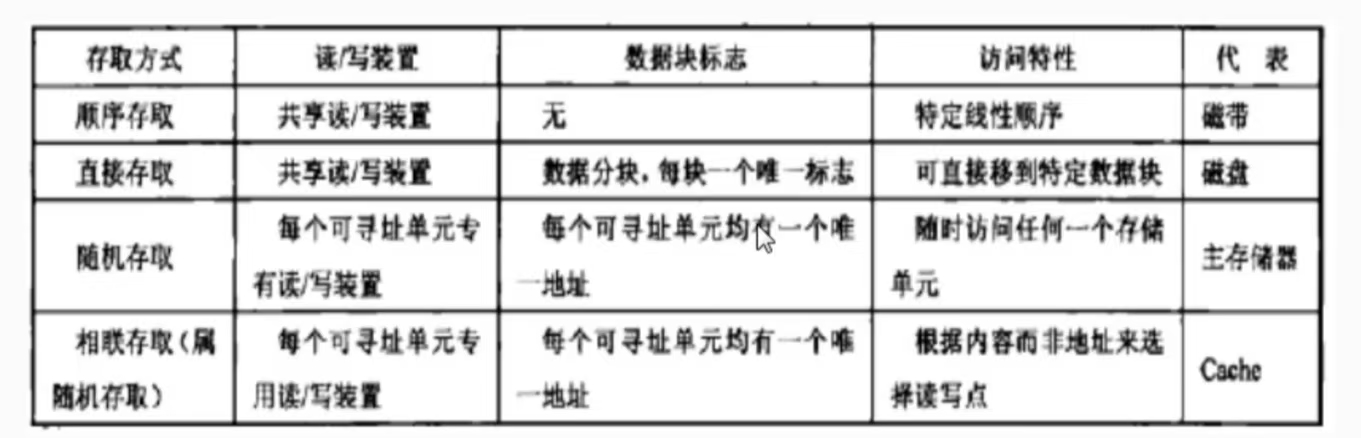

1.存储器的存取方式

2.存储器的性能

存取时间:

对于随机存取而言,就是完成一次读/写所花的时间

对非随机存取,就是将读/写装置移动到目的位置所花的时间

存储器带宽:

每秒能访问的位数。通常存储器周期是纳秒级(ns)

计算公式是:

1/存储器周期×每周期可访问的字节数

例如:

存储器周期是200ns,每个周期可访问4B,则带宽=1s/200ns×(4Bx8)=160Mbps

3.数据传输率

每秒输入/输出的数据位数

对于随机存取而言,传输率R=1/存储器周期

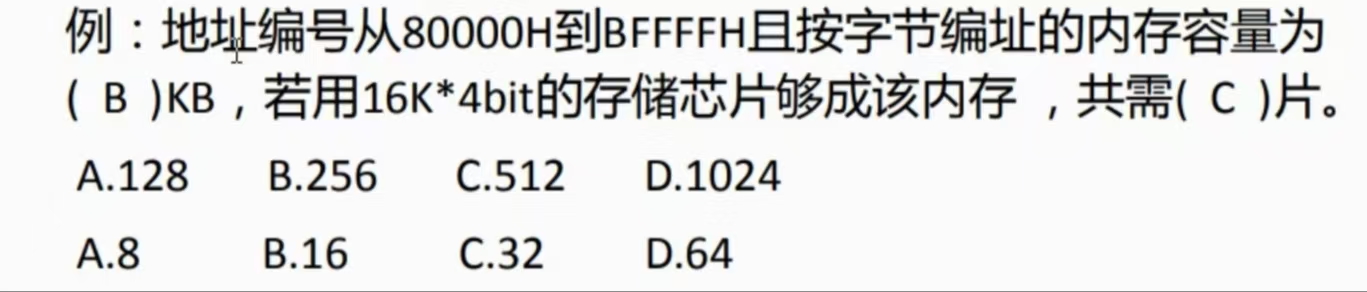

三、主存储器

主存储器的种类

1.RAM:

随机存储器,可读/写,只能暂存数据,断电后数据丢失

SRAM:

静态随机存储器,在不断电时信息能够一直保持,读写速度快,生产成本高,多用于容量

较小的高速缓冲存储器

DRAM:

动态随机存储器,需要定时刷新以维持信息不丢失,读写速度较慢,集成度高,生产成本

低,多用于容量较大的主存储器

2.ROM:

只读存储器,出厂前用掩膜技术写入,常用于存放BIOS和微程序控制

四、Cache

高速缓冲存储器是位于主存与CPU之间的一级存储器,由静态存储芯片(SRAM)组成,容量比较小但速度比主存高得多,接近于CPU的速度。但其成本更高,因此Cache的容量要比内存小得多。

Cache存储了频繁访问内存的数据

原理

使用Cache改善系统性能的主要依据是程序的局部性原理。

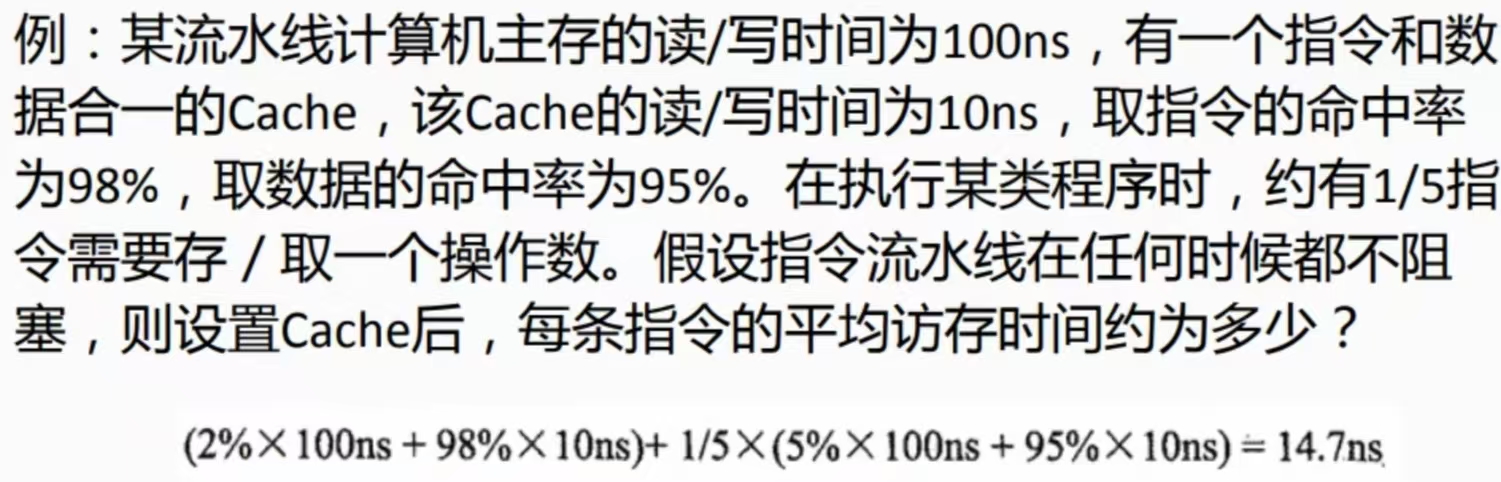

命中率、失效率

Cache的访问命中率为h(通常1-h就是Cache的失效率),Cache的访问周期时间是t1,主存储器的访问周期时间是t2,则整个系统的平均访存时间就是:t3 = h x t1+(1-h ) x t2

五、总结

软考对职业发展意义重大。本教程面向自学能力较强者,非完整知识体系。旨在通过核心要点梳理构建知识框架,以考促学提升技能。