智芯Z20K144x MCU开发之时钟架构

这里写目录标题

- 一、zhixin时钟架构

- 1.时钟源

- 2.系统时钟控制器(SCC)

- 3.外设时钟控制器(PARCC)

- 二、软件应用

- 三、总结

一、zhixin时钟架构

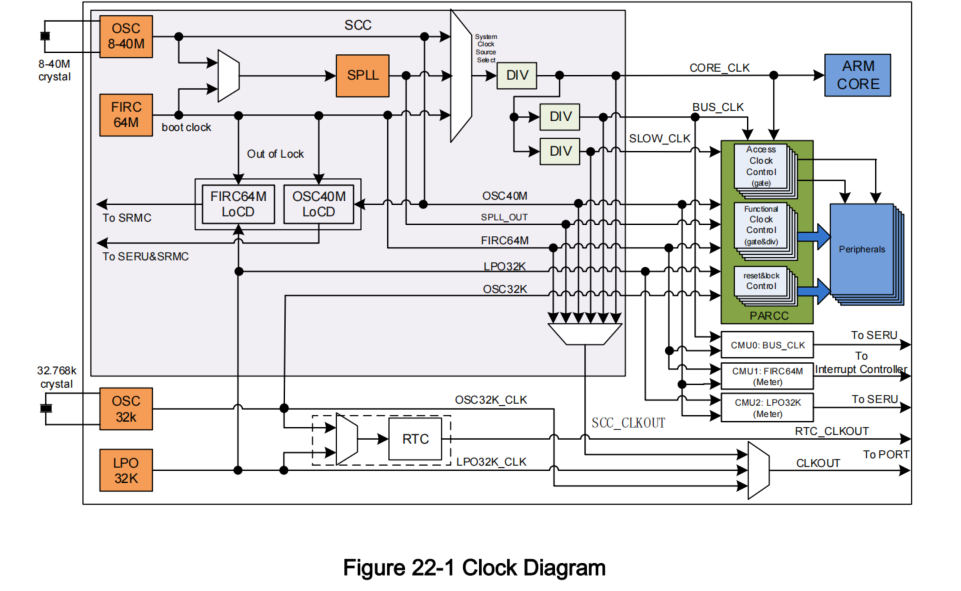

可以将时钟架构分解为三个部分来理解:

- 时钟源(OSC、FIRC、LPO)

- 系统时钟控制器(SCC)

- 外设时钟控制器 (PARCC)

其中SCC产生的时钟信号主要输出至PARCC进而分配至对应的外设使用;

LPO主要一般主要用于低功耗,输出智SRMC进行低功耗管理;

所有时钟信号均可输出至Port进而配置在对应的引脚上,可以通过示波器观测;

1.时钟源

三种时钟源特性对比:

| 时钟源名称 | 特性 |

|---|---|

| OSC(晶振) | 精度高(误差ppm(百万分之一)级别)、启动慢、功耗高 |

| FIRC(内部RC振荡器) | 精度始中(百分之几到千分之几)、快速启动、功耗适合中 |

| LPO(低功耗振荡器) | 精度相对较低、功耗较低 |

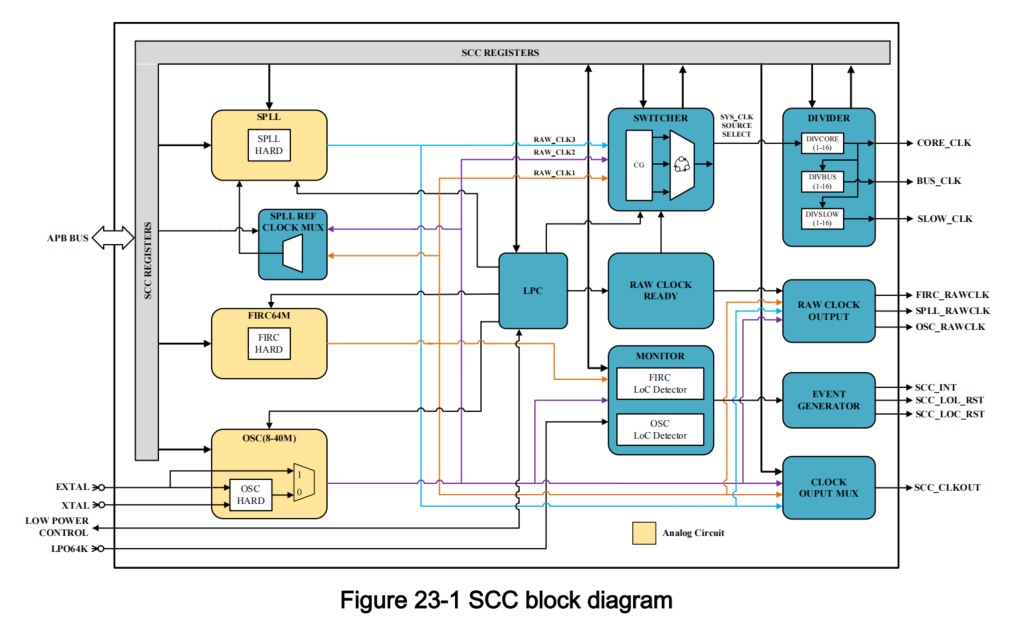

2.系统时钟控制器(SCC)

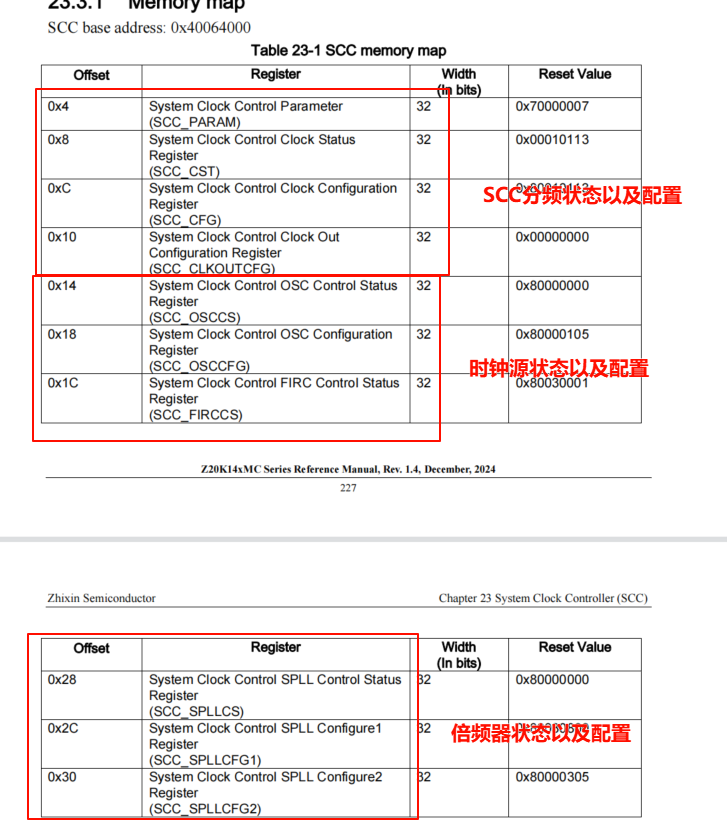

Cpu通过APB总线访问SCC寄存器进而配置系统时钟分配,SCC主要负责系统时钟相关的参数配置以及输出监控,以下为主要使用寄存器介绍:

SCC_PARAM:只读 记录当前MCU设计参数

SCC_CST:只读 记录当前各个分频器以及复选器参数配置

SCC_CFG:附带寄存器锁 设置各个分频器以及复选器参数

SCC_CLKOUTCFG:选择所需的时钟源输出至CLKOUT复用功能的Pin

SCC_OSCCS:附带寄存器锁 控制OSC工作模式以及状态监控

- 可以设置OSC信号loss时是触发中断还是复位

- 可以监控OSC信号是否ready

- 可以设置OSC监控模式(前提FIRC必须保持有效)

SCC_OSCCFG:OSC参数配置

- 选择什么类型外部时钟源(晶振/其他方波源)

- 高频模式配置(高于24M)

- 驱动电流配置(不同频率选择对应配置)

SCC_FIRCCS:控制FIRC工作模式以及状态监控,功能与SCC_OSCCS类似不再赘述

SCC_SPLLCS:控制SPLL工作模式以及状态监控,功能与SCC_OSCCS类似不再赘述

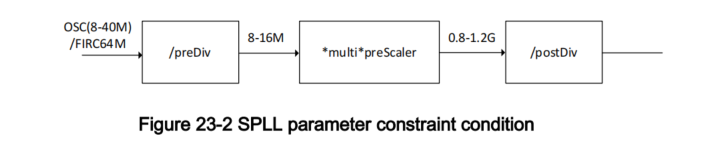

SCC_SPLLCFG1:SPLL锁相环参数配置,可以倍频出更高频率的时钟

SCC_SPLLCFG2:SPLL锁相环参数配置,可以倍频出更高频率的时钟

SPLL锁相环倍频计算方法如下:

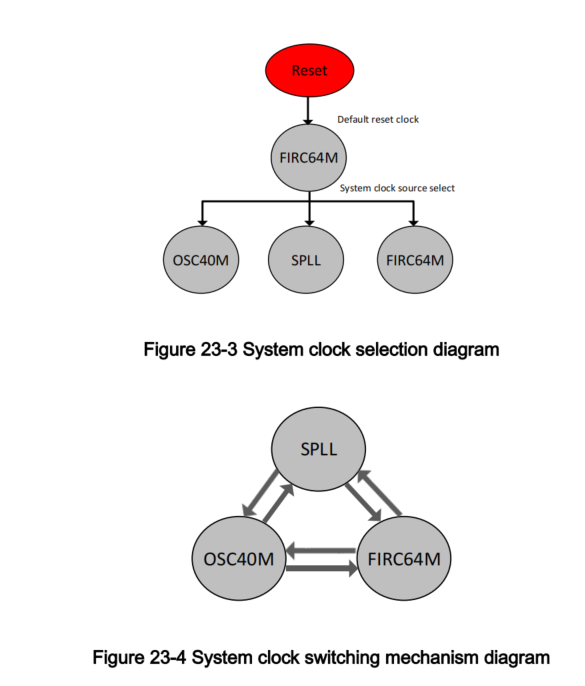

默认复位状态下System clock是由FIRC驱动的,后续软件配置选择对应的时钟源后进行切换:

3.外设时钟控制器(PARCC)

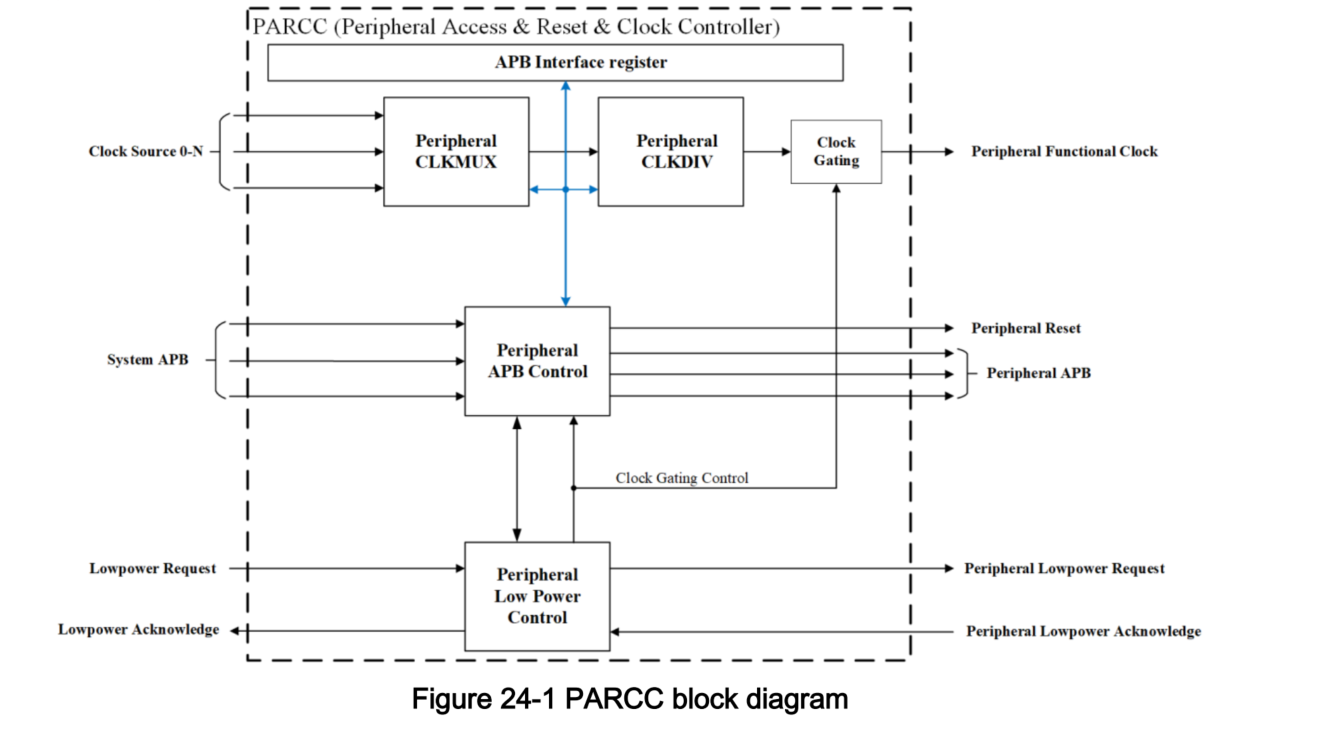

PARCC(Peripheral Access & Reset & Clock Controller)是用于访问外设&复位&时钟分配功能的模块,主要功能如下:

- 外设访问保护

- 外设复位

- 外设时钟分配(clkmux用于选择所需的时钟源,CLKDIV用于外设时钟分频)

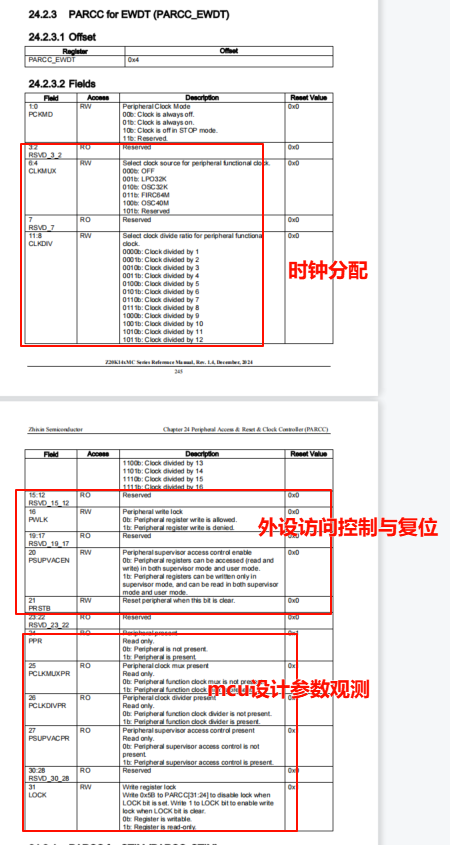

由PARCC架构图可知,PARCC主要由3个部分组成:外设时钟配置模块、APB外设访问以及控制模块、外设低功耗控制模块;由PARCC模块寄存器为每个外设都开辟了独立的寄存器,功能基本相同,因此以下仅以一个PARCC寄存器举例介绍:

二、软件应用

下面展示一些 内联代码片。

//FIRC时钟源使能控制

void CLK_FIRC64MEnable(ControlState_t stopModeEn);

void CLK_FIRC64MDisable(void);

//获取system clk使用的时钟源是OSC还是FIRC

CLK_System_t CLK_GetSysClkSrc(void);

//OSC时钟使能控制

ResultStatus_t CLK_OSC40MEnable(uint32_t freq, ControlState_t stopModeEn, CLK_OscMode_t mode);

ResultStatus_t CLK_OSC40MEnable2(CLK_OscFreqMode_t freqMode, ControlState_t stopModeEn, CLK_OscMode_t mode);

void CLK_OSC40MDisable(void);

//system clk选择时钟源

ResultStatus_t CLK_SysClkSrc(CLK_System_t clk);

//配置osc 40M时钟Loss监控

void CLK_OSC40MMonitorEnable(CLK_MonitorAct_t act);

//关闭osc 40M时钟Loss监控

void CLK_OSC40MMonitorDisable(void);

//配置FIRC时钟Loss监控

void CLK_FIRC64MMonitorEnable(CLK_MonitorAct_t act);

//关闭FIRC时钟Loss监控

void CLK_FIRC64MMonitorDisable(void);

//LPO低功耗时钟源使能控制

void CLK_LPO32KEnable(void);

void CLK_LPO32KDisable(void);

//OSC 32K时钟使能控制

void CLK_OSC32KEnable(CLK_OscMode_t mode);

void CLK_OSC32KDisable(void);

//scc设置时钟分配

void CLK_SetClkDivider(CLK_Module_t module, CLK_Divider_t divider);

//选择对应外设时钟源

ResultStatus_t CLK_ModuleSrc(CLK_Module_t module, CLK_Src_t clockSource);

//选择TIM外部时钟源

void CLK_TimExternalClkSrc(CLK_TIM_t timId, CLK_TIMExtClk_t clockSrc);

//选择对应的时钟源输出至外部PIN

void CLK_ClkOutEnable(CLK_OutSrc_t outSrc, CLK_OutDiv_t divider);

void CLK_ClkOutDisable(void);

//获取对应外设时钟频率

uint32_t CLK_GetModuleClkFreq(CLK_Module_t module,uint32_t oscFreq);

//获取时钟源状态

FlagStatus_t CLK_GetClkStatus(CLK_Src_t clockSource);

//等待时钟源状态ready

ResultStatus_t CLK_WaitClkReady(CLK_Src_t clockSource);

//SCC安装终端回调函数可以配置当时钟源丢失时进入中断

void SCC_InstallCallBackFunc(CLK_Int_t intId,isr_cb_t * cbFun);

//清楚SCC中断标志位

void SCC_IntClear(CLK_Int_t intId);三、总结

本文为博主开发过程中总结而得,如有不正之处欢迎指正。