PCIe控制器介绍(二)

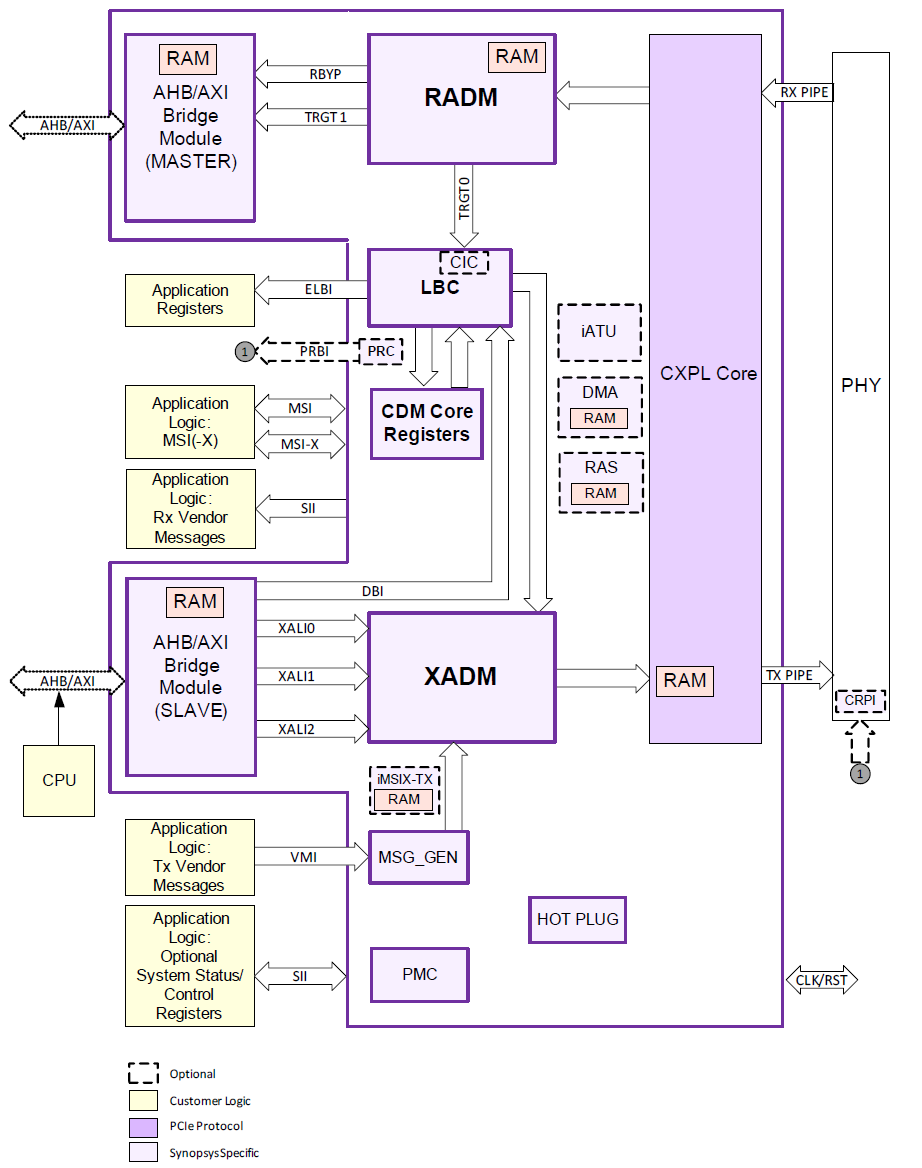

PCIe EP核心功能图如下:

上图从左往后依次是:应用层、事务层、链路层和物理层。CXPL及其右边的逻辑属于大部分事务层、链路层和物理层;也就是说,上图CXPL左边基本上应用层。

1. 接收通路

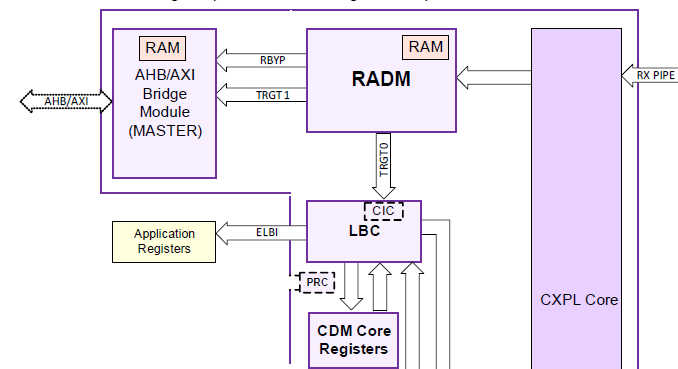

CXPL模块通过RX PIPE从物理层PHY接收到TLP数据包,并将TLP数据包提交给RADM模块。RADM模块存在两类接口:TRGT0接口、TRGT1/RBYP接口。

TRGT0接口是用来专门访问CDM寄存器,或者通过ELBI访问应用层寄存器。

RADM模块可配置外部或内部RAM用于接收队列(外部RAM设计复杂度高,但单位面积上的存储容量大;内部RAM设计复杂度底,但单位面积上的存储容量小)。

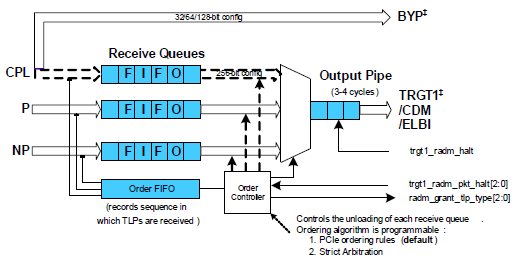

RADM在逻辑上实现了三个FIFO队列,分别是CPL FIFO、P FIFO和NP FIFO。CPL FIFO是用于接收TLP完成包;P FIFO是用于接收TLP非确认请求包,例如非确认写请求;NP FIFO是用于接收TLP确认请求包,例如读请求或确认写请求。

逻辑接收队列的三种模式:存储转发S/F、快通C/T、旁路B/P。

| S/F | C/T | B/P |

| TLP包全部存入缓冲 | TLP包的某些字段存入缓冲 | 无缓冲 |

| TLP包被处理完成后再提交给应用层 | TLP包立即提交给应用层 | |

| 应用层可以停止RADM提交TLP包 | 应用层*不*可以停止RADM提交TLP包 | |

| RADM管理信令 | RADM*不*管理信令 | |

| 保序 | 不保序 | |

| RADM检查错误后,将正确TLP进行提交 | RADM不检查错误,直接将TLP进行提交 | |

只有FIFO队列的第一个TLP包处理模式是快通C/T。这句话的意思是,即使FIFO队列设置为快通模式,如果FIFO队列中存在两个或两个以上的TLP包,除了第一个TLP包之外的所有TLP包都是按照存储转发S/F模式来处理的。

无论是信号trgl_radm_halt有效还是trgt1_radme_pkt_halt[2:0]信号有效,都将阻止TLP包从FIFO队列进入输出管道(Output Pipe)。直接采用信号trgl_radm_halt可能发生死锁:当NP TLP包进入输出管道,应用层接收到NP TLP包时,如果将信号trgl_radm_halt设置有效,就可能将后续P TLP包阻塞。

为了避免这种死锁情况发生,需要另外设计一个NP TLP跟踪器逻辑,该逻辑用信号trgt1_radme_pkt_halt [2:0] 信号(0:P FIFO、1:NP FIFO、2:CPL FIFO)提前通知RADM“应用层不能接收指定类型的TLP包”,RADM就会阻塞对应类型的FIFO队列。

ELBI接口(这个接口可以不使用,而是直接使用AXI-MASTER访问应用层寄存器)

LBC控制器通过ELBI接口可以访问应用层寄存器,我猜,LBC还会针对寄存器的访问对应生成一个TLP完成包。

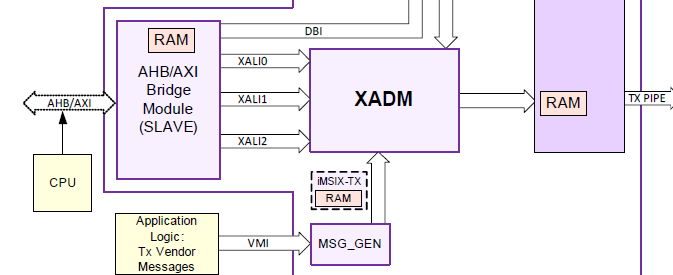

2. 发送通路

应用层通过XALI0/1/2向PCIe总线发送TLP包,包括NP/P TLP请求包或TLP完成包。三个接口是相同的逻辑,建议:XALI0用于P TLP请求包的发送;XALI1用于NP TLP请求包的发送;XALI2用于TLP完成包发送。

另外,应用层逻辑可以通过MSI接口或MSI-X接口向PCIe总线发送TLP中断消息包。手册中的图和文字描述有冲突,我的理解是:应用层的中断逻辑如果想想PCIe RC发送MSI或MSI-X中断,就是通过MSI接口或MSI-X接口通知MSG_GEN逻辑,MSG_GEN生成TLP中断消息包提交给XADM,最终通过TX PIPE发送到PCIe总线上。