基于FPGA控制ADC0832双通道采样+电压电流采样+LCD屏幕显示

基于FPGA控制ADC0832双通道采样+电压电流采样+LCD屏幕显示

- 前言

- 一、芯片手册阅读

- 1.SPI通信时序

- 二、仿真分析

- 三、代码分析

- 总结

- 视频演示

前言

定制

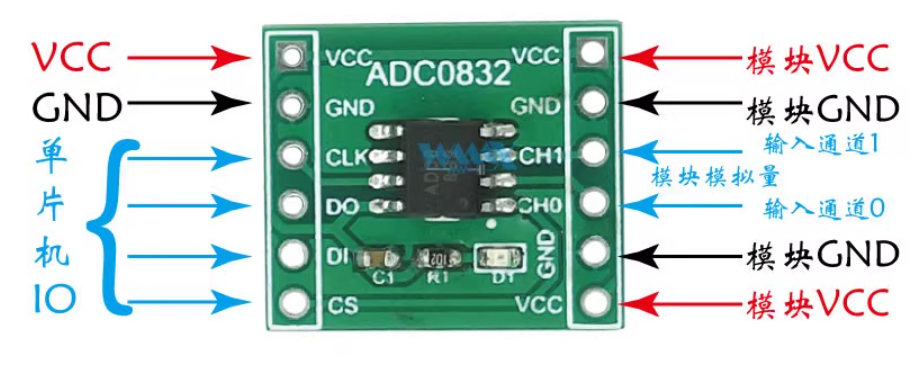

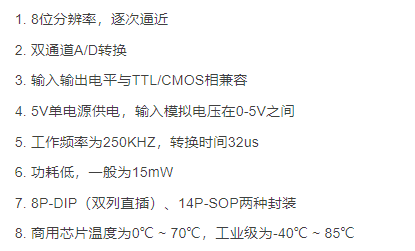

要求使用ADC0832芯片进行ADC采样。其中电压采样以及电流采样是固定电路,是硬件设计,跟软件没没关系。本质上是进行了两路的电压信号采集。

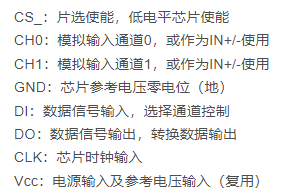

引用:ADC0832模块说明

一、芯片手册阅读

1.SPI通信时序

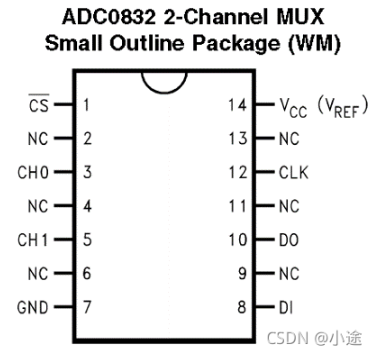

确定SPI相关信息:

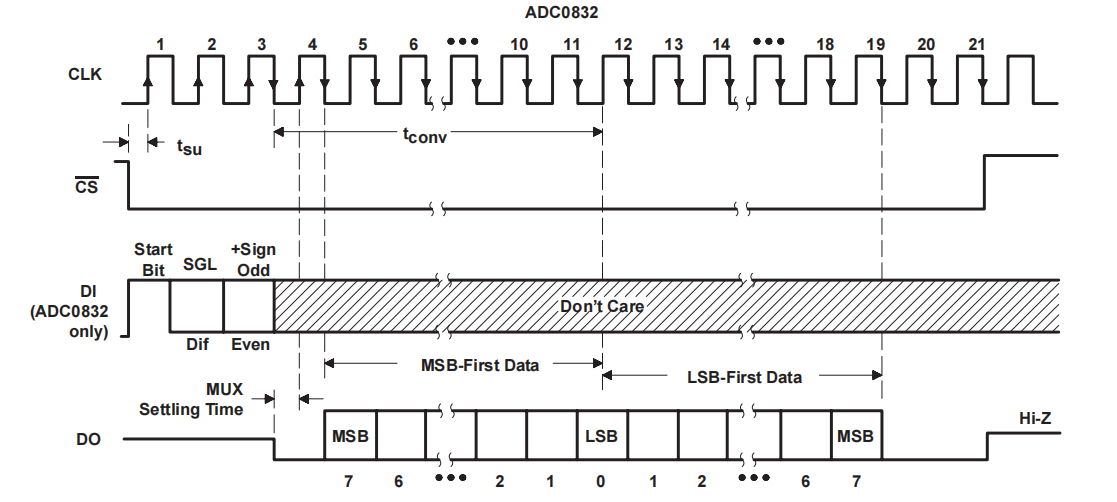

第一个空闲状态下CLK和DI的状态,图上显示CLK默认为低电平,上升沿设置数据,下降沿读取数据。DI空闲状态下为高电平。

CS正常拉低。

DOUT数据输出15个bit,本身这个ADC是8位,因此输出的数据就是8bit的,但是这个芯片本身有一个验证的功能吧相当于。分别把这个8位数据输出两次,先从高位输出到低位,再从低位输出到高位,其中低位是共用的。如果两个8位数据一致,则输出。否则认为ADC采样有问题。

数据构成相关说明:

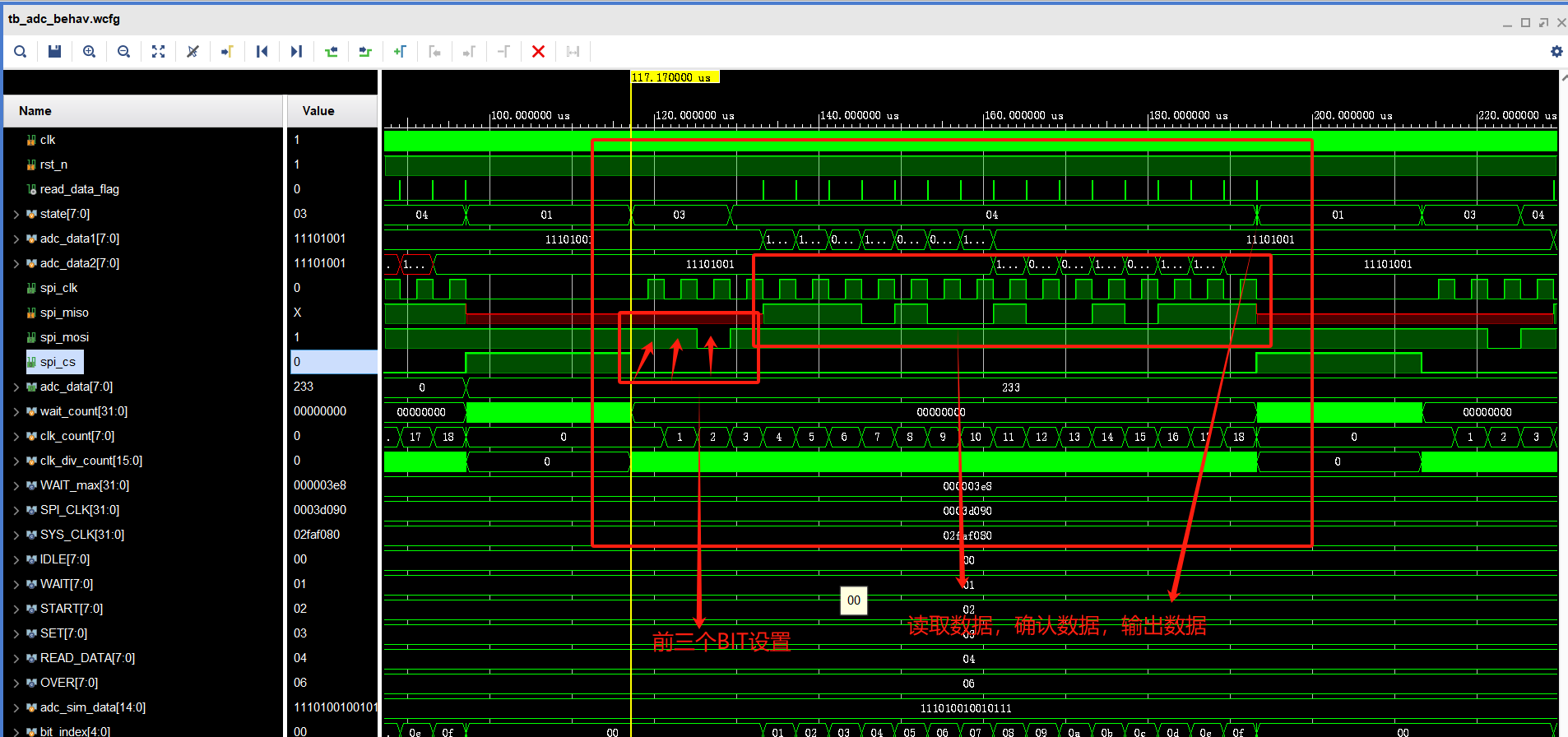

跟一般的SPI AD采样的过程的区别就是前3个bit是进行设置。第四个脉冲的下降沿进行输出数据,但是用第五个的脉冲的上升沿读取数据更加合理,所以一共需要3+1+15个脉冲,也就是19个脉冲。

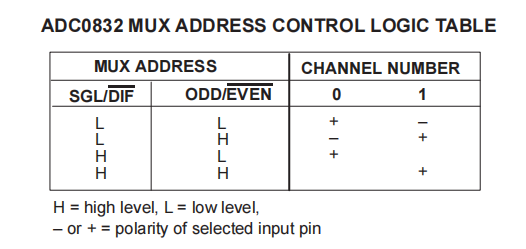

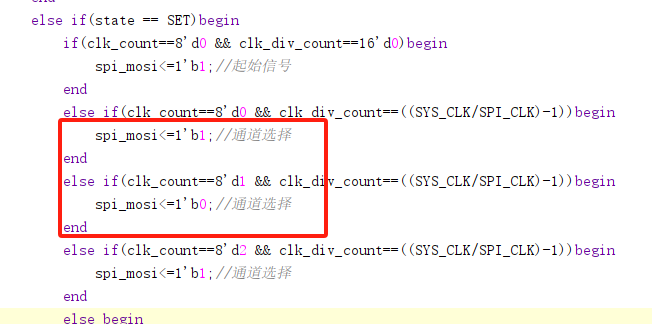

这个就是对前三个比特说明:第一个比特必须为高,目的是告诉ADC要开始读取了。其次后面两个比特是进行采样通道的设置,10就是用通道0,11就是用通道1.其他就是差分输入了,我用不到。

二、仿真分析

通过改通道10或者11就实现两个通道的切换了。

仿真只做了一种通道,后面实际上板是两个通道来回采样,实现了两个通道的采样。

三、代码分析

主要就是状态机的轮转

//state goalways @(posedge sys_clk or negedge rst_n)beginif(!rst_n)beginstate<=IDLE;adc_data1_temp<=16'd0;adc_data2_temp<=16'd0;CH_SET<=1'b0;lcd_flag<=1'b0;endelse begincase(state)IDLE:beginstate<=WAIT;lcd_flag<=1'b0;CH_SET<=~CH_SET;endWAIT:beginif(wait_count==WAIT_max)beginstate<=START;endelse beginstate<=WAIT;endendSTART:beginstate<=SET;endSET:beginif(clk_count==8'd3)beginstate<=READ_DATA;endelse beginstate<=SET;endendREAD_DATA:beginif(clk_count==8'd19)beginstate<=OVER;endelse beginstate<=READ_DATA;endendOVER:beginstate<=SAVE_DATA;endSAVE_DATA:beginstate<=IDLE;lcd_flag<=1'b1;if((adc_data1==adc_data2) && CH_SET==1'b1)beginadc_data1_temp<= ((adc_data1 * 3300) >> 4'd8);endelse if((adc_data1==adc_data2) && CH_SET==1'b0)beginadc_data2_temp<= ((adc_data1 * 3300) >> 4'd8);endelse beginadc_data1_temp<=adc_data1_temp;adc_data2_temp<=adc_data2_temp;endenddefault:state<=IDLE;endcaseendend

总结

视频演示

基于FPGA控制ADC0832双通道采样+电压电流采样+LCD屏幕显示