41.防静电的系列措施

静电干扰的处理措施

- 1. ESD放电特征

- 2. 静电防护电路设计措施

- 3. ESD防护结构措施

- 4. 案例分析

1. ESD放电特征

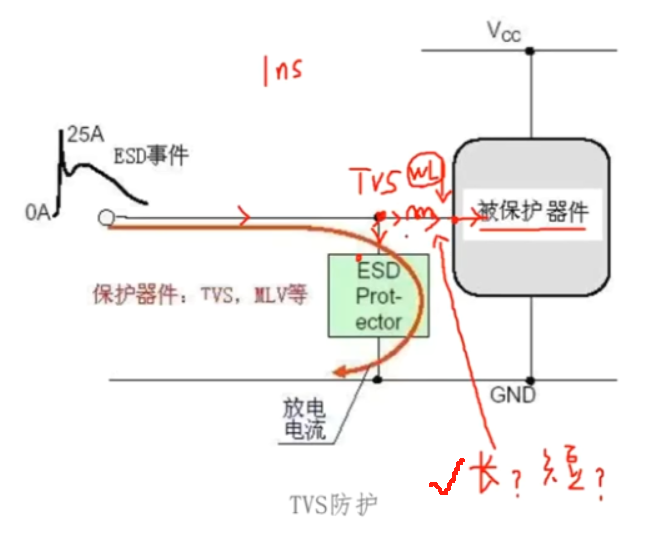

(1)放电电流tr≈1nS,ESD保护器件响应时间应小于1nS;

(2)频率集中在几十MHz到500MHz;

(3)ESD接触到IC引脚,Ip达几十安培,会烧伤IC融化硅片管芯、内部金属连接烧断、钝化层被破坏,晶体管单元烧坏;

(4)ESD会引起IC闩锁(LatchUp),CMOS内部类可控硅结构单元被激活,形成从VCC-GND的大电流,而且一直保持,轻症短路失效,重症烧毁。

2. 静电防护电路设计措施

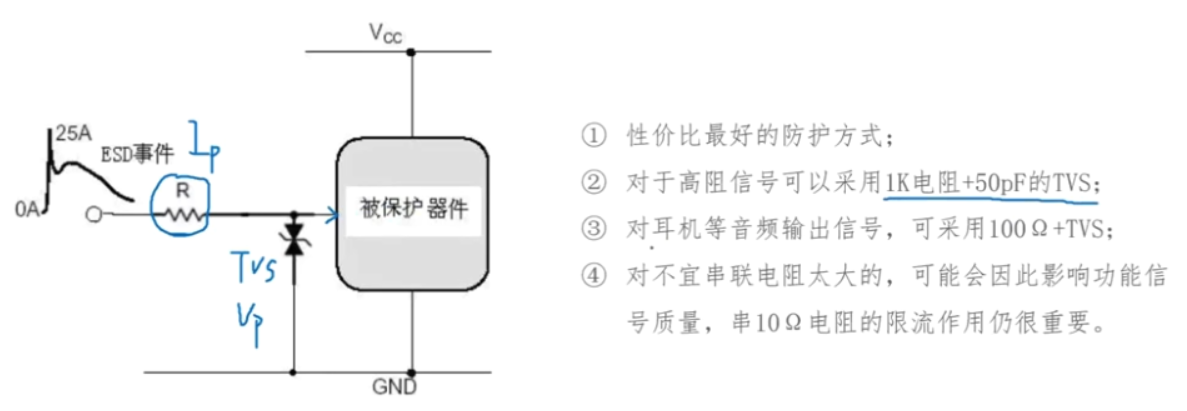

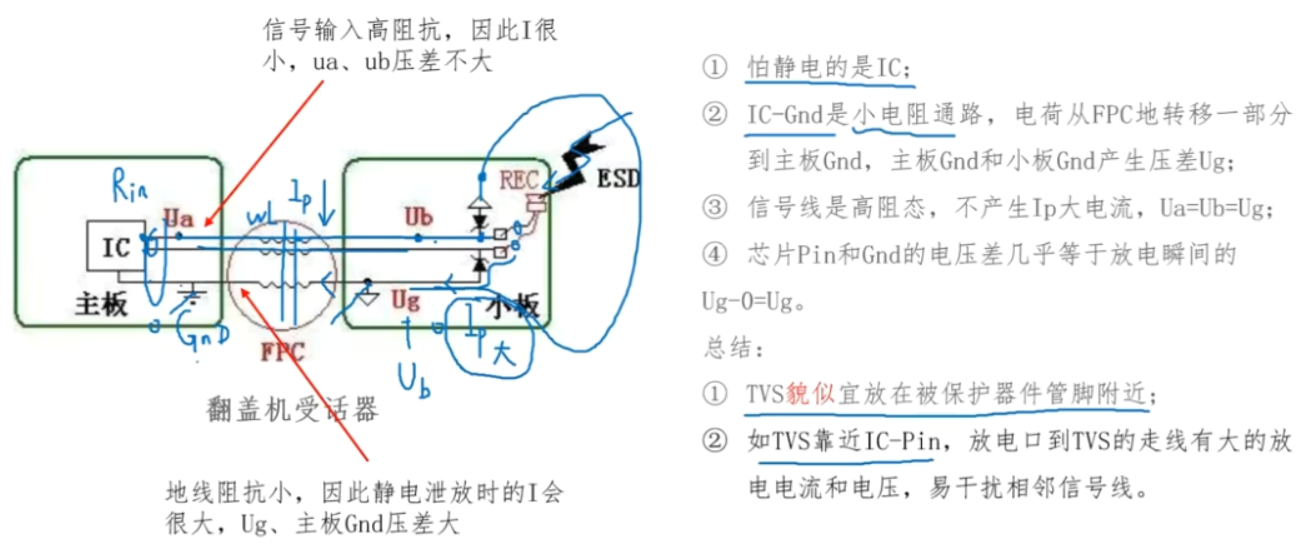

(1)通常情况下,TVS离被保护IC引脚远一点更好,利用走线电感降低残压。

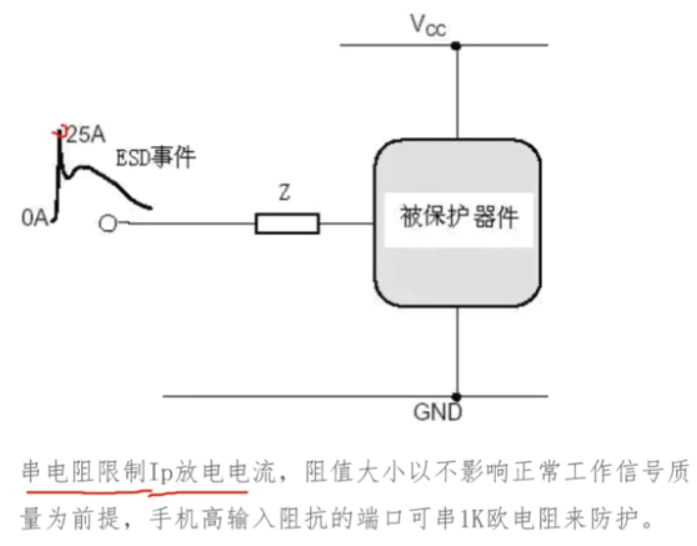

(2)串接电阻限制尖峰电流Ip.

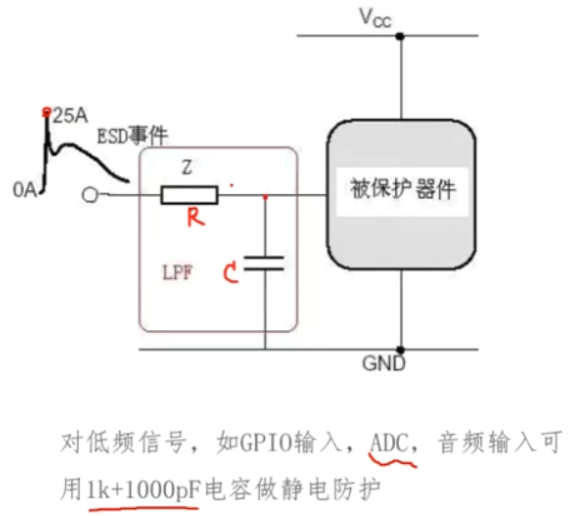

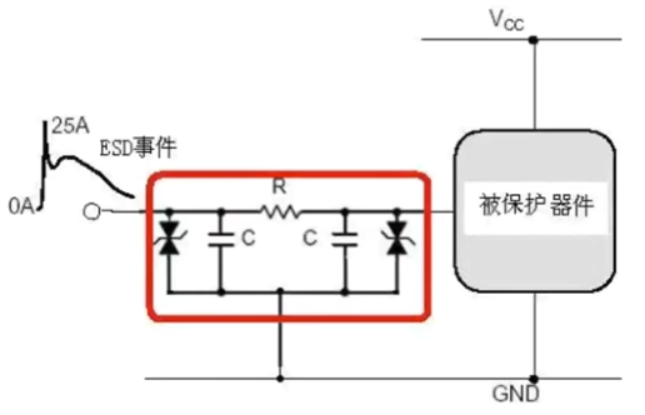

(3)低频信号通过RC电路保护,R限流,C限压。

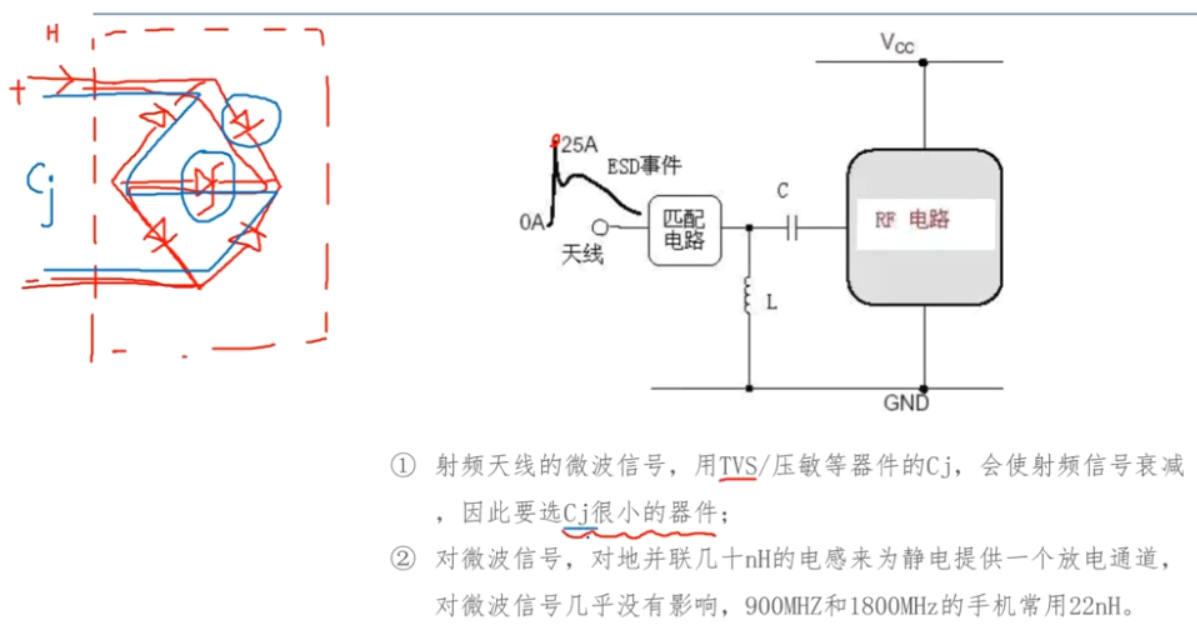

(4)射频电路防护

(5)复合防护

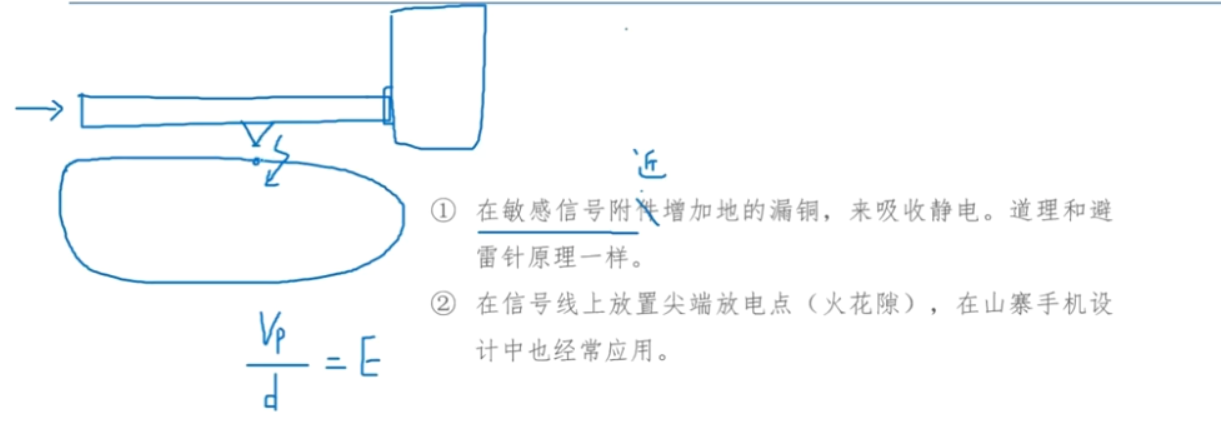

(6)增加吸收回路,通过尖端对地放电

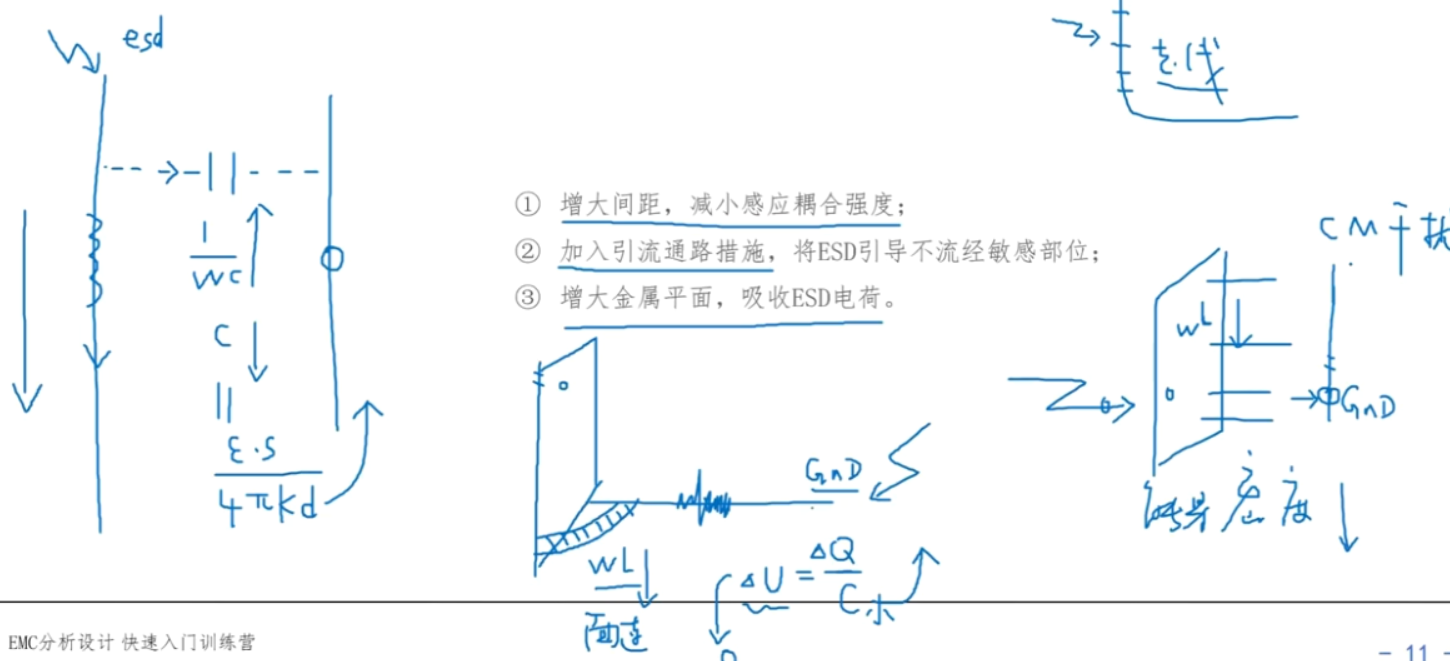

3. ESD防护结构措施

(1)增大间距,减小感应耦合强度;

(2)加入引流通路措施,将ESD引导不流经敏感部位;

(3)增大金属平面,吸收ESD电荷。可以将GND接到一块浮空的金属上,增大自身电容性,或者用金属隔离ESD干扰。

4. 案例分析

如果IC输入阻抗很高,那么静电干扰流入IC的电流很小。即使TVS管远离IC,TVS管和IC引脚间的走线电感所分担的压降仍然很小。要格外小心地阻抗不足够小的情况,靠近IC的地方可能也需要加一个TVS管。