逐次逼近式A/D转换器

AD转换器:

| 类型 | 计数式A/D转换器 | 双积分式A/D转换器 | 逐次逼近式A/D转换器 |

|---|---|---|---|

| 定义 | 通过计数器逐步增加数字量,并与模拟输入电压比较,直到两者匹配,计数结果即为转换值。 | 通过两次积分(对输入电压和参考电压的积分)将模拟电压转换为时间宽度,再转换为数字量。 | 通过二分搜索策略,逐次比较输入电压与DAC生成的电压,最终逼近输入电压值。 |

| 转换速度 | 慢(转换时间与输入电压大小成正比) | 较慢(依赖积分时间,通常毫秒级) | 快(转换时间固定,通常微秒级) |

| 精度 | 较低(受计数器步进限制) | 高(积分过程抑制噪声,抗干扰能力强) | 中等至高(取决于DAC位数和比较器精度) |

| 复杂度 | 简单 | 中等(需积分器和时钟控制) | 较高(需精密DAC和逐次逼近逻辑) |

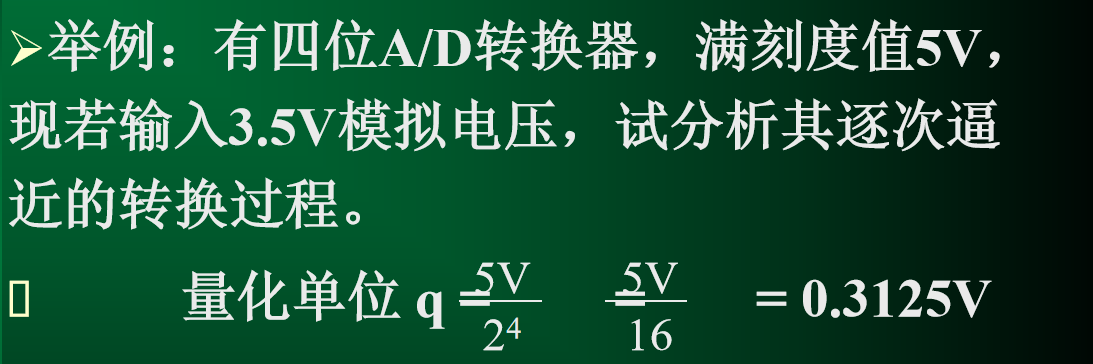

在逐次逼近式A/D转换器(SAR ADC)中,试探值的顺序遵循二分搜索法(Binary Search),从最高位(MSB)到最低位(LSB)逐步确定每一位的值。

以输入电压 Vin = 3.5V、满量程 5V 为例:

| 步骤 | 当前位 | 试探值(二进制) | DAC输出电压 | 比较(Vin ≥ DAC输出?) | 该位结果 | 更新后的数字量 |

|---|---|---|---|---|---|---|

| 1 | D3(MSB) | 1000 | 5V × (8/16) = 2.5V | 3.5V ≥ 2.5V → 是 | 1 | 1000 |

| 2 | D2 | 1100 | 2.5V + 5V × (4/16) = 3.75V | 3.5V ≥ 3.75V → 否 | 0 | 1000 |

| 3 | D1 | 1010 | 2.5V + 5V × (2/16) = 3.125V | 3.5V ≥ 3.125V → 是 | 1 | 1010 |

| 4 | D0(LSB) | 1011 | 3.125V + 5V × (1/16) ≈ 3.4375V | 3.5V ≥ 3.4375V → 是 | 1 | 1011 |

D/A转换器:

D/A转换器的原理可以归纳为“按权展开,然后相加”。因此,D/A转换器内部必须要有一个解码网络(decode network),以实现按权值分别进行D/A转换。解码网络通常有两种:二进制加权电阻网络和T型电阻网络。

| 特性 | 二进制加权电阻网络 | T型电阻网络(R-2R) |

|---|---|---|

| 定义 | 由一组电阻构成,阻值按二进制权重(如R, 2R, 4R, 8R…)排列,通过开关切换产生不同电压。 | 由两种阻值(R和2R)的电阻构成梯形结构,通过节点分压实现二进制加权电流或电压输出。 |

| 原理 | 每个电阻代表一个二进制位,电流/电压叠加实现DAC输出。 | 利用R-2R节点的等效电阻恒定特性,通过分流实现精确的二进制加权输出。 |

| 电阻值分布 | 阻值按2ⁿ指数增长(如1kΩ, 2kΩ, 4kΩ…)。 | 仅需两种阻值(R和2R),如所有水平电阻为2R,垂直电阻为R。 |

| 优点 | 1. 结构简单直观。 2. 低位数时易于实现。 | 1. 电阻种类少,易于集成。 2. 高精度和线性度。 3. 适合高位数的DAC设计。 |

| 缺点 | 1. 高位电阻值极大,难以匹配。 2. 位数增加时精度下降显著。 | 1. 结构较复杂。 2. 对电阻匹配精度要求高(需激光修调或精密工艺)。 |

权(weight):数字量的每个数位所代表的值。如8位二进制数的最低位的权为20=1,最高位的权为27=128 数字量转换成模拟量(D/A conversion):把每一位上的代码按其权的大小转换成相应的模拟量,再把代表各位的模拟量相加。