从零开始讲DDR(9)——AXI 接口MIG 使用(2)

一、前言

在之前的文章中,我们介绍了官方DDR MIG AXI接口的例程的整体框架,在本文中,我们将着重介绍例程中关于数据产生,及驱动到AXI接口的相关逻辑实现。

二、data_gen

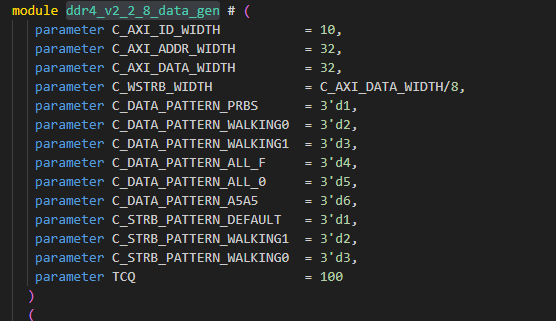

在例程中,有ddr4_v2_2_8_data_gen这样一个文件,该模块是DDR4测试系统中的数据引擎,负责生成各类测试数据模式及对应的字节使能信号(Strobe)。

首先,我们关注它的参数接口,前面的ID,ADDR,DATA和WSTRB都很好理解,不需要解释,后面提到的几个参数则对应了不同的数据模式:

parameter C_DATA_PATTERN_PRBS = 3'd1,parameter C_DATA_PATTERN_WALKING0 = 3'd2,parameter C_DATA_PATTERN_WALKING1 = 3'd3,parameter C_DATA_PATTERN_ALL_F = 3'd4,parameter C_DATA_PATTERN_ALL_0 = 3'd5,parameter C_DATA_PATTERN_A5A5 = 3'd6,parameter C_STRB_PATTERN_DEFAULT = 3'd1,parameter C_STRB_PATTERN_WALKING1 = 3'd2,parameter C_STRB_PATTERN_WALKING0 = 3'd3,2.1 数据模式

这里我们介绍一下这几种数据模式:

| 数据模式 | 值 | 功能描述 | 应用场景 |

|---|---|---|---|

| PRBS (伪随机序列) | 3'b001 | 32位LFSR生成的伪随机码,多项式为x³² + x⁷ + x⁶ + x² + 1 | 模拟真实数据流,测试时序容限和误码率 |

| WALKING0 | 3'b010 | 初始值为32'hFFFF_FFFE,每次左移1位 (如: FFFE → FFFC → FFF8...) | 测试数据线对单bit错误的敏感度 |

| WALKING1 | 3'b011 | 初始值为32'h0000_0001,每次左移1位 (如: 0001 → 0002 → 0004...) | 检测数据线开路/短路故障 |

| ALL_F (全1) | 3'b100 | 恒定输出32'hFFFF_FFFF | 测试电源完整性(最大电流负载) |

| ALL_0 (全0) | 3'b101 | 恒定输出32'h0000_0000 | 测试信号完整性(最小电流负载) |

| A5A5 (交替模式) | 3'b110 | 固定输出32'h5A5A_A5A5 (01011010/10100101交替) | 背景模式测试,特别用于检测相邻位干扰(ISI) |

Strobe(wstrb)是AXI协议的字节使能信号,每个bit对应数据总线的一个字节(8bit)的有效性。该模块支持三种生成模式:

| Strobe模式 | 值 | 功能描述 | 二进制示例(AXI 64bit) |

|---|---|---|---|

| DEFAULT (默认) | 3'b001 | 根据size_in自动填充有效字节段,如size=4B时生成4个连续1 | |

| WALKING1 | 3'b010 | 每次只有一个字节为1,依次左移 (模拟单字节写入) | 00000001 → 00000010 → 00000100... |

| WALKING0 | 3'b011 | DEFAULT模式的反相,用于测试未使能字节的容错能力 | size=2B: 11111100 → 11110011 → 11001111... |

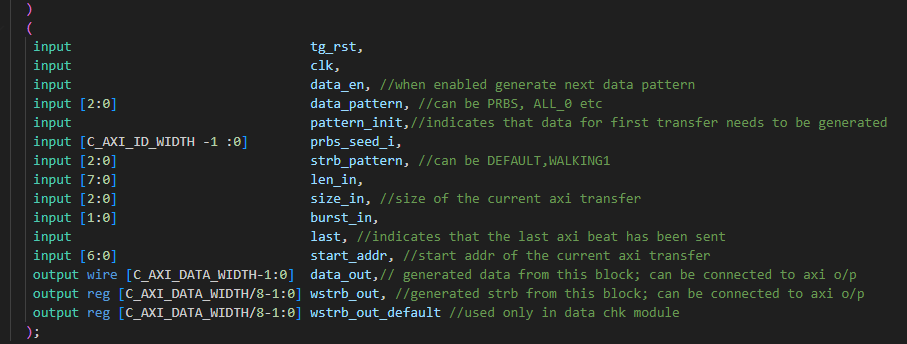

2.2 接口信号

接下来我们关注这个模块的输入输出接口,从而判断这个模块的基本功能,简单说就是,用户输入数据模式,传输大小和传输初地址等相关配置信息,本模块可以根据不同的需求,给出用户需要的测试数据,字节使能信号。

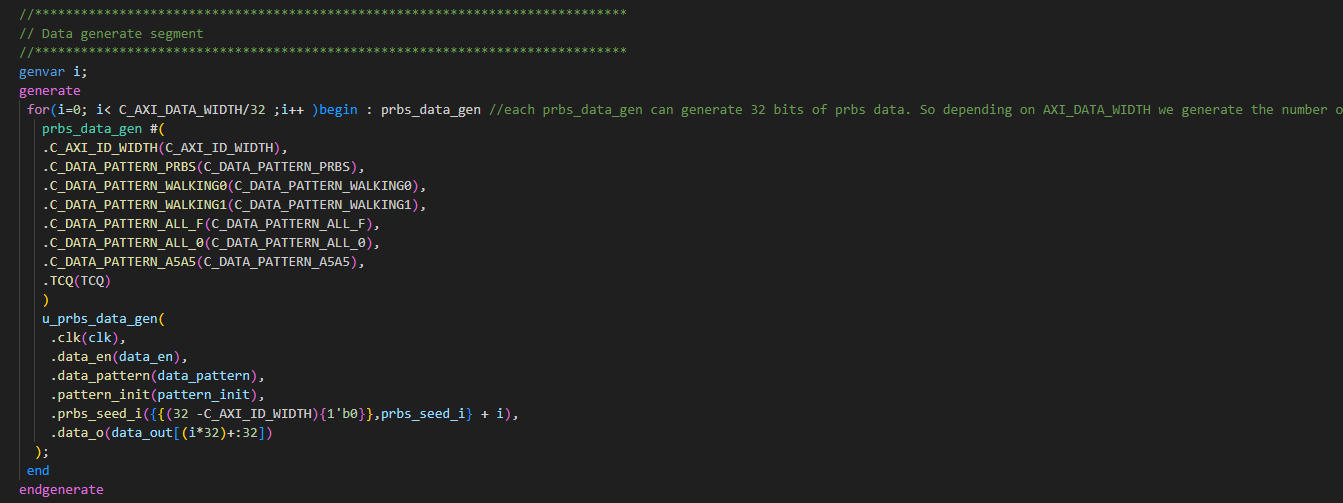

2.3 数据生成

这段Verilog代码实现了一个可配置宽度的伪随机数据生成器,它通过`generate for`循环动态生成多个32位PRBS(伪随机二进制序列)模块实例,每个实例使用不同的初始化种子(`原始种子 + 实例序号i`),并将各实例的32位输出按顺序拼接成最终的总线宽度数据(如64/128/256位),从而支持灵活的AXI总线位宽适配。模块通过传递统一的数据模式常量(如PRBS、A5A5等)确保多实例行为一致性,同时利用种子差异化确保宽总线数据的各段伪随机序列不重复,满足DDR4测试中对数据多样性和位宽可扩展性的要求。

2.4 AXI总线写选通信号(wstrb)生成

剩下部分的Verilog代码实现了一个动态可配置的AXI总线写选通信号(wstrb)生成器,主要功能是根据AXI传输的数据宽度(size)、起始地址对齐情况和选通模式(strb_pattern),实时生成精确的字节使能掩码,支持三种工作模式:

- DEFAULT模式:根据数据宽度自动生成连续低位为1的掩码(例如8字节数据对应

0xFF),并在多拍传输时循环左移,适用于常规的连续数据写入。- WALKING1模式:单bit轮转测试(

0x1→0x2→0x4→...),适合验证物理存储的bit级正确性。- WALKING0模式:生成带缺口的掩码(如8字节数据对应

0xFE),用于测试非全掩码写入时存储器的行为。

此外,该模块支持非对齐地址补偿,可根据地址偏移对掩码进行动态移位,并处理AXI Wrap突发传输的地址回绕,确保选通信号始终匹配实际数据位置。所有计算均采用流水线设计,保证在单时钟周期内完成,适用于高性能总线场景。

三、data_chk

该模块是一个AXI总线读数据比较器,主要用于比对实际读取的数据(rdata)与预期数据(expected_data)是否一致,并在出错时报告详细错误信息。

其内部首先例化了一个ddr4_v2_2_8_data_gen用来生成测试所需的数据,之后例化了数据对齐流水线:将数据生成器输出和AXI读取数据同步到同一时钟域,并补偿模块间处理延迟。然后核心的比较逻辑在于:

always @(posedge clk) beginexpected_data_pri <= #TCQ (data_o_pri_r & wstrb_out_pri_full);actual_data_pri <= #TCQ (rdata_r & wstrb_out_pri_full);expected_data_bg <= #TCQ (data_o_bg_r & (wstrb_out_bg_full ^ wstrb_out_pri_full));actual_data_bg <= #TCQ (rdata_r & (wstrb_out_bg_full ^ wstrb_out_pri_full));mismatch_pri <= #TCQ expected_data_pri^actual_data_pri;mismatch_bg <= #TCQ expected_data_bg^actual_data_bg;mismatch <= #TCQ (compare_bg_r)? (|(mismatch_pri | mismatch_bg)) : (|mismatch_pri);

end- 主数据路径:通过掩码过滤有效数据位,按bit对比差异。

- 背景路径:当

compare_bg使能时,检查未被主掩码覆盖的区域是否符合背景模式。

四、axi_wrapper

该模块的功能是作为AXI4协议转换的桥梁,将测试指令(如PRBS、固定模式数据)转换为符合AXI4协议的读写事务,并完成数据校验。内部例化了data_gen来生成测试写数据,并根据协议要求,将数据驱动到写数据总线和写地址总线上,同时,内部还例化了data_chk,将读数据总线上获取的数据,输入到data_chk,实现测试结果的自动化比对。

五、opcode_gen

该模块是AXI总线事务生成器,负责:

- 指令转换:将上层测试指令(如PRBS、固定模式等)转换为AXI协议的读写操作。

- 地址对齐处理:根据

instr_axi_size动态计算对齐后的地址(aligned_addr)。- ECC支持:检测和纠正内存错误(通过

ECC参数配置)。- 数据校验:比对写入数据与读取数据,检测内存或总线错误。

其核心的操作逻辑如下:

输入指令 → 状态机控制 → AXI协议转换 → 物理层交互 → 数据校验 → 错误定位 ddr4_v2_2_8_axi_opcode_gen 是一个专门用于 DDR4 控制器测试的 AXI4 事务生成模块,负责将测试指令(如 PRBS、固定模式等)转换为符合 AXI4 协议的突发读写操作,并支持 ECC 检查、错误定位和调试。并将产生的axi opcode传递到axi_wrapper中,进行进一步的处理。