通信协议——SPI通信协议

一、SPI 协议简介

SPI(Serial Peripheral interface,串行外围设备接口) 通信协议是 Motorola 公司首先在其MC68HCXX 系列处理器上定义的。SPI 接口是一种高速的全双工同步的通信总线,已经广泛应用在众多 MCU、存储芯片、AD 转换器和 LCD 之间。

| 功能说明 | SPI 总线 | IIC 总线 |

| 通信方式 | 同步 串行 全双工 | 同步 串行 半双工 |

| 总线接口 | MOSI、MISO、SCL、CS | SDA、SCL |

| 拓扑结构 | 一主多从/一主一从 | 多主从 |

| 从机选择 | 片选引脚选择 | SDA上设备地址片选 |

| 通信速率 | 一般50MHz以下 | 100kHz、400kHz、3.4MHz |

| 数据格式 | 8位/16位 | 8位 |

| 传输顺序 | MSB/LSB | MSB |

二、SPI 协议应用

SPI 广泛用于连接高速外围设备,如:

- 数据存储设备(SD卡、闪存)

- 显示屏(LCD、OLED)

- 传感器(加速度计、陀螺仪)

- 数模转换器(DAC)和模数转换器(ADC)

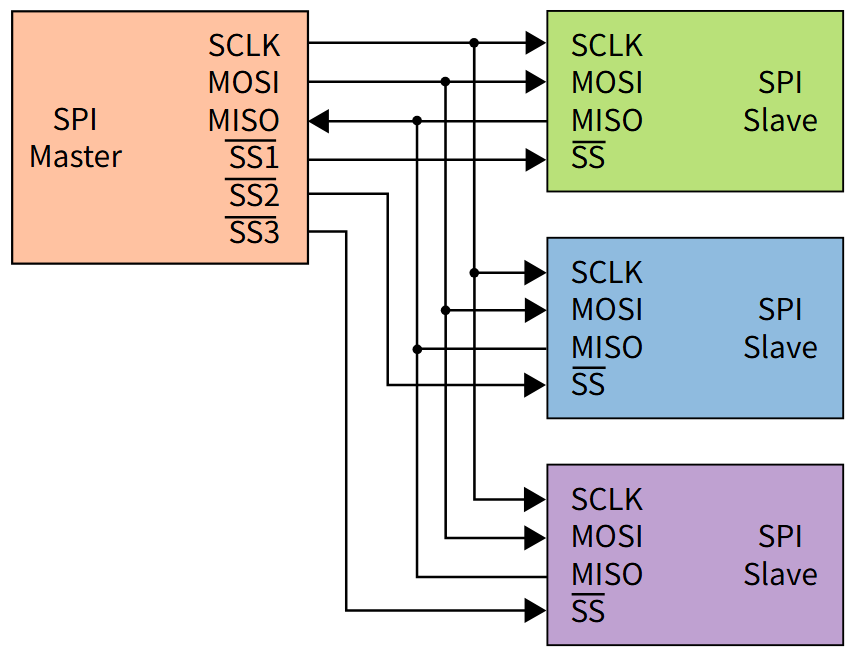

三、SPI 协议接口

MISO(Master In / Slave Out)主设备数据输入,从设备数据输出。

MOSI(Master Out / Slave In)主设备数据输出,从设备数据输入。

SCLK(Serial Clock)时钟信号,由主设备产生。

CS(Chip Select)从设备片选信号,由主设备产生。

四、SPI 协议四种工作模式

主从设备 必须使用相同的工作模式——SCLK、CPOL 和 CPHA,才能正常工作。如果有多个 从设备,并且它们使用了不同的工作模式,那么 主设备 必须在读写不同 从设备 时需要重新修改对应从设备的模式。以上SPI总线协议的主要内容。

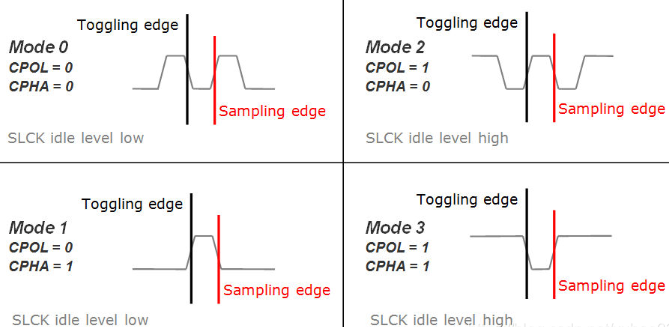

1. CPOL

CPOL(Clock Polarity),就是时钟的极性。通信的整个过程分为空闲时刻和通信时刻,如果SCLK在数据发送之前和之后的空闲状态是高电平,那么就是CPOL=1;如果空闲状态SCLK是低电平,那么就是 CPOL=0。

时钟相位(CPHA)定义数据的采集时间:

2. CPHA

CPHA(Clock Phase),就是时钟的相位。同步通信的一个特点就是所有数据的变化和采样都是伴随着时钟沿进行的,也就是说数据总是在时钟的边沿附近变化或被采样。而一个时钟周期必定包含了一个上升沿和一个下降沿。这里将结束空闲状态之后的第一个边沿当作奇数边沿,第二个边沿当作偶数边沿,以此类推,奇偶交替

CPHA=0,在时钟的第一个跳变沿(上升沿或下降沿)进行数据采样,在第2个边沿发送数据

CPHA=1,在时钟的第二个跳变沿(上升沿或下降沿)进行数据采样,在第1个边沿发送数据

3. 工作模式

- 模式0:CPOL= 0,CPHA=0。空闲状态时 SCLK 串行时钟为低电平;数据采样在 SCLK 时钟的奇数边沿,本模式中,奇数边沿为上升沿;数据更新在 SCLK 时钟的偶数边沿,本模式中,偶数边沿为下降沿。

- 模式1:CPOL= 0,CPHA=1。空闲状态时 SCK 串行时钟为低电平;数据采样在 SCLK 时钟的偶数边沿,本模式中,偶数边沿为下降沿;数据更新在 SCLK 时钟的奇数边沿,本模式中,偶数边沿为上升沿。

- 模式2:CPOL= 1,CPHA=0。空闲状态时 SCLK 串行时钟为高电平;数据采样在 SCLK 时钟的奇数边沿,本模式中,奇数边沿为下降沿;数据更新在 SCLK 时钟的偶数边沿,本模式中,偶数边沿为上升沿。

- 模式3:CPOL= 1,CPHA=1。空闲状态时 SCLK 串行时钟为高电平;数据采样在 SCLK 时钟的偶数边沿,本模式中,偶数边沿为上升沿;数据更新在 SCLK 时钟的奇数边沿,本模式中,偶数边沿为下降沿。

注:理解成 CPOL 同或 CPHA 等于 1 时,SPI 通信在 SCLK 的上升沿采样数据,下降沿发送数据,反之同理。

| 模式 | 采样数据时钟边沿 | 发送数据时钟边沿 |

| CPOL= 0,CPHA=0 | 上升沿 | 下降沿 |

| CPOL= 0,CPHA=1 | 下降沿 | 上升沿 |

| CPOL= 1,CPHA=0 | 下降沿 | 上升沿 |

| CPOL= 1,CPHA=1 | 上升沿 | 下降沿 |