使用DDR4控制器实现多通道数据读写(十)

一、本章概述

本章节对目前单通道的读写功能进项测试,主要验证读写的数据是否正确,并观察该工程可以存储的最大容量。通过空满信号进行读写测试,根据ila抓取fifo和ddr4全部满的时刻,可以观察到最大容量。再通过debug逻辑可以测试读写数据是否正确。

二、DDR4循环读写功能测试

我们实现的功能是,只要fifo_1不满就可以往里存入数据,fifo_2不空就可以读出数据。所以只要根据fifo_1的几乎满(wrfifo_almost_full)信号为低电平状态就可以控制数据写入,根据fifo_2d的空(rdfifo_empty)信号为低电平状态就可以控制数据输出。

1、写入数据测试代码:

module generate_data(

input wire wr_clk,

input wire rst,

input wire wrfifo_almost_full,

input wire full,

output wire [255:0] wdata_in,

output reg wdata_en

);

reg [26:0] data_cnt;

wire rst_1;

always @(posedge wr_clk ) begin

if(rst) begin

data_cnt <= 0;

end

else if (data_cnt == 'h2000401 && wdata_en1) begin

data_cnt <= 0;

end

else if ( wdata_en1) begin

data_cnt <= data_cnt + 1;

end

end

always @(posedge wr_clk ) begin

if(rst) begin

wdata_en <= 1’b0;

end

else if ( wrfifo_almost_full == 1) begin

wdata_en <= 1’b0;

end

else if (rst_10) begin

wdata_en <= 1’b0;

end

else if (!wrfifo_almost_full && rst_11) begin

wdata_en <= 1’b1;

end

end

assign wdata_in = data_cnt;

vio_0 vio_0_inst (

.clk(wr_clk), // input wire clk

.probe_out0(rst_1) // output wire [0 : 0] probe_out0

);

endmodule

通过vio控制何时写入数据,在写入数据时, full如果拉高,证明fifo_1、fifo_2、ddr都已经写满。

2、读出数据测试代码

module data_out(

input wire rd_clk,

input wire rst,

input wire rd_fifo_empty,

input wire rdfifo_almost_empty,

input wire empty,

input wire [255:0] rdata_out,

output reg rdata_en

);

wire read_1;

reg read_start;

reg [26:0] rd_data_cnt;

reg error;

reg error_1;

always @(posedge rd_clk ) begin

if(rst) begin

read_start <= 0;

end

else begin

read_start <= read_1;

end

end

always @* begin

if(rst) begin

rdata_en <= 1’b0;

end

else if (!rd_fifo_empty && read_start==1) begin

rdata_en <= 1’b1;

end

else begin

rdata_en <= 1’b0;

end

end

always @(posedge rd_clk ) begin

if(rst) begin

rd_data_cnt <= 0;

end

else if (rd_data_cnt == 'h2000401 && rdata_en == 1) begin

rd_data_cnt <= 0;

end

else if (rdata_en == 1) begin

rd_data_cnt <= rd_data_cnt +1;

end

end

always @* begin

if(rst) begin

error <= 0;

end

else if (rdata_en == 1) begin

if (rd_data_cnt == rdata_out) begin

error <= 0;

end

else if (rd_data_cnt != rdata_out) begin

error <= 1;

end

else begin

error <= 0;

end

end

end

always @(posedge rd_clk ) begin

if(rst) begin

error_1 <= 0;

end

else if (error == 1 && rdata_en == 1) begin

error_1 <= 1;

end

else begin

error_1 <= 0;

end

end

vio_read vio_read_inst (

.clk(rd_clk), // input wire clk

.probe_out0(read_1) // output wire [0 : 0] probe_out0

);

endmodule

通过vio控制数据何时读取,也可以通过empty的状态观察到fifo_1、fifo_2、ddr中是否含有数据。如果写入的数据和读取的数据不相同,error_1就会拉高,可以通过error_1的状态判断ddr循环读写的功能是否正确。

三、上板验证过程

将板卡上电并烧入bit文件与ltx文件。

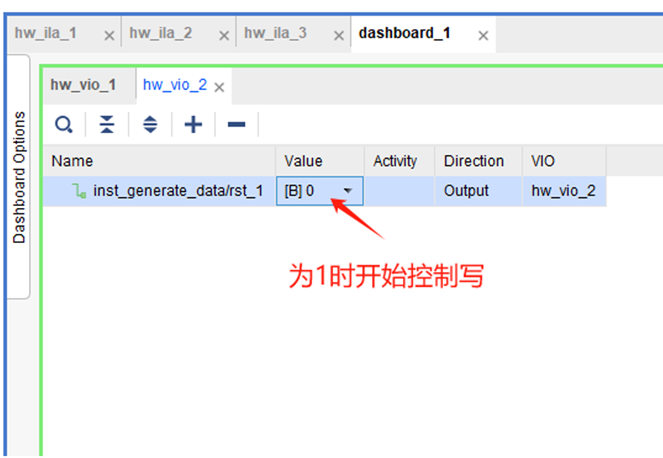

上图中vio_2控制何时开始写入,为1时开始写入递增数据。

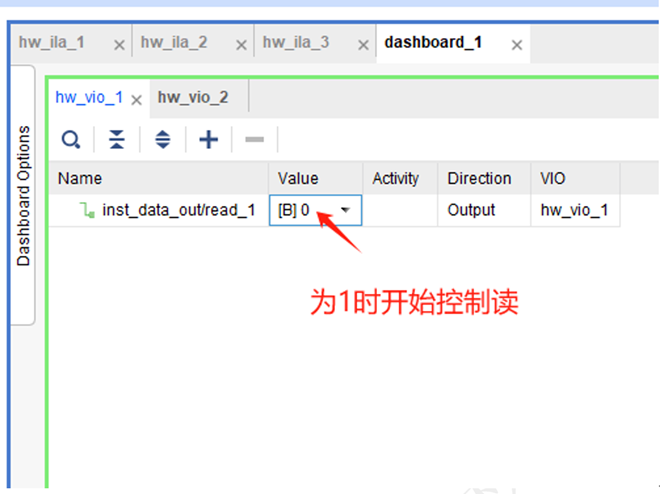

上图中vio_1控制何时开始读数据,为1时开始读出数据。

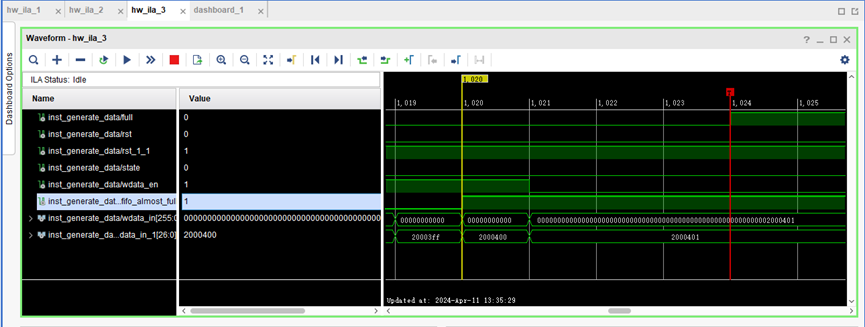

测试时,首先vio_2控制rst_1拉高,抓取数据存满的时刻。

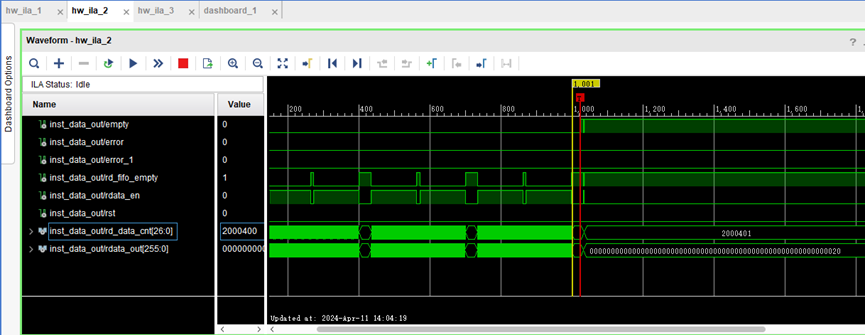

上图中,红线位置为写入数据后,fifo_1,fifo_2和ddr4全部存满数据的时刻。之后,拉低rst_1,再控制vio_1拉高read_1,抓取数据读取完的时刻。

上图中,可以看到,读出的数据数量和存入的数据数量相等,并且可以观察到,测试工程中可以存储的数据数量为ddr4的最大存储量加上两个fifo的存储量。

本文章由威三学社出品

对课程感兴趣可以私信联系