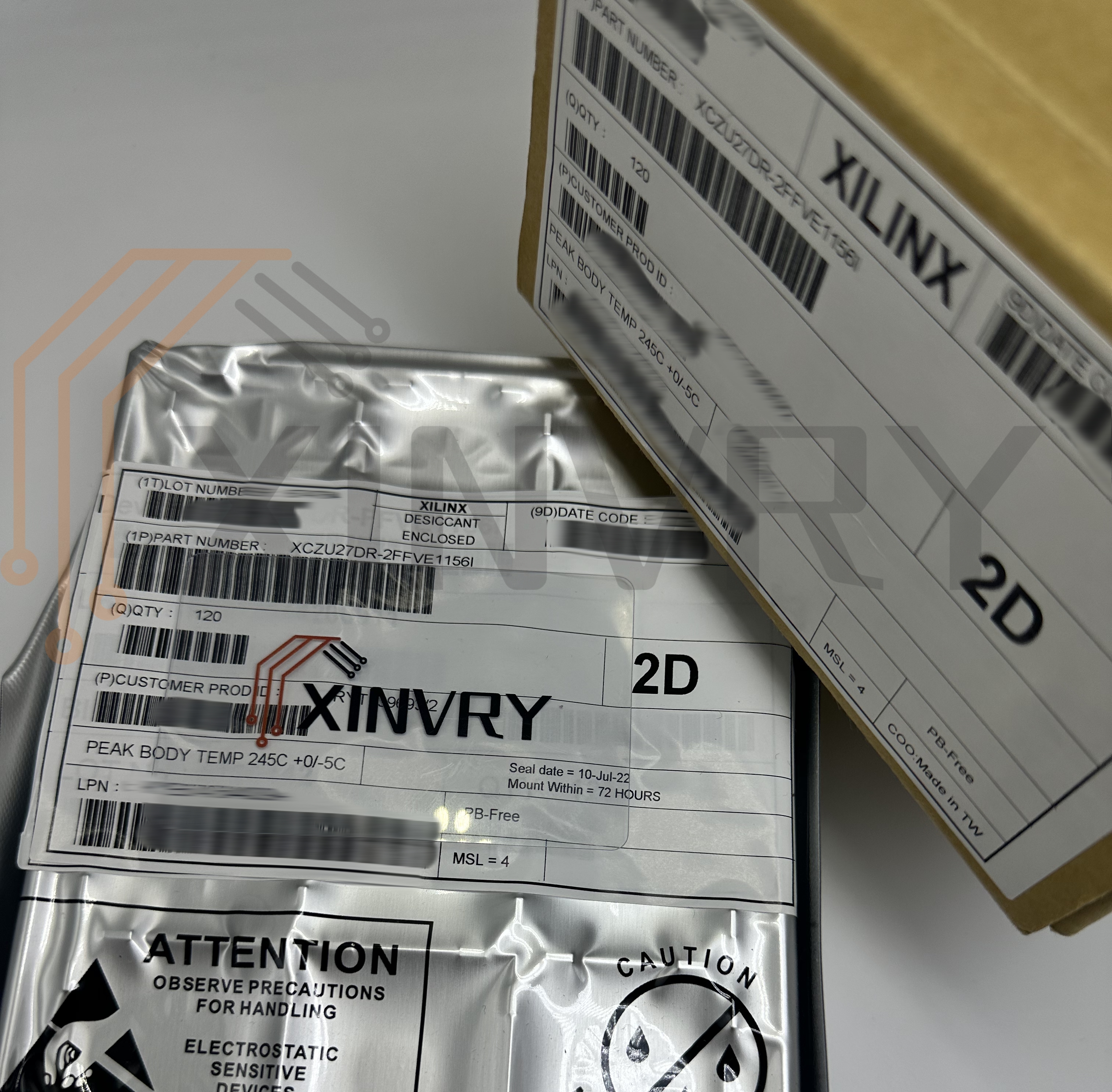

XCZU27DR‑2FFVE1156I Xilinx Zynq UltraScale+ RFSoC

一、概述

XCZU27DR‑2FFVE1156I 属于 Zynq® UltraScale+™ RFSoC Gen 2 系列,采用 TSMC 16 nm FinFET+ 工艺,Speed Grade ‑2,集成了 ARM 处理系统、可编程逻辑与高性能射频数据转换单元,为软件定义无线电、5G 前端、测试测量等场景提供单芯片解决方案。

二、处理系统 (PS)

-

应用处理器 (APU):4× Arm® Cortex‑A53 MPCore™,NEON SIMD + 单/双精度 FPU,32 KB I‑Cache + 32 KB D‑Cache,1 MB L2 Cache,最高 1.5 GHz。

-

实时处理器 (RPU):2× Arm® Cortex‑R5F,32 KB I‑Cache + 32 KB D‑Cache + 256 KB TCM,最高 533 MHz。

-

片上内存:256 KB ECC TCM;外部支持 DDR4/DDR3/LPDDR4/LPDDR3、Quad‑SPI、NAND、eMMC;

-

高性能外设:4 × PS‑GTR (最高 6.0 Gb/s);PCIe® Gen1/2;Serial ATA 3.1;DisplayPort 1.2a;USB 3.0;SGMII;

-

通用外设:214 路 PS I/O;UART、CAN 2.0B、USB 2.0 OTG、I²C、SPI、32‑bit GPIO、RTC、看门狗、三定时器等;

-

系统监控:1× 片上电源/温度监控,可扩展 17 路外部 ADC。

三、射频数据转换子系统

-

12‑bit RF‑ADC w/ DDC:8 通道,最高 4.096 GSPS;

-

14‑bit RF‑DAC w/ DUC:8 通道,最高 6.554 GSPS;

-

数字前端:内置 DDC/DUC 引擎,支持可编程插值/抽取、NCO、复数混频,多频带双模式操作;

-

软判决 FEC (SD‑FEC):无硬件加速模块 (Gen 2 设备此项为 0);

-

应用场景:4G/5G 基带、DOCSIS 回程、雷达、软件无线电。

四、可编程逻辑 (PL)

-

系统逻辑单元:930 300 LE;

-

CLB 结构:425 280× 6‑输入 LUT + 850 560 Flip‑Flop;

-

分布式 RAM:13.0 Mb (LUT‑RAM);

-

Block RAM:38.0 Mb (1 080 × 36 Kb 块);

-

UltraRAM:22.5 Mb (80 × 288 Kb 块);

-

DSP 切片:4 272 × DSP48E2 (27×18 位乘加块,96 位 XOR,27 位预加器);

-

时钟管理 (CMT):8× MMCM/PLL;

-

系统监控单元:1×;

-

安全特性:CSU 安全引导 (AES‑GCM、SHA‑384)、软错误恢复。

五、高速收发器与 I/O

-

GTY 收发器:16 × 最高 32.75 Gb/s,支持 PCIe Gen3/Gen4、100 G Ethernet、Interlaken 等;

-

PS‑GTR:4 对,最高 6 Gb/s;

-

I/O 引脚:

-

PS I/O:214;

-

HPIO (高性能 I/O):299;

-

HDIO (高密度 I/O):48;

-

-

每种封装下资源:

-

FFVE1156(35×35 mm, 0.8 mm 球距):214 PSIO, 48 HDIO, 104 HPIO; 4 PS‑GTR, 8 GTY, 8 ADC, 8 DAC。

-

六、电源 & 封装

-

核心电压 (VCCINT):0.825 – 0.876 V (典型 0.850 V);

-

I/O 电压 (VCCO):1.14 – 3.3 V(独立银行配置);

-

工作温度:–40 °C ~ 100 °C (TJ);

-

封装形式:1156‑球 FCBGA (FFVE1156),35 × 35 × 4.5 mm,MSL 3/4。