FPGA状态机思想实现流水灯及HDLBits学习

目录

- 第一章 在DE2-115上用状态机思想实现LED流水灯

- 1.1 状态机设计思路

- 1.2 Verilog代码实现

- 1.3. 仿真测试代码

- 1.4 编译代码与仿真

- 第二章 CPLD和FPGA芯片的主要技术区别是什么?它们各适用于什么场合?

- 2.1 主要技术区别

- 2.2 适用场合

- 第三章 HDLBits学习

- 3.1四位右移寄存器

- 3.2 半加器

- 3.3 全加器

- 3.4 线材

- 3.5 与门

- 参考资料

第一章 在DE2-115上用状态机思想实现LED流水灯

1.1 状态机设计思路

- 状态定义:定义多个状态,每个状态对应一个LED亮起。

- 状态转移:按顺序从一个状态转移到下一个状态。

- 计数器:用于控制每个状态的持续时间。

1.2 Verilog代码实现

- 环境配置

- 代码

module led_fsm(

input wire clk, // 时钟信号

input wire reset, // 复位信号

output reg [7:0] leds // 8个LED输出

);

// 定义状态

parameter STATE0 = 3'b000;

parameter STATE1 = 3'b001;

parameter STATE2 = 3'b010;

parameter STATE3 = 3'b011;

parameter STATE4 = 3'b100;

parameter STATE5 = 3'b101;

parameter STATE6 = 3'b110;

parameter STATE7 = 3'b111;

reg [2:0] current_state, next_state;

// 计数器,用于控制每个状态的持续时间

reg [25:0] cnt;

always @(posedge clk or posedge reset) begin

if (reset) begin

current_state <= STATE0;

cnt <= 0;

end else begin

if (cnt == 25'd10000000) begin // 每个状态持续约1秒(假设时钟为50MHz)

cnt <= 0;

current_state <= next_state;

end else begin

cnt <= cnt + 1;

end

end

end

always @(*) begin

case (current_state)

STATE0: begin

leds = 8'b00000001;

next_state = STATE1;

end

STATE1: begin

leds = 8'b00000010;

next_state = STATE2;

end

STATE2: begin

leds = 8'b00000100;

next_state = STATE3;

end

STATE3: begin

leds = 8'b00001000;

next_state = STATE4;

end

STATE4: begin

leds = 8'b00010000;

next_state = STATE5;

end

STATE5: begin

leds = 8'b00100000;

next_state = STATE6;

end

STATE6: begin

leds = 8'b01000000;

next_state = STATE7;

end

STATE7: begin

leds = 8'b10000000;

next_state = STATE0;

end

default: begin

leds = 8'b00000001;

next_state = STATE1;

end

endcase

end

endmodule

1.3. 仿真测试代码

module tb_led_fsm;

// 时钟和复位信号

reg clk;

reg reset;

wire [7:0] leds;

// 实例化被测试模块

led_fsm uut (

.clk(clk),

.reset(reset),

.leds(leds)

);

// 时钟生成

initial begin

clk = 0;

forever #10 clk = ~clk;

end

// 测试过程

initial begin

reset = 1;

#20 reset = 0;

#10000 $stop;

end

endmodule

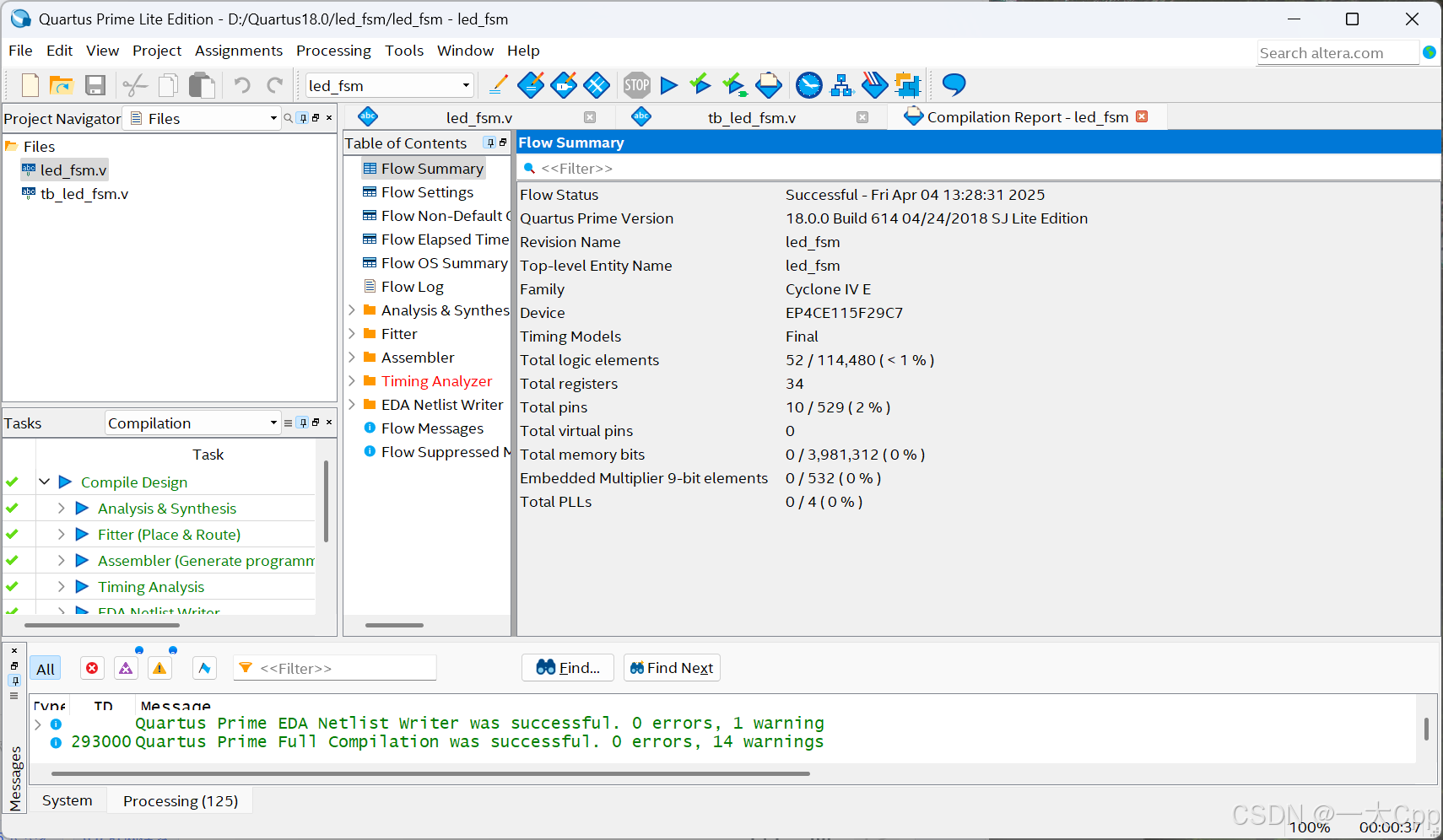

1.4 编译代码与仿真

-

编译

led_fsm.v

-

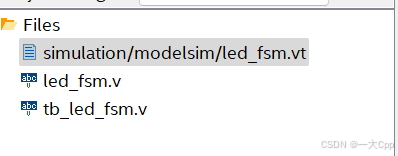

点击

Processing–>Start–>Start test bench template writer,并在flie中添加生成的led_fsm.vt文件

-

修改led_fsm.vt文件内容

把仿真代码copy到该文件内,并在第一行声明时间扫描间隔

-

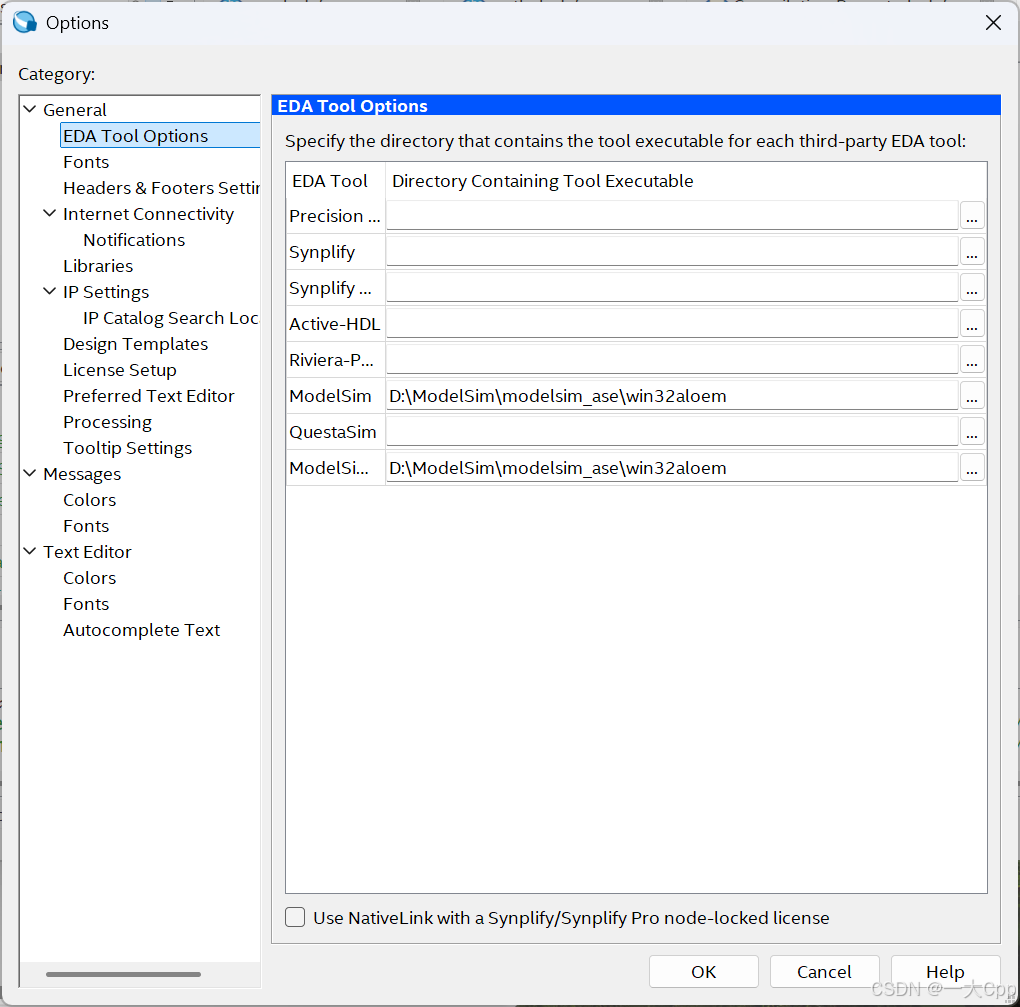

配置仿真环境

点击Tools–>Options–>EDA ToolsOptions选项,配置ModelSim环境,如果Modelsim版本为INTEL FPGA Edition,那么文件地址应为安装文件内........\modelsim_ase\win32aloem,如图所示。

-

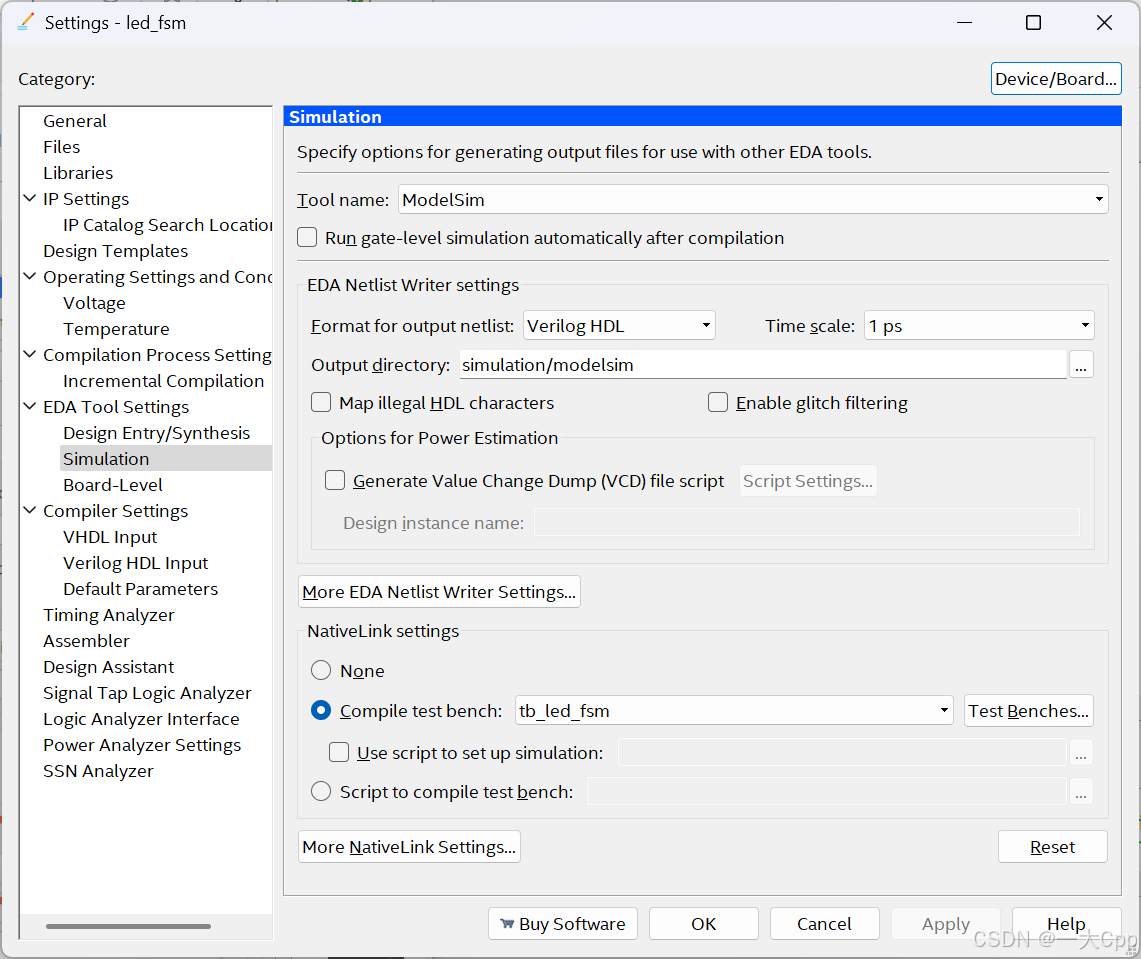

配置仿真文件,点击

Assignments–>Settings

-

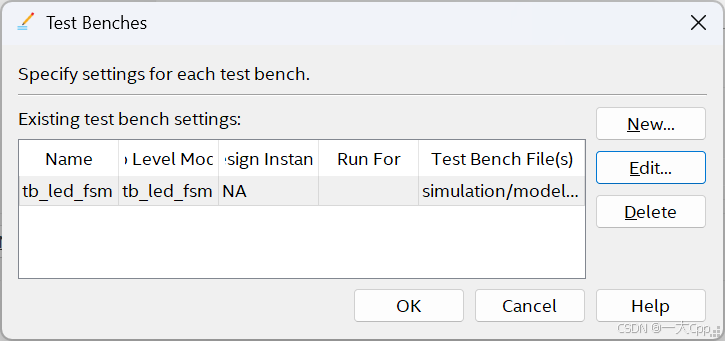

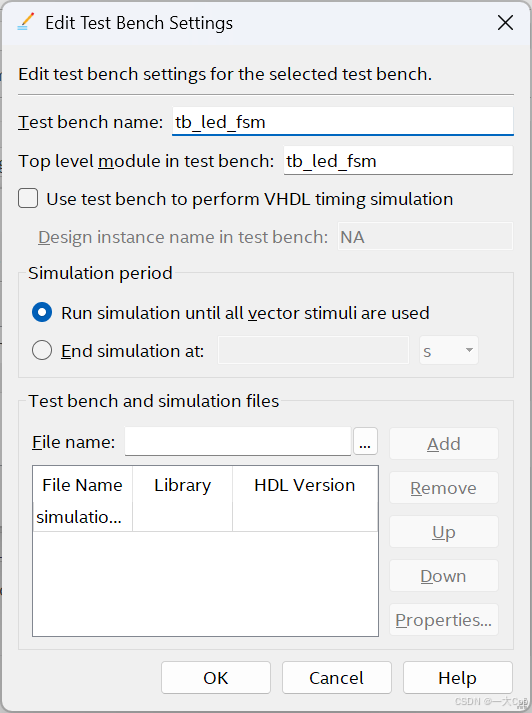

选择上面的

Compile test bench点击后面Test Bench进入选择,点击New新建

-

按照顺序先编辑名字,然后浏览刚才的.vt文件,最后点击Add添加达到如下图效果,再点击OK

-

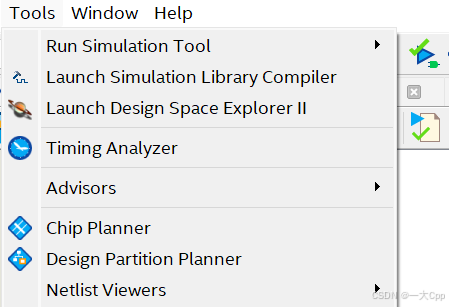

点击

Tools–>Run Simulation Tool–>RTL Simulation开始进行仿真

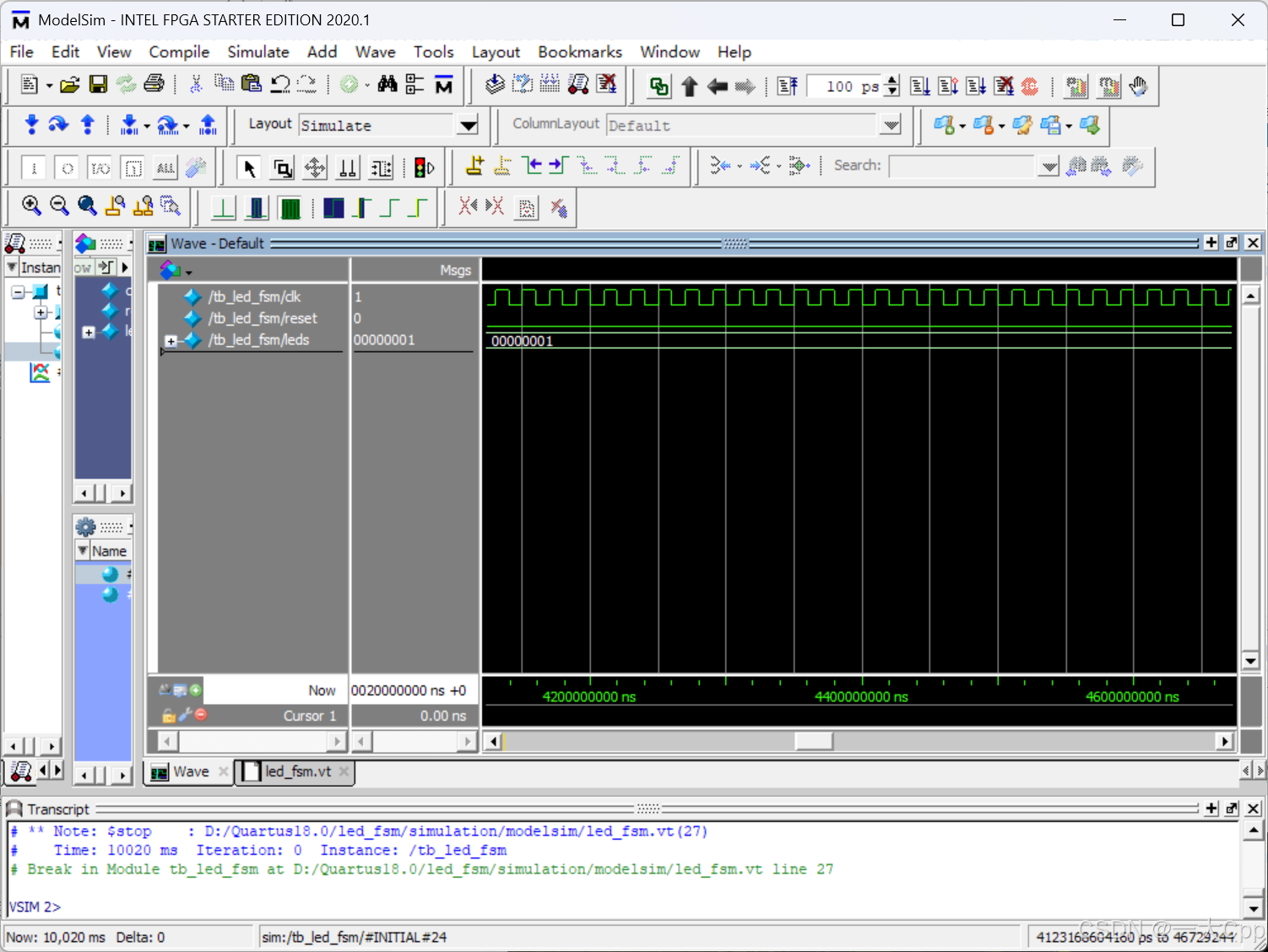

仿真结果

第二章 CPLD和FPGA芯片的主要技术区别是什么?它们各适用于什么场合?

2.1 主要技术区别

- 结构:

CPLD:基于查找表(LUT)和可编程连线的简单结构,逻辑资源较少。

FPGA:基于查找表(LUT)和可编程连线的复杂结构,逻辑资源丰富,支持大规模设计。 - 编程方式:

CPLD:通常使用一次性可编程(OTP)技术,编程后不可擦除。

FPGA:使用SRAM配置,可多次擦写和重新编程。 - 速度和性能:

CPLD:延迟较低,适合高速简单逻辑。

FPGA:延迟较高,但支持复杂的逻辑设计。 - 成本和功耗:

CPLD:成本较低,功耗较低。

FPGA:成本较高,功耗较高。

2.2 适用场合

CPLD:

- 适合简单的逻辑设计和组合逻辑。

- 适合需要低延迟和低功耗的场合。

- 适合需要一次性编程的场合。

FPGA:

- 适合复杂的逻辑设计和大规模数字系统。

- 适合需要频繁更新和调试的场合。

- 适合需要高性能计算的场合。

第三章 HDLBits学习

通过访问HDLBits以及HDLBits中文导学网站,完成组合逻辑(combinational logic)中的各题目

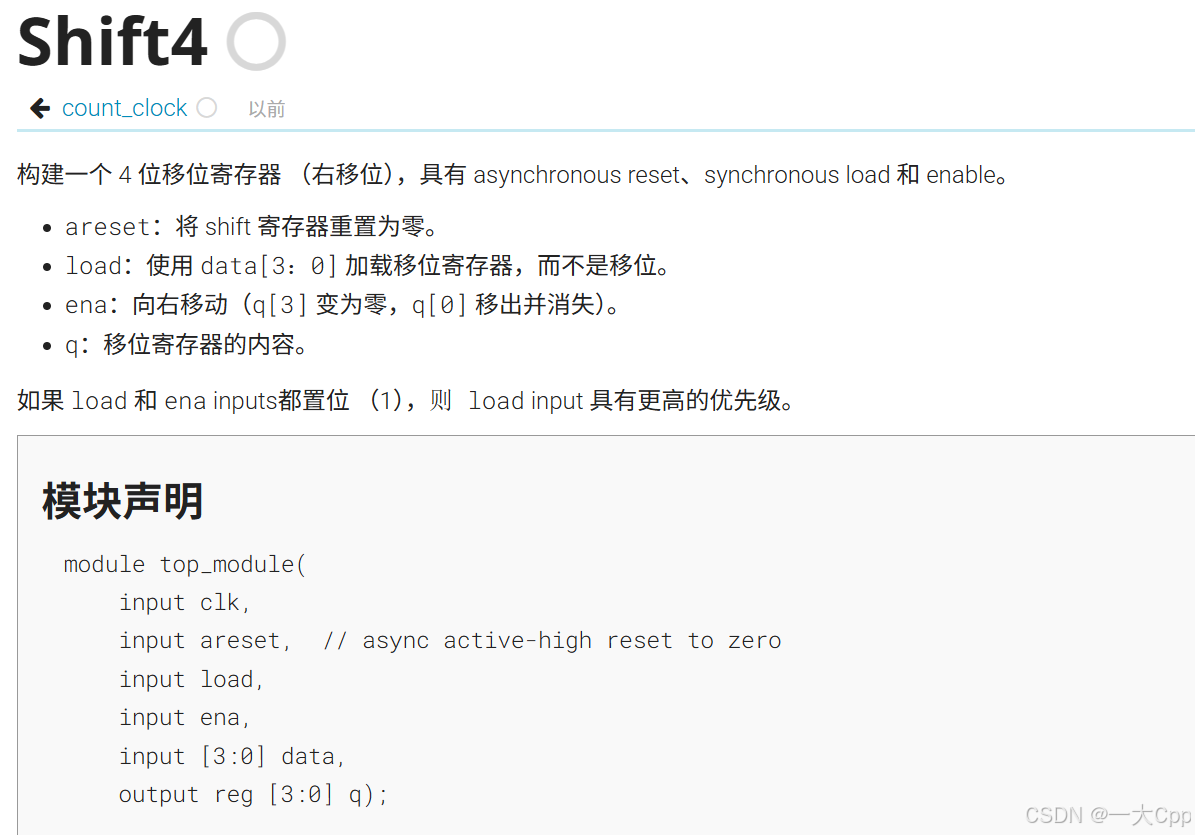

3.1四位右移寄存器

-

题目

-

代码实现

module top_module(

input clk,

input areset, // async active-high reset to zero

input load,

input ena,

input [3:0] data,

output reg [3:0] q);

// 异步复位,同步加载和移位

always @(posedge clk or posedge areset) begin

if (areset) begin

q <= 4'b0000; // 异步复位为0

end else begin

if (load) begin

q <= data; // 同步加载

end else if (ena) begin

q <= {1'b0, q[3:1]}; // 右移一位,最高位清零

end

// 如果load和ena都无效,保持当前状态

end

end

endmodule

- 提交结果

3.2 半加器

- 题目

- 代码实现

module top_module(

input a, b,

output cout, sum

);

assign sum = a ^ b;

assign cout = a & b;

endmodule

- 提交结果

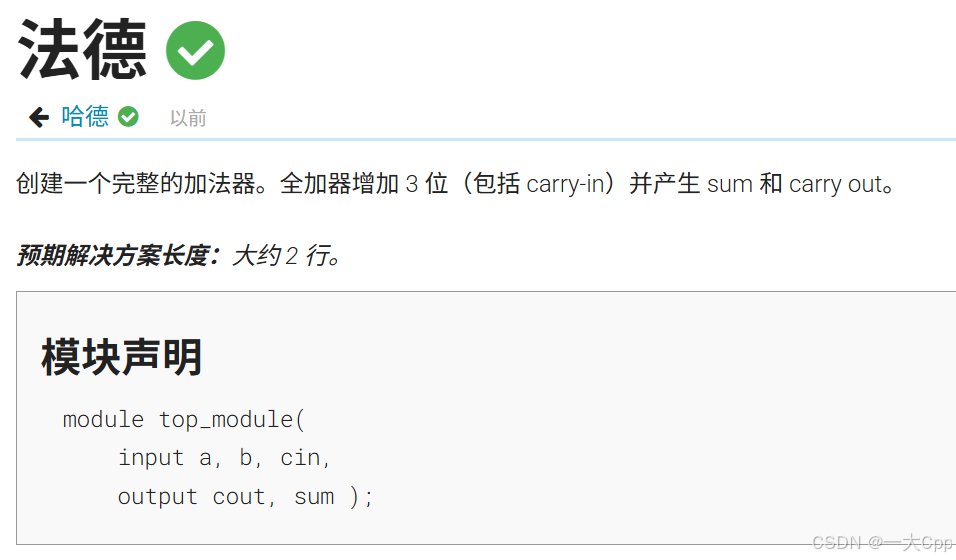

3.3 全加器

- 题目

- 代码实现

module top_module(

input a, b, cin,

output cout, sum

);

assign sum = a ^ b ^ cin;

assign cout = (a & b) | (a & cin) | (b & cin);

endmodule

- 提交结果

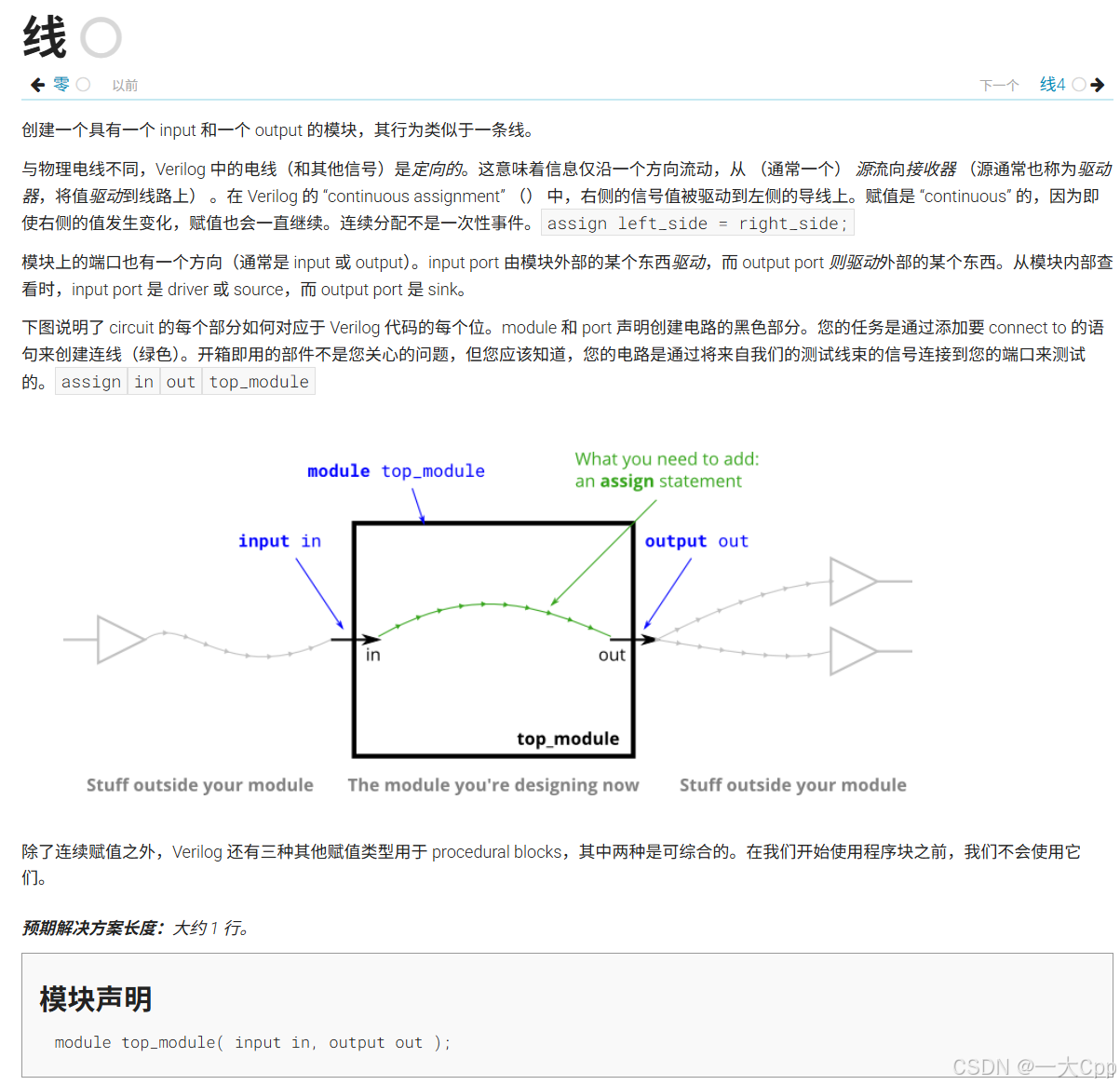

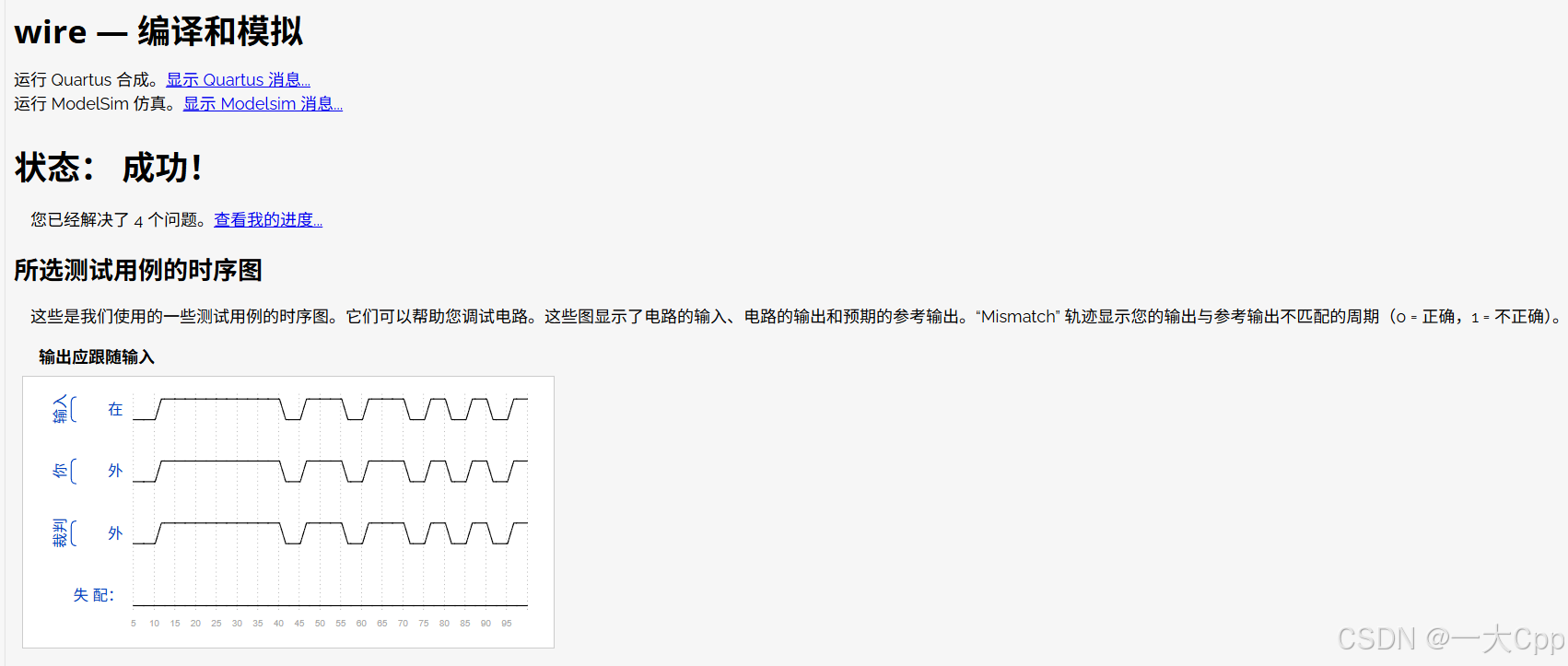

3.4 线材

- 题目

- 代码

module top_module(

input in,

output out

);

assign out = in;

endmodule

- 提交结果

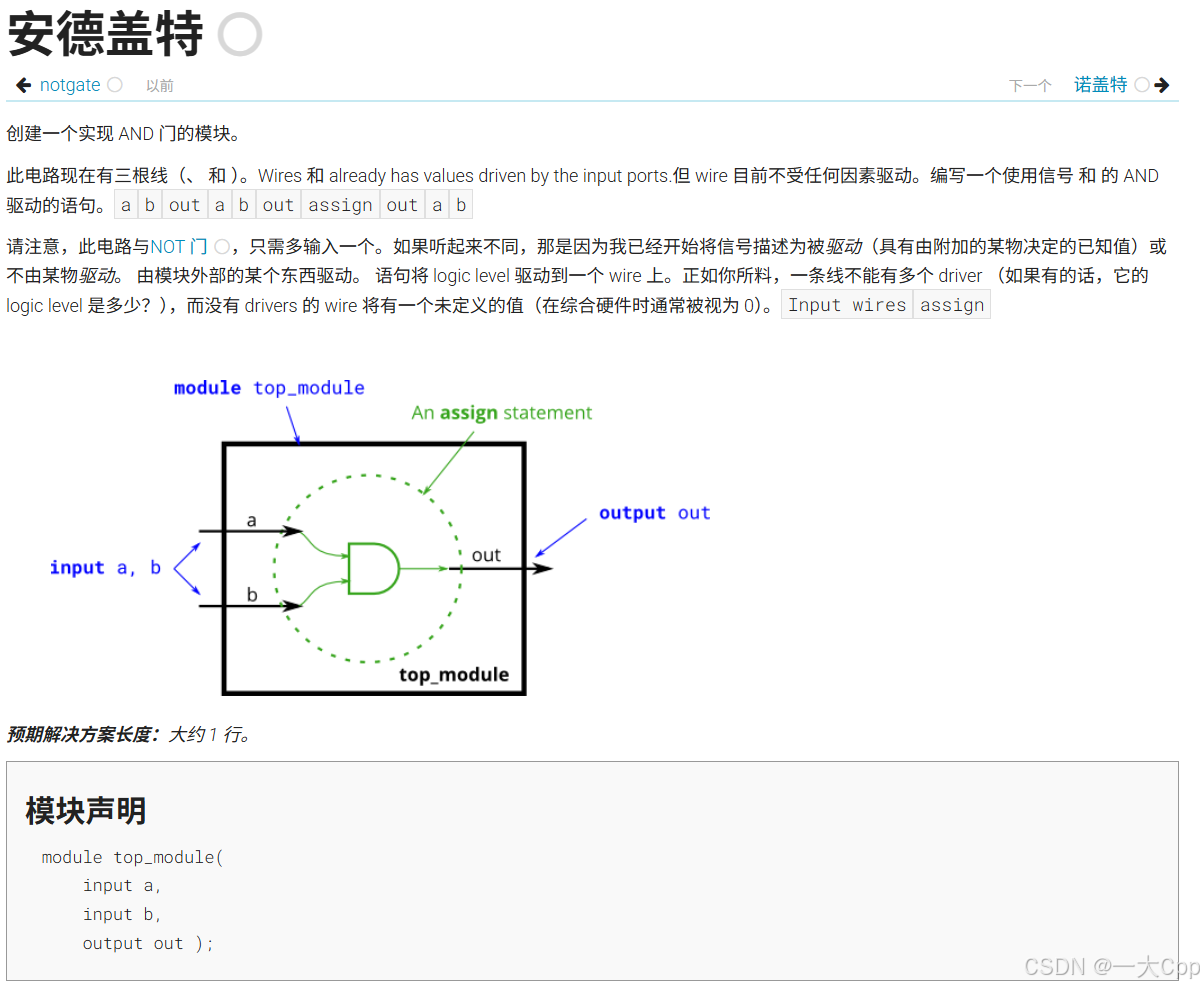

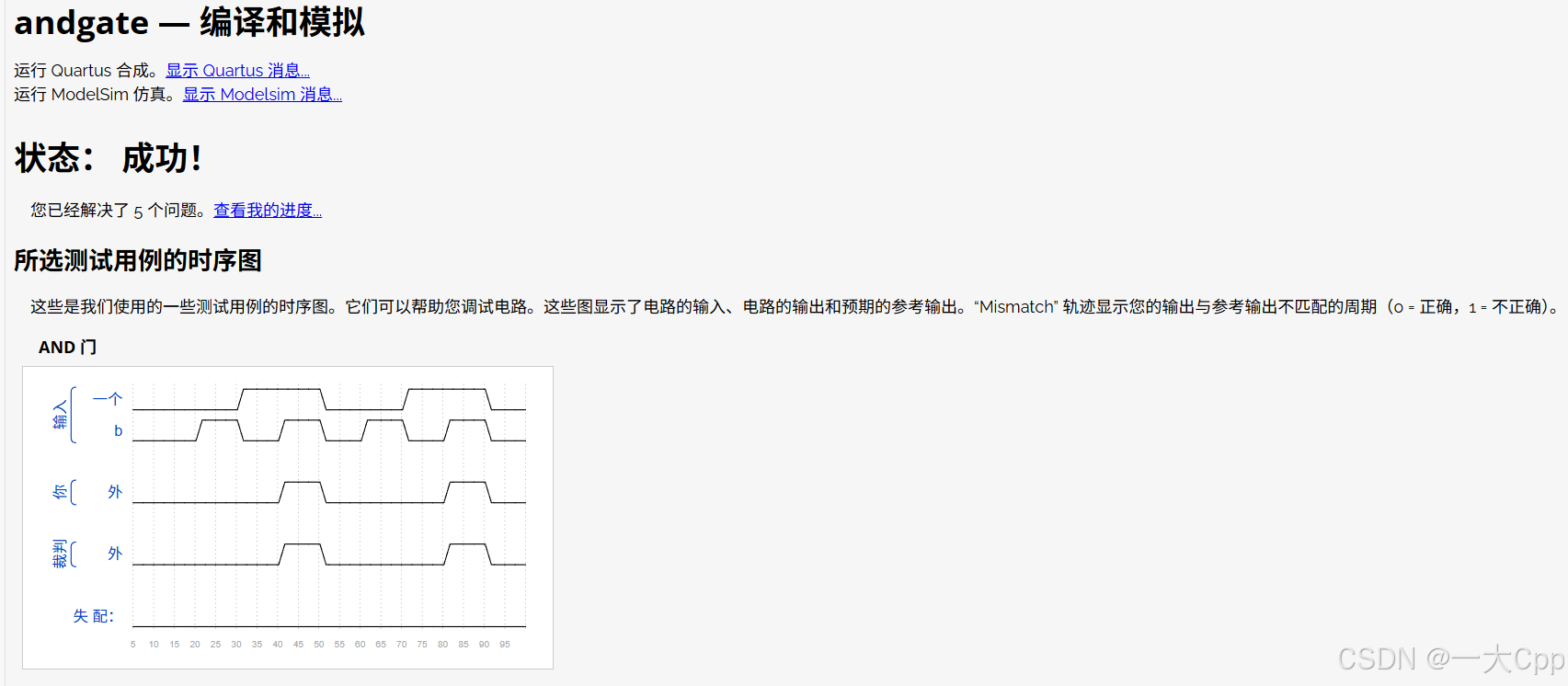

3.5 与门

- 题目

- 代码实现

module top_module(

input a,

input b,

output out

);

assign out = a & b;

endmodule

- 提交结果

参考资料

Quartus使用步骤及联合Modelsim仿真教程

FPGA基础入门【2】ModelSim官方免费版安装

quartus和modelsim联合仿真详细教程