深圳市网站建设制作设计平台常州做网站优化

实验四 图像处理实验报告

目录

- 实验目的

- 实验内容

- 原理描述

- Verilog HDL设计源代码

- Testbench仿真代码及仿真结果

- XDC文件配置

- 下板测试

- 实验体会

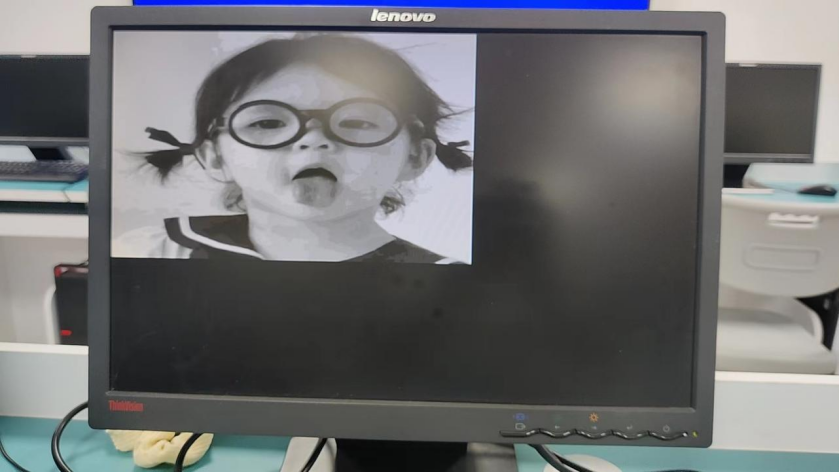

- 实验照片

实验目的

在实验三的基础上,将图片显示在显示器上,并进行灰度处理。

实验内容

原理描述

1. 图片的分辨率、尺寸和位深度

- 分辨率:每英寸内有多少个像素点(如dpi、lpi、ppi),决定了图像细节度。

- 尺寸:图片的像素长和宽,如640×480表示宽640像素、高480像素。

- 位深度:每个像素用多少位(bit)表示,如24位能表示2^24种颜色。

2. 图片数据导入方法

- 方法一:用Matlab将图片转为三维矩阵,提取RGB分量,按GRB565格式拼接,写入.coe文件。

- 方法二:用BMP2Mif等工具将图片直接转为.coe文件。

- 过程:

- 用BMP2Mif生成.coe文件。

- 在Vivado生成ROM IP核,导入.coe。

- 设置RGB格式,VGA扫描显示图像。

3. VGA显示与灰度处理原理

- 通过VGA协议分时扫描输出RGB信号。

- 用IP核ROM存放图片像素数据,VGA扫描时顺序读出。

- 灰度处理:将彩色像素转为灰度级像素,简化显示效果。

Verilog HDL设计源代码

module vga_tu(input clock, output reg [3:0] red, // Routput reg [3:0] green, // Goutput reg [3:0] blue, // Boutput hsync, // 行同步信号output vsync // 场同步信号

);reg [9:0] hcount; // 行计数reg [9:0] vcount; // 场计数wire hcount_ov; // 是否完成一行wire vcount_ov; // 是否完成一场wire dat_act; // 是否在显示区域reg vga_clk; // VGA时钟分频reg clk_tmp;// VGA时序参数parameter hsync_end = 10'd95,hdat_begin = 10'd143,hdat_end = 10'd783,hpixel_end = 10'd799,vsync_end = 10'd1,vdat_begin = 10'd34,vdat_end = 10'd514,vline_end = 10'd524;// 时钟分频always @(posedge clk_tmp) vga_clk <= ~vga_clk;always @(posedge clock)clk_tmp <= ~clk_tmp;// 行扫描always @(posedge vga_clk) beginif (hcount_ov)hcount <= 10'd0;elsehcount <= hcount + 10'd1;endassign hcount_ov = (hcount == hpixel_end);// 场扫描always @(posedge vga_clk) beginif (hcount_ov) beginif (vcount_ov)vcount <= 10'd0;elsevcount <= vcount + 10'd1;endendassign vcount_ov = (vcount == vline_end);assign dat_act = ((hcount >= hdat_begin) && (hcount < hdat_end)) &&((vcount >= vdat_begin) && (vcount < vdat_end));assign hsync = (hcount > hsync_end);assign vsync = (vcount > vsync_end);// 判断是否在图片显示区域wire now_show;assign now_show = ((hcount <= 199 + hdat_begin) && (hcount >= 0) && (vcount <= 125 + vdat_begin) && (vcount >= 0));// 导入IP核reg [14:0] addra;wire [15:0] douta;blk_mem_gen_0 your_instance_name (.clka(vga_clk), .addra(addra), // 像素点计数.douta(douta) // 图片颜色信息);// R灰度处理wire [15:0] R_grey;assign R_grey = {douta[15:11], douta[15:11], 1'b0, douta[15:11]};// 图片显示及灰度处理always @(posedge vga_clk) beginif(dat_act) begin // 在显示区域if(now_show) begin // 在图片显示区域red <= R_grey[15:12];green <= R_grey[10:7];blue <= R_grey[4:1];if(addra == 25200 - 1) // 图片大小为250x600addra <= 0;elseaddra <= addra + 1;endendend

endmodule

XDC文件配置

set_property PACKAGE_PIN D8 [get_ports {blue[3]}]

set_property PACKAGE_PIN D7 [get_ports {blue[2]}]

set_property PACKAGE_PIN C7 [get_ports {blue[1]}]

set_property PACKAGE_PIN B7 [get_ports {blue[0]}]

set_property PACKAGE_PIN A6 [get_ports {green[3]}]

set_property PACKAGE_PIN B6 [get_ports {green[2]}]

set_property PACKAGE_PIN A5 [get_ports {green[1]}]

set_property PACKAGE_PIN C6 [get_ports {green[0]}]

set_property PACKAGE_PIN A4 [get_ports {red[3]}]

set_property PACKAGE_PIN C5 [get_ports {red[2]}]

set_property PACKAGE_PIN B4 [get_ports {red[1]}]

set_property PACKAGE_PIN A3 [get_ports {red[0]}]

set_property PACKAGE_PIN E3 [get_ports clock]

set_property PACKAGE_PIN B11 [get_ports hsync]

set_property PACKAGE_PIN B12 [get_ports vsync]

set_property IOSTANDARD LVCMOS33 [get_ports {blue[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {blue[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {blue[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {blue[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports clock]

set_property IOSTANDARD LVCMOS33 [get_ports vsync]

set_property IOSTANDARD LVCMOS33 [get_ports {green[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {green[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {green[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {green[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {red[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {red[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {red[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {red[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports hsync]

下板测试

- 灰度处理前:

- 灰度处理后:

实验体会

- 学会了导入IP核,以及图片数据在FPGA中的读取与VGA显示原理。

- 掌握了使用BMP2Mif等工具一键生成.coe文件,极大方便了图片数据的转换和导入。

- 实验过程中需不断试错、调参和验证,培养了耐心和工程实操能力。

- 抓住课堂时间高效完成实验,有助于巩固理论知识,提高实践效率。