外贸网站建设要注意什么股票发行ipo和seo是什么意思

后面都只讲解网络接口类型的调用,因为内存接口相关的类型,一般都是MIG核直接调用,且内存接口调用需要实现复杂的DDR时序规则

ISERDESE2参数介绍:

参数DATA_RATE:

定义传入数据流是单数据流SDR还是双数据流DDR,可选值为SDR、DDR;

参数INTERFACE_TYPE:

可选值为MEMORY, MEMORY_DDR3, MEMORY_QDR, NETWORKING, OVERSAMPLE,其中MEMORY, MEMORY_DDR3, MEMORY_QDR为存储器使用的模式,其中OVERSAMPLE过采样模式则是用于时钟不可靠的异步低速信号使用,一般LVDS信号处理使用NETWORKING网络模式即可;

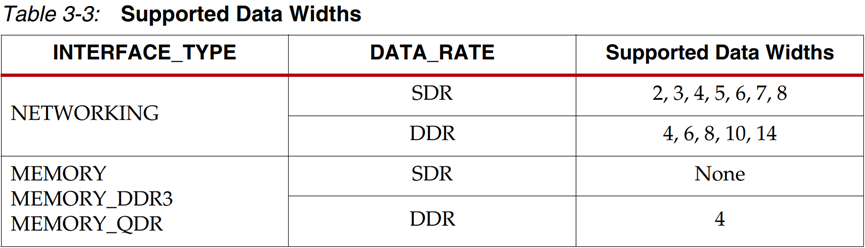

参数DATA_WIDTH:

定义串转并的并行数据的输出宽度,

其中网络模式下SDR有2~8的转换位宽选择,DDR模式有4/6/8/10/14的位宽选择,但其中大于8的位宽,需要一对ISERDESE2主从配置后级联实现;

参数DYN_CLKDIV_INV_EN、DYN_CLK_INV_EN:

与端口DYNCLKDIVSEL、DYNCLKSEL搭配使用,控制输入时钟极性,仅在MEMORY_QDR模式下使用,不用关注,不使用时设置为FALSE即可;

参数INIT_Q1、INIT_Q2、INIT_Q3、INIT_Q4:

4个Q1、Q2、Q3、Q4输出端口的上电初始化值,可设置为0或1;

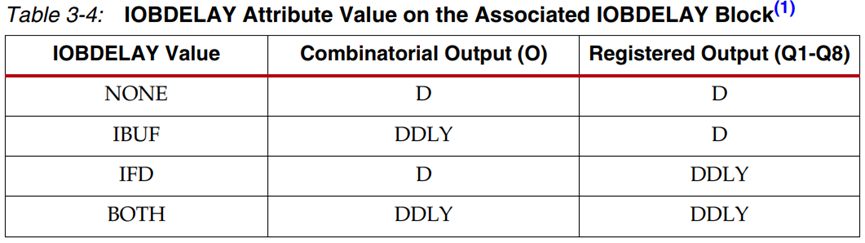

参数IOBDELAY:

当D和DDLY都连接有效信号时,该参数控制输出端口O和Q1Q8使用的数据来自输入端口是D还是DDLY,其中D连接到IOB,DDLY连接到IDELAYE2,O直接组合输出,Q1Q8寄存器输出;

参数NUM_CE:

定义了使用的时钟使能(CE1和CE2)的数量。可能的值为1和2(默认= 2);

参数OFB_USED:

可选值FALSE, TRUE,只有当参数值设置为TRUE时,端口OFB才能工作;

参数SERDES_MODE:

可选值MASTER, SLAVE,当要扩展并行位宽时,主ISERDESE2设置MASTER,从设置SLAVE,单个使用时默认MASTER;

参数SRVAL_Q1、SRVAL_Q2、SRVAL_Q3、SRVAL_Q4:

4个Q1、Q2、Q3、Q4输出端口的复位值,可设置为0或1;

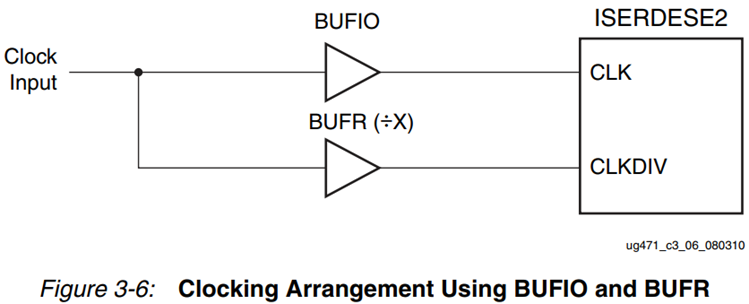

时钟使用方法:

NETWORKING网络接口类型:

CLK和CLKDIV的相位关系在串并转换中十分重要,两者必须能够相位对齐;

且对于有效时钟的使用也有规定:

情况1:CLK由BUFIO驱动,CLKDIV由BUFR驱动,这是指CLK是由FPGA输入得到,CLKDIV是由CLK经过BUFR分频得到;

情况2:CLK由MMCM或PLL驱动,CLKDIV由MMCM或PLL的CLKOUT[0:6]这几个端口驱动,这时两个时钟都出自同一个MMCM的较近相位同步的端口;

当使用MMCM驱动CLK和CLKDIV时,缓冲器类型不能乱用,CLK为BUFG类型时,CLKDIV也需要为BUFG类型;

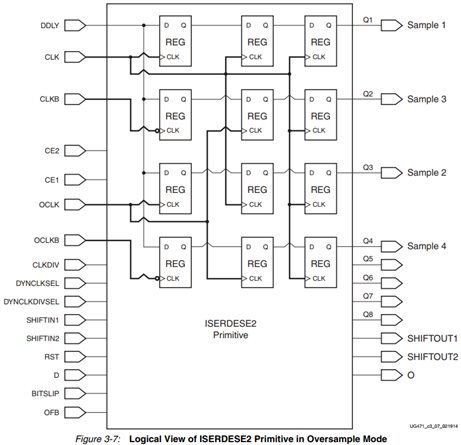

OVERSAMPLE过采样接口类型:

过采样模式可以捕获双倍数据速率DDR数据的两个相位,使用CLK和OCLK两个时钟进行捕获,CLK和OCLK之间存在90°相位偏移的关系,时钟的有效安排为:

情况1:CLK和CLKB由BUFIO驱动,OCLK和OCLKB由相位偏移90°的BUFIO驱动,且这些时钟都为同一个MMCM驱动输出;

情况2:CLK和CLKB由BUFG驱动,OCLK和OCLKB由相位偏移90°的BUFG驱动,且这些时钟都为同一个MMCM驱动输出;

这些时钟的关系为:

CLK:0°,OCLK:90°,CLKB:180°,OCLKB:270°;

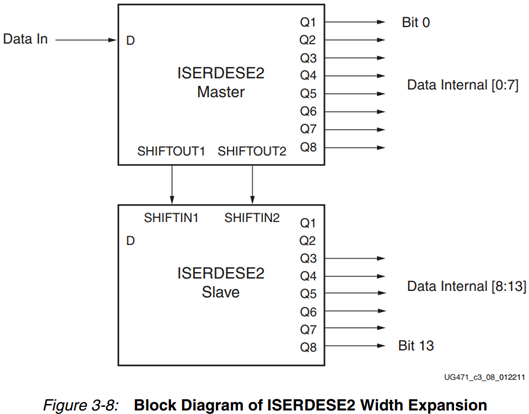

ISERDESE2宽度扩展:

当在DDR模式下,使用两个ISERDESE2级联,可以支持10位和14位的宽度扩展;

两个组件,一个SERDES_MODE设置主模式MASTER,一个设置从模式SLAVE,将主ISERDESE2的SHIFTOUT端口连接到从ISERDESE2的SHIFTIN端口,两个ISERDESE2模块必须是相邻的主从对,且两个ISERDESE2模块必须处于网络模式,连接框图如下:

使用10位模式时,输出管脚为:主Q1Q8,从Q3Q4;

使用14位模式时,输出管脚为:主Q1Q8,从Q3Q8;

DATA_WIDTH设置为10或14使用;

BITSLIP子模块:

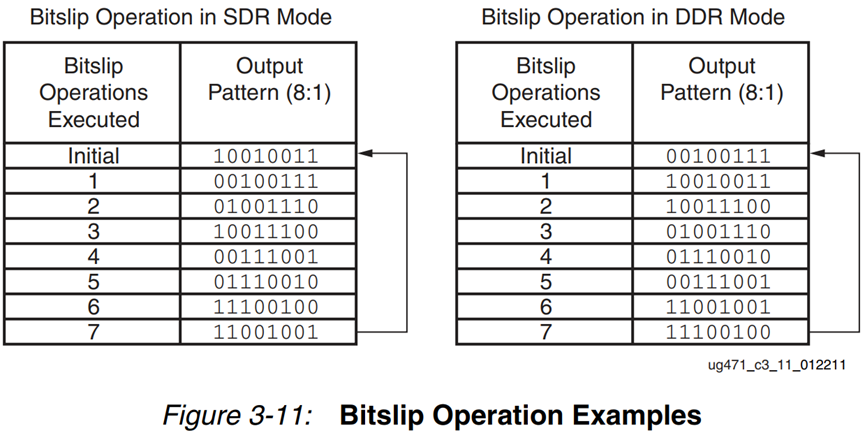

每个ISERDESE2都包含一个BITSLIP子模块,能够将转换的并行数据重新排序后输出;

通过置位ISERDESE2模块的Bitslip引脚,传入的串行数据流在并行端被重新排序,该操作可以重复执行,一直执行到并行输出了用户需要的输出模式为止;

从之前可以知道,先进入ISERDESE2的数据将放在Q8的位置,上图中initial一栏的输出二进制序列,从左到右表示Q8到Q1;

在上图中,左侧演示SDR模式的移位操作,每次BITSLIP操作,输出模式向左移动一位;

右侧DDR模式的移位,每次BITSLIP操作,输出模式在向右移动一位和向左移动三位的两种移位方式交替进行;

且两种方式移动8次后都会回到初始的输出模式;

BITSLIP模块仅在NETWORKING网络模式下可用,执行BITSLIP操作时,bitslip端口必须在一个CLKDIV周期内保持高电平,保持1个CLKDIV高电平则是成功执行一次bitslip操作,但是不能连续拉高两个周期高电平,两次移位操作之前至少需要CLKDIV保持一个周期的低电平;且为了保证移位操作成功作用到输出上,SDR模式下移位后需要等待至少2个CLKDIV周期,DDR模式需至少等待3个CLKDIV周期,才能对输出数据进行判断;

如果ISERDESE2被复位,bitslip的移位逻辑也会被复位并回到其初始状态;

下一节进行ISERDESE2的仿真验证。

本文章由威三学社出品

对课程感兴趣可以私信联系