站内推广的主要目的是管理系统论文

参考文献

[1]Static Timing Analysis for Nanometer Designs A Practical Approach

[2]静态时序分析圣经翻译计划

三.组合逻辑单元的时序模型

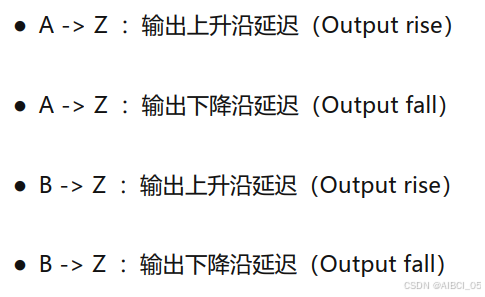

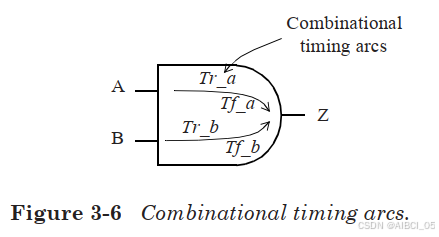

对于一个两输入与门的时序弧,两个时序弧均为正单边类型(positive_unate)。这意味着对于 NLDM 模型,将会有四个表格模型用于指定延迟。同样,也将有四个表格模型用于指定输出过渡时间(压摆)。

1. 延迟与压摆模型

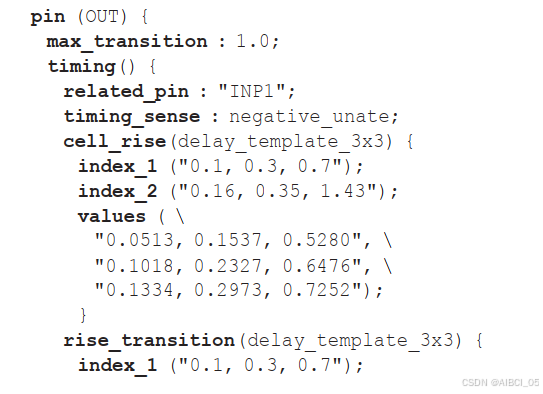

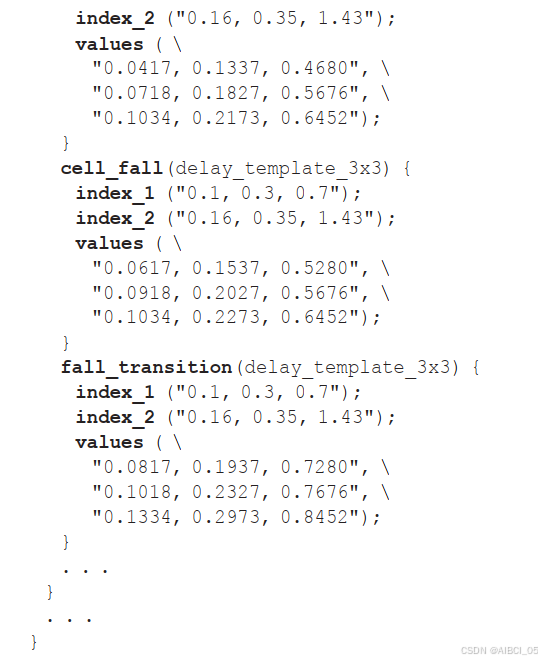

以三输入与非门(nand)单元的输入 INP1 到输出OUT 的时序模型为例。

在上面的例子中,使用了两个单元延迟表 cell_rise 和 cell_fall 以及两个过渡时间表 rise_transition 和 fall_transition 来描述从 INP1 到 OUT 的时序弧的特性,上面的例子中还包括了输出的最大过渡时间(max_transition)值。

与非门单元中的时序弧为负单边类型(negative unate),这表示输出引脚电平跳变方向与输入引脚电平跳变方向是相反的。因此,查找 cell_rise 表对应于输入引脚上的下降过渡时间。

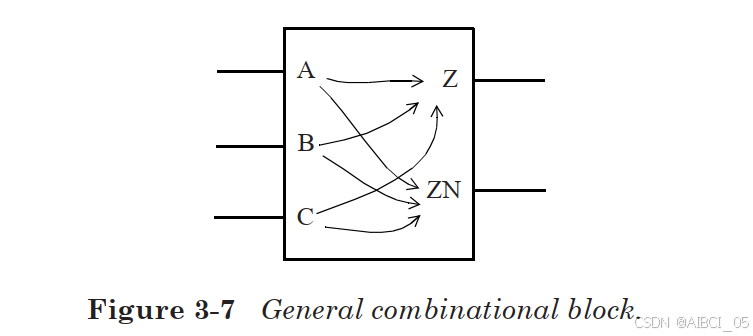

2. 通用组合逻辑块

以具有三输入和两输出的通用组合逻辑块(General Combinational Block)为例。像这样的组合逻辑块可以具有多个时序弧。通常,从块的每个输入到每个输出都有一条时序弧。如果从输入到输出的逻辑路径是同相(non-inverting)或正单边类型的,则输出的极性(polarity)与输入的极性相同;如果逻辑路径是反相(inverting)或负单边类型,则输出的极性与输入相反,即当输入电平上升时,输出电平将下降。这些时序弧代表了通过这个组合逻辑块的传播延迟。

通过组合逻辑单元的某些时序弧可以既是正单边类型,也是负单边类型的。一个例子是通过两输入异或门(xor)单元的时序弧,根据该单元的另一个输入的逻辑状态,两输入异或门单元的输入引脚处的电平跳变会导致输出引脚处的电平沿相同或相反的方向跳变。这些时序弧可以描述为非单边类型(non-unate)的,也可以描述为两组状态相关(state-dependent)的正单边类型时序模型和负单边类型时序模型。

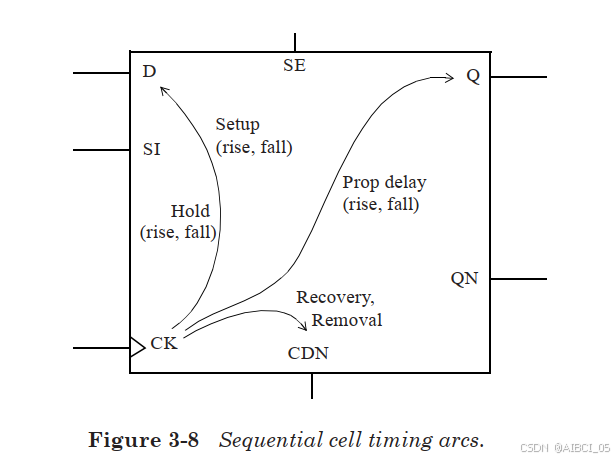

四. 时序逻辑单元的时序模型

以下图的时序逻辑单元的时序弧为例。

对于同步(synchronous)输入,例如引脚 D(或 SI, SE),存在以下时序弧:

- 建立时间(setup)检查时序弧,包括上升沿和下降沿;

- 保持时间(hold)保持时序弧,包括上升沿和下降沿;

对于异步(asynchronous)输入,例如引脚 CDN,存在以下时序弧: - 撤销(remova)时间检查时序弧;

- 恢复(recovery)时间检查时序弧;

对于触发器的同步输出,例如引脚 Q 或 QN,存在以下时序弧: - 时钟引脚(CK)到输出端口(Q和QN)的传播延迟时序弧线,包括上升沿和下降沿。

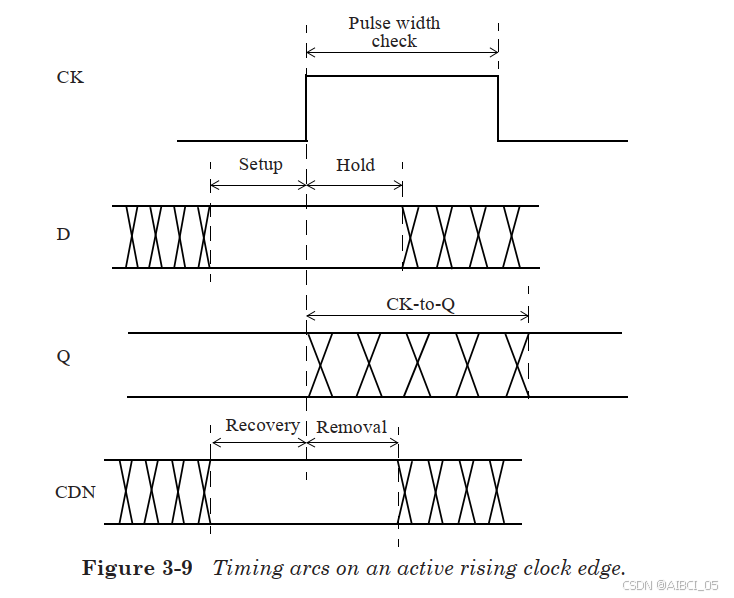

所有同步时序弧均相对于时钟的有效沿(active edge),即时序逻辑单元捕获数据的时钟沿。此外,时钟引脚和异步引脚(如复位引脚)还需要进行脉冲宽度(pulse width)时序检查。各种时序检查如下图3-9 所示:

1. 同步时序检查

为了确保数据能够正确通过时序单元传播,需要进行建立时间和保持时间的同步时序检查。这些时序检查可验证输入的数据在时钟有效沿上是否为确定的逻辑状态,并且在有效沿上将正确的数据锁存下来。

- 建立时间:输入的数据必须在有效时钟沿之前保持稳定的最短时间称为建立时间(setup time)。这是根据最晚的(the latest)数据信号超过其阈值(通常为 Vdd 的 50%)到有效时钟沿超过其阈值(通常为 Vdd 的50%)的时间间隔测量的。

- 保持时间:保持时间(hold time)是在时钟有效沿之后输入的数据必须保持稳定的最短时间,这也是根据有效时钟沿超过其阈值到最早的(the earliest)数据信号超过其阈值的时间间隔来度量的。

建立时间和保持时间检查示例

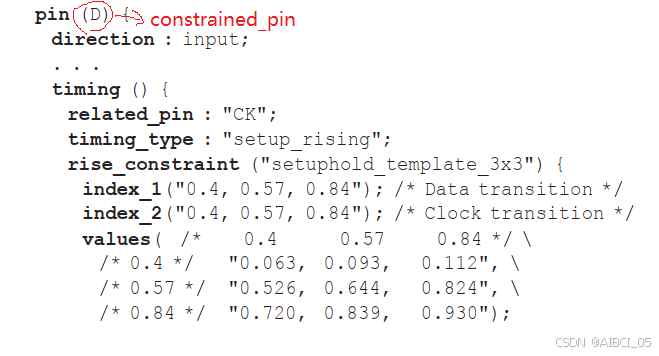

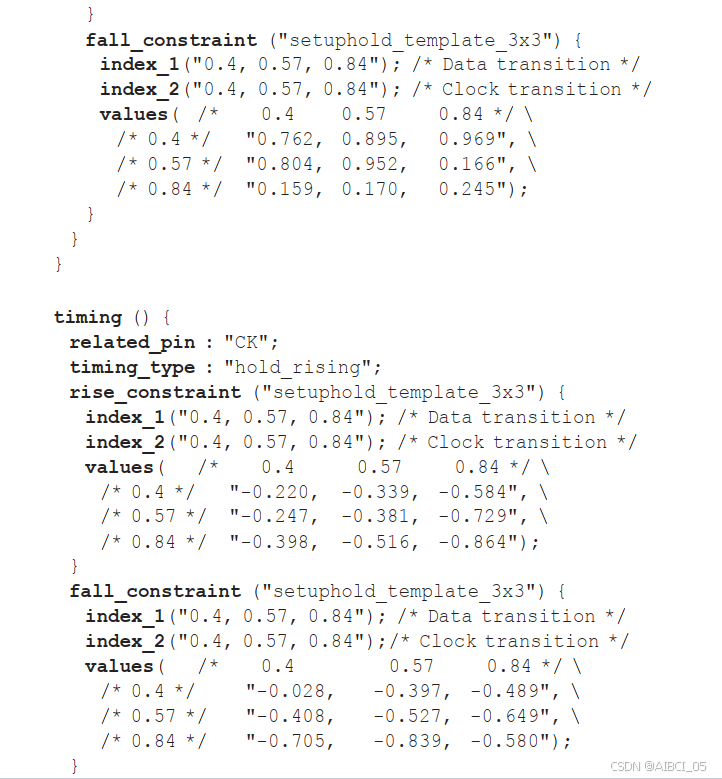

时序单元同步引脚的建立时间和保持时间约束通常用二维表格来描述,如下所示。下面的例子展示了触发器数据引脚的建立时间和保持时间时序信息:

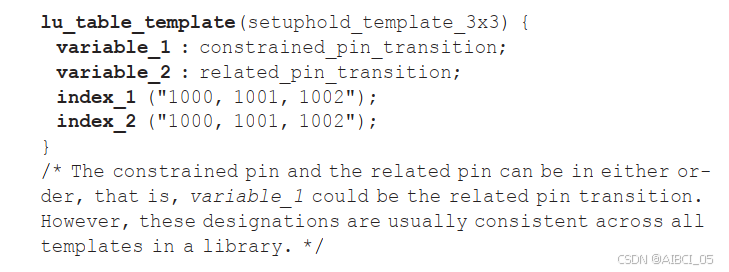

上例展示了相对时序单元时钟引脚CK的上升沿,在输入引脚D上的建立时间和保持时间约束。二维表格模型是根据约束引脚constrained_pin(D)和相关引脚 related_pin(CK)处的过渡时间确定的,二维表格的查找是基于库中描述的模板setuphold_template_3x3 的。因此,当 D 引脚的上升沿过渡时间为 0.4ns, CK 引脚的上升沿过渡时间为 0.84ns 时, D 引脚上升沿的建立时间约束为0.112ns,该值是从 rise_constraint 表中读取的。

建立时间约束的 rise_constraint 和 fall_constraint 表是指constrained_pin。所用的时钟过渡时间由 Timing_type 决定,它会指定该时序逻辑单元是上升沿触发还是下降沿触发。

建立时间和保持时间检查里的负值

上面示例中的某些保持时间值是负数。这是可以接受的,这种情况通常发生在触发器的引脚到数据内部锁存点的路径长于相应的时钟路径时。因此,负的保持时间检查意味着触发器的数据引脚可以在时钟引脚之前改变,并且仍然满足保持时间的检查要求。触发器的建立时间值也可以为负。这意味着触发器的数据引脚可以在时钟引脚之后改变,并且仍然满足建立时间的检查要求。

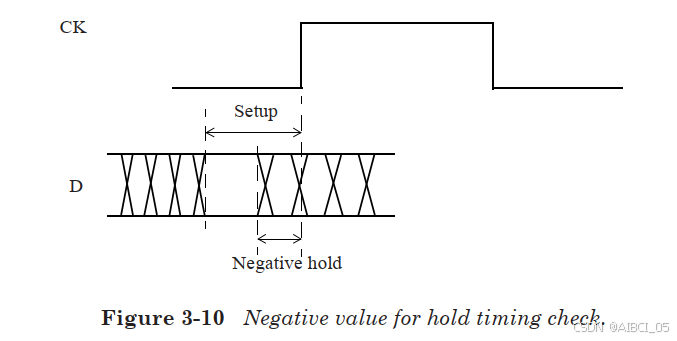

但是建立时间和保持时间不可以都为负(建立时间为负数代表数据在有效沿后到来,保持时间为负数代表数据在有效沿前消失,显然两者不能同时出现)。 因此,如果建立(或保持)时间检查包含负值,则相应的保持(或建立)时间检查应为正值,且足够大,以使建立时间加上保持时间之和是一个正数。具有负的保持时间值的示例如图 3-10 所示,由于建立时间检查会先于保持时间检查,所以此时的建立时间加上保持时间显然是一个正数。建立时间加上保持时间即为要求数据信号稳定的区域的宽度。

对于触发器,在扫描数据(scan data)输入引脚上设置一个负的保持时间会很有帮助,这样可以给予时钟偏斜(clock skew)一定的灵活性,并且可以消除当扫描模式(scan mode)下保持时间发生违例时插入缓冲器(buffer)的需要(扫描模式是将触发器串联在一起形成一条扫描链的模式,触发器的输出通常连接到串联的下一个触发器的扫描数据输入引脚,这些连接是用于芯片测试的)。

2. 异步时序检查

脉冲宽度检查

除了同步和异步时序检查外,还有一项检查去确保逻辑单元输入引脚上的脉冲宽度满足最低要求。例如,如果时钟引脚上的脉冲宽度小于指定的最小值,则时钟可能无法正确锁存数据。也可以为相关的同步和异步引脚指定脉冲宽度检查(pulse width check),并且可以为高脉冲和低脉冲分别指定最小脉冲宽度检查。

恢复时间和撤销时间检查

诸如异步复位(clear)或异步置位(set)之类的异步引脚会覆盖单元的任何同步行为。当异步引脚处于有效(active)状态时,输出将由异步引脚控制,而不是由时钟锁存到的输入数据控制。但是,当异步引脚变为无效(inactive)状态时,时钟的有效边沿将开始锁存输入的数据。异步恢复(recovery)时间和撤销(removal)时间约束检查将验证异步引脚在下一个时钟有效沿处是否已明确返回到了无效状态。

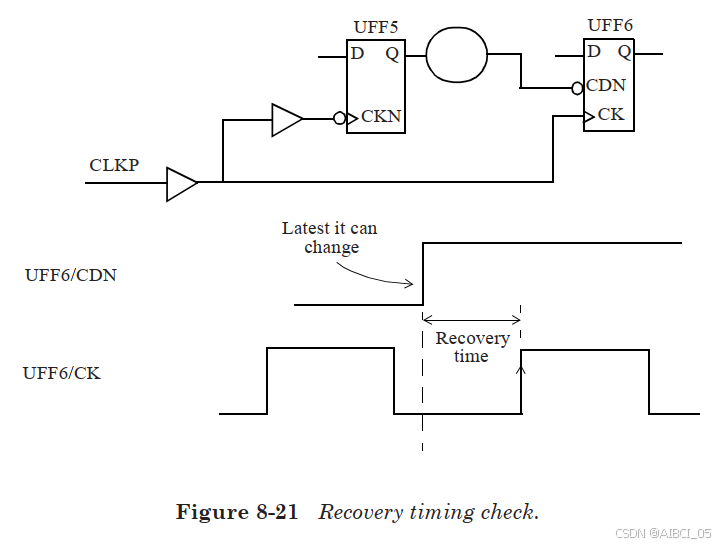

- 恢复时间(recovery):恢复时间是指异步输入被置为无效(de-asserted)后在下一个时钟有效沿之前需要保持稳定的最短时间。

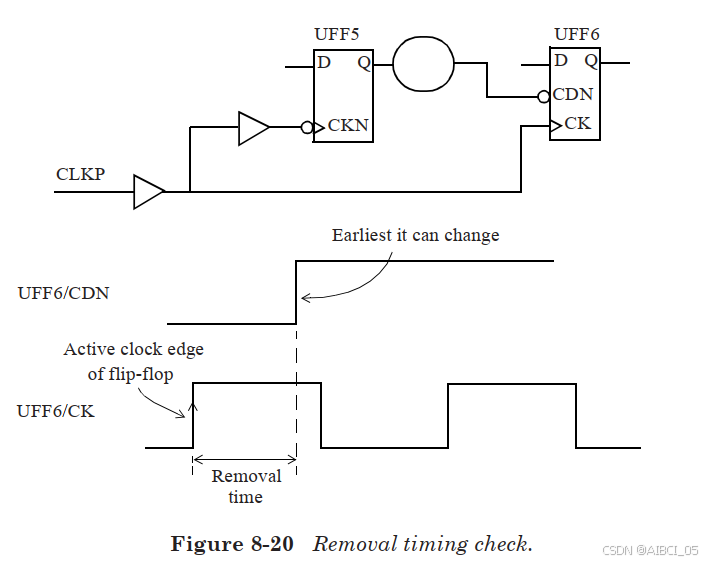

- 撤销时间(removal):撤销时间是指在一个有效的时钟沿之后,异步引脚必须保持有效状态的最小时间,即在有效时钟沿之后必须经过一段撤销时间才能够将异步引脚置为无效状态。

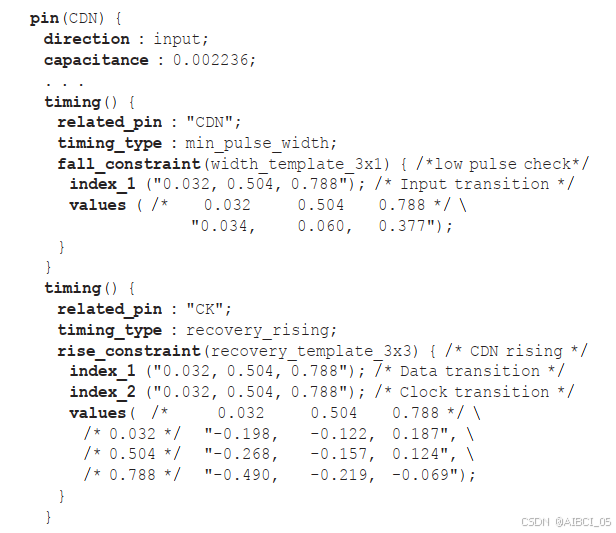

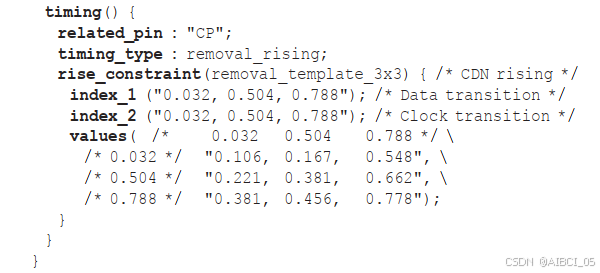

下面给出了触发器的异步清零引脚 CDN 的恢复时间、撤销时间和脉冲宽度检查的示例,其中恢复时间和撤销时间检查还与时钟引脚 CK 有关。由于恢复时间和撤销时间检查是针对异步引脚被置为无效的时刻,因此在以下示例中仅存在上升约束。 CDN 引脚的最小脉冲宽度检查用于低脉冲,这是由于 CDN 引脚为低电平有效,因此该引脚上的高脉冲宽度没有限制,因此未指定。

3.传播延迟( t c l k 2 q t_{clk2q} tclk2q)

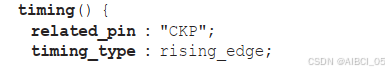

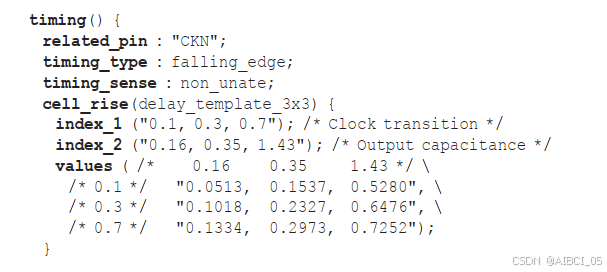

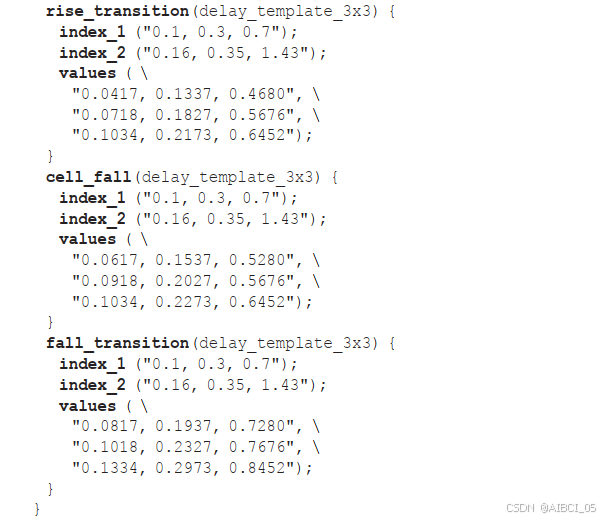

时序单元的传播延迟(propagation delay)是指从时钟的有效沿到输出的上升沿或下降沿。以下是一个时钟下降沿触发的触发器从时钟引脚 CKN 到输出 Q 的传播延迟弧的示例。这是一个非单边类型(non-unate)的时序弧,因为时钟的有效沿会导致输出引脚 Q 的电平上升或下降,因此由对应4个查找表,代表着上升下降延迟和上升下降过渡时间。

可以看到,输出的传播延迟会根据输入过渡时间和输出负载电容以二维表格的形式呈现。值得注意的是,由于触发器是时钟下降沿触发的,因此要使用的输入过渡时间是 CKN 引脚的下降过渡时间,这在上面的示例中可以从 Timing_type 字段中看出,上升沿触发的触发器将把 rising_edge 指定为其 timing_type。