网站开发项目视频WordPress小工具两列

在PCB设计中,往往透过制程改善如背钻、盲孔或埋孔,来消除不必要的Via stub,可是多出来的制造成本会压低产品的毛利,可是又有什么办法可以不透过制程改善以缩小Via stub带来的SI困扰呢?

本周我们来讲从Layout布局的角度以缩小Via stub长度,改善Via stub带来的不良影响,有效改善讯号质量。

传统设计带来的长Via Stub效应

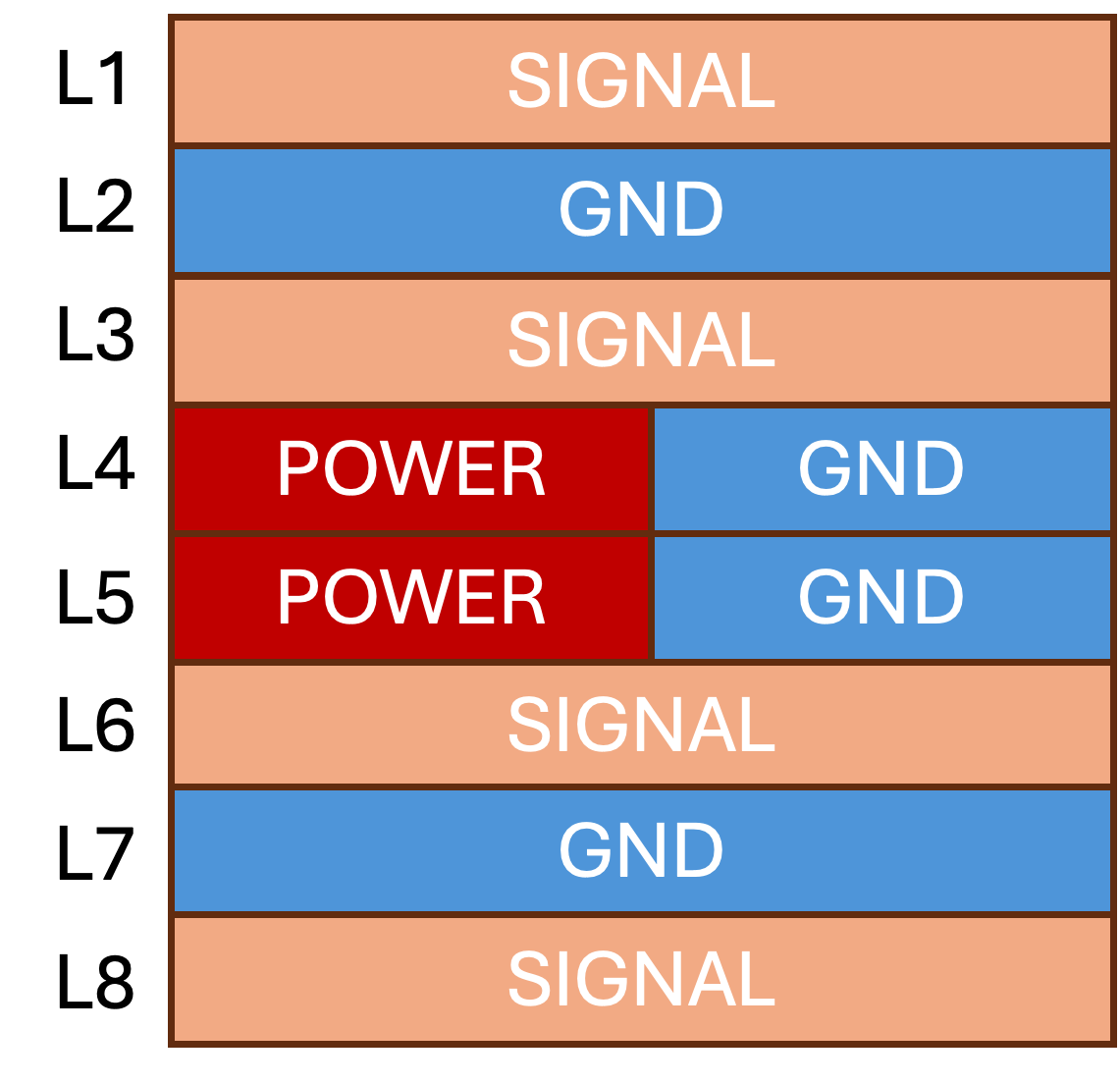

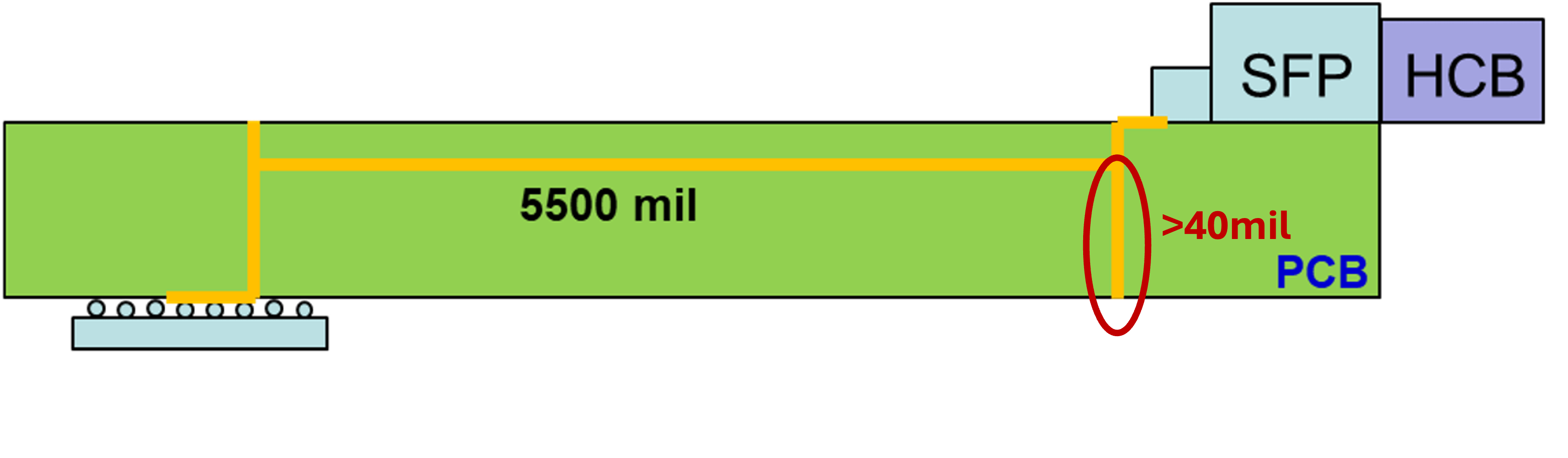

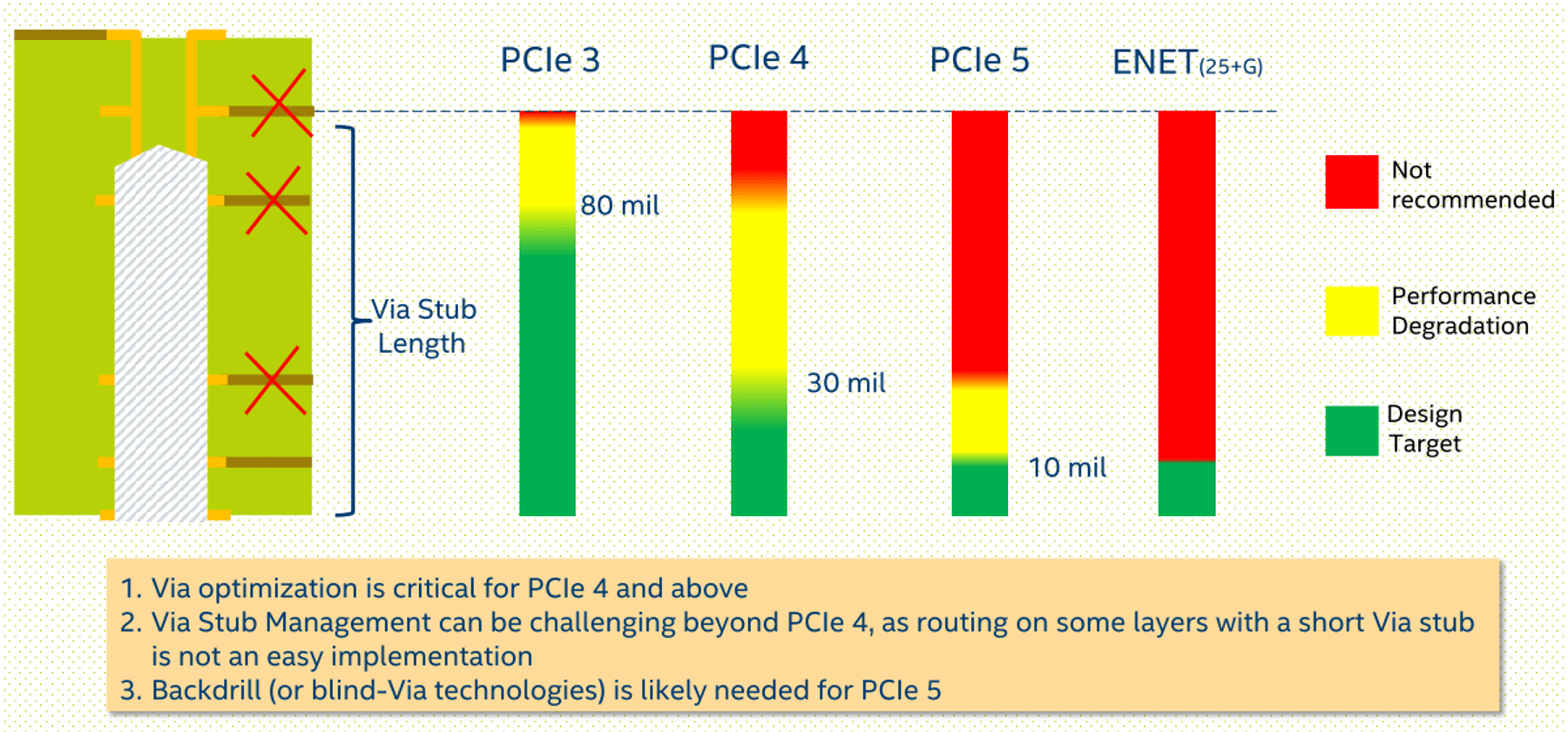

在一个典型的ASIC与连接器的拓朴中,叠构为8层板,ASIC放在底层,原本若将走线安排在L3,会在Connector端的Via产生约40mil长的Via stub。 这个Via stub的长度主要是由板子的厚度所决定,不同板厚会有不同的数值。 虽然一个40mil长的Via stub在某些情况下可能看似问题不大,但这还需要根据具体的SI测试或模拟结果来判断。 通常这种设计在低速线路(<10Gbps)是还可以接受的,从Intel早期提供的文件来看,PCIe Gen3(8Gbps)是可以接受大约80mil的Via stub。

P.S. 实际可忍受的Via stub长度,还是要看SI模拟或测试的结果,Intel提供的文件主要是针对他们提出的Topology,跟您的设计不一定完全一样!

Intel对于PCIe Gen3~Gen5,不同世代Via stub长度的设计建议:

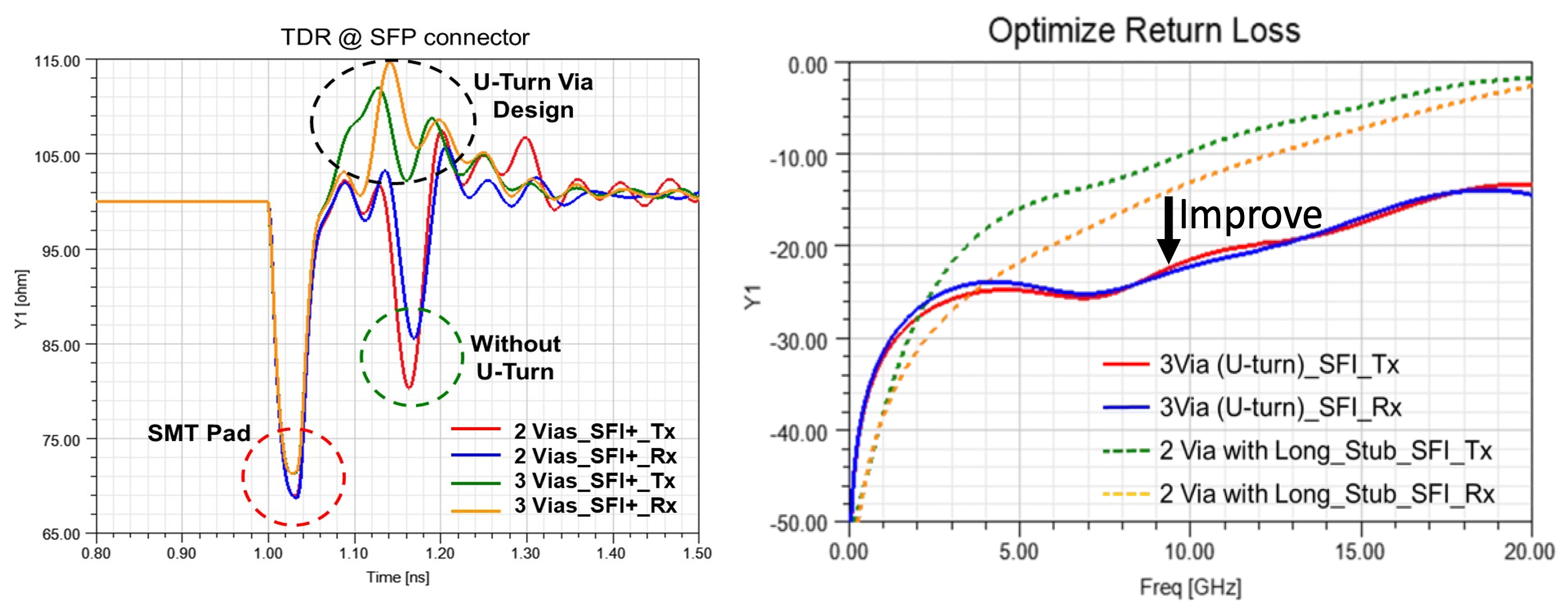

但在超过10Gbps的高速通道中,这么长的Via stub很容易导致信号传输异常。 透过TDR的分析,可以发现该走线会出现一个相当明显且深邃的阻抗掉落,这正是由于长Via stub导致的阻抗不匹配现象。 所以Return loss在10GHz的时候就直奔-10dB去了,要知道以一个阻抗匹配的通道,Return loss应该至少要小于-15dB(能做到-20dB就是Perfect了)。 因此,这种设计方案从SI的角度来看,是难以接受的。

U-Turn Via

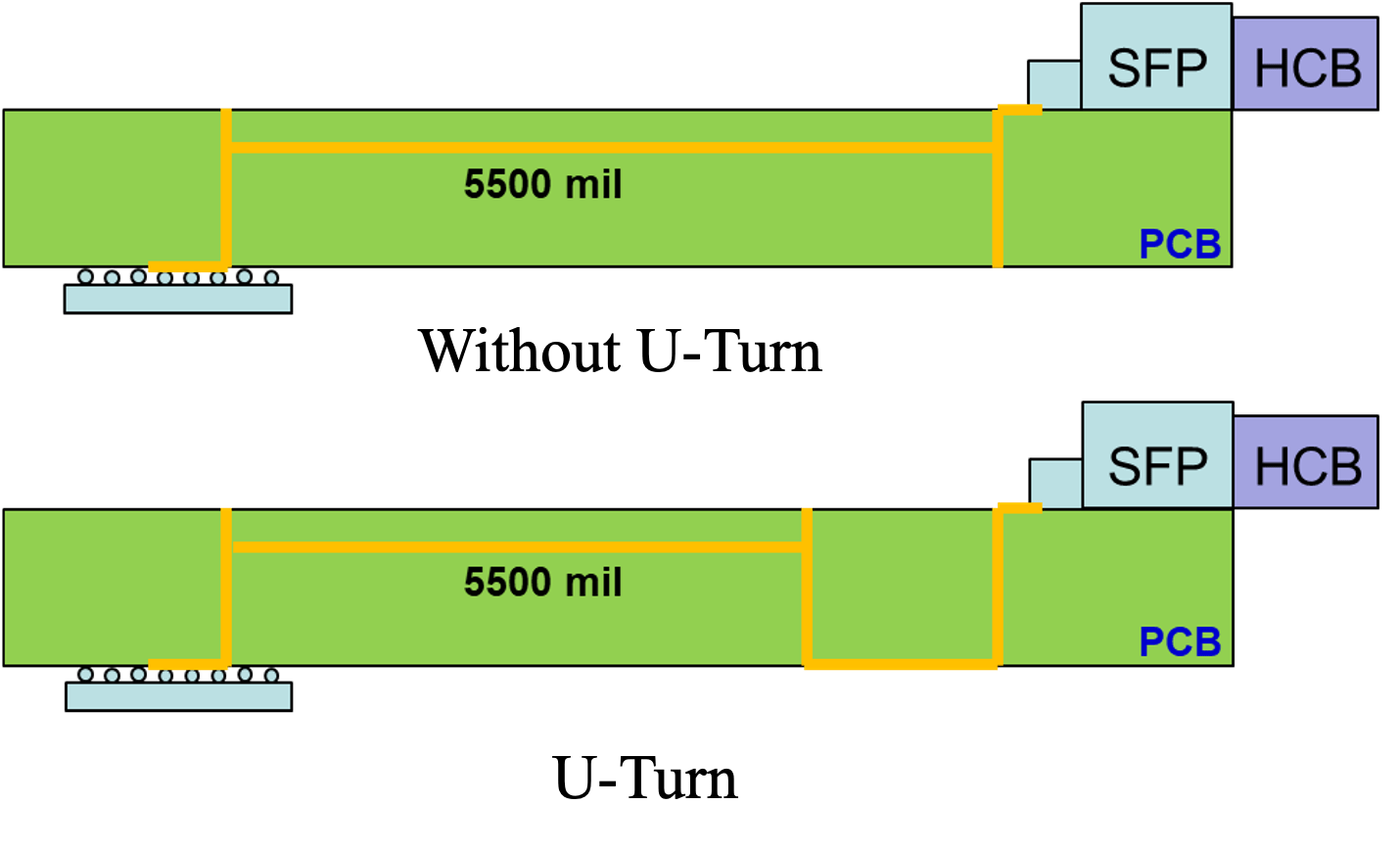

那么,如何不依赖PCB制程,例如背钻、盲埋孔,以移除Via stub,仅从Layout调整上来消除长Via stub,该怎么做? 除了我上周的文章介绍的走线层别规划外,还有一种叫U-Turn Via的解法:在原有路径上增加一颗额外的via,形成U-Turn Via设计。

以上述设计为例,若走线安排在L3层,原先从L3到L1的换层会产生一段长达40mil的Via stub。 为了改善这一情况,我们在Connector via前面新增一颗via,该Via首先将讯号从L3换层到底层L8,之后在L8走线,最终再由L8-L1的Connector via连回表层的连接器。 如此一来,原先在L3层产生的长Via stub就可以变成大概12mil的Via stub,缺点则是多出一颗Via,以及一段底层走线,SI设计者得好好控制这颗新增的Via的阻抗与走线长度。

U-Turn Via的信号完整性分析

实际执行SI电磁仿真,利用U-Turn Via设计后,可以明显观察到TDR阻抗曲线的改善。 由于原本长Via stub被完全移除,新通道的阻抗特性不再出现明显的掉落点,相反地,因为增加了一颗额外的Via,导致整个路径的阻抗会略微偏高。 但这个偏移可以通过进一步优化Via的anti-pad设计及调整P/N两颗Via之间的间距搞定。

从Return loss的模拟结果来看,原本在10GHz频率下仅有-10dB的Return loss,在经过U-Turn Via设计优化后,整个Return loss曲线完全改善,-10dB的频宽从10GHz,跑到图外面去了10GHz这个频率点优化了整整10dB至-20dB,效果绝佳! 换言之,整个高速通道的阻抗匹配变得更好!

U-Turn Via设计准则整理

尽管U-Turn Via设计能够通过Layout改善,解决部分Via stub问题,但在实际应用中仍有一些需要注意的事项:

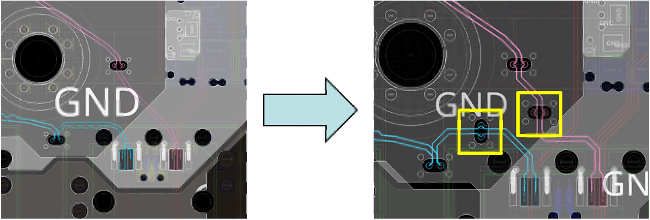

- 控制新增的Via的阻抗当这颗Via阻抗偏高或偏低时,需要通过调整Via的anti-pad尺寸,与P/N via的间距,以改善阻抗。 不要让这个新增的Via变成额外设计上的负担。 这点除了手动优化这些参数外,也可以通过3D电磁模拟软件的Sweep功能或是现在正夯的AI引擎(例如Cadence Optimality)去有效率地改善阻抗。

- 注意走线空间U-Turn Via设计的成功与否在于如何合理规划走线路径及层间转换。 不仅要在物理上消除长via stub,还需注意多出来的表层走线长度,我们提过表层走线的损耗是比较大的,所以多出来的走线如果太长,会加大整体通道损耗,反而有反效果,这就得不偿失,做白工。

- 透过SI模拟分析通道的优化在设计修改后,必须搭配充分的TDR模拟与损耗模拟,确认改善效果。 并确认最终通道结果可以满足高速讯号界面的Spec,一个完整的SI分析,可以帮助设计者免除测试时不必要的烦恼!