普洱做网站的报价现在清算组备案在哪个网站做

一、章节概括

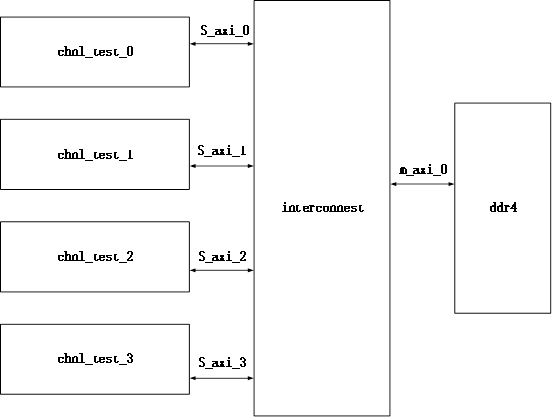

这一节使用interconnect RTL ip核将DDR4与四个读写通道级联,在测试工程中,将四个通道同时写入/读出地址与数据,并使用modelsim仿真器仿真,四个通道同时发送写请求或读请求后,经过interconnect后,观察数据的读写功能。

二、功能框架

三、interconnect RTL IP 核例化模版

axi_interconnect_0 axi_interconnect_0 (

.INTERCONNECT_ACLK(c0_ddr4_clk), // input wire INTERCONNECT_ACLK

.INTERCONNECT_ARESETN(~c0_ddr4_rst), // input wire INTERCONNECT_ARESETN

//chnl 0

.S00_AXI_ARESET_OUT_N(S00_AXI_ARESET_OUT_N), // output wire S00_AXI_ARESET_OUT_N

.S00_AXI_ACLK(clk_75m), // input wire S00_AXI_ACLK

.S00_AXI_AWID(S00_AXI_AWID), // input wire [3 : 0] S00_AXI_AWID

.S00_AXI_AWADDR(S00_AXI_AWADDR), // input wire [31 : 0] S00_AXI_AWADDR

.S00_AXI_AWLEN(S00_AXI_AWLEN), // input wire [7 : 0] S00_AXI_AWLEN

.S00_AXI_AWSIZE(S00_AXI_AWSIZE), // input wire [2 : 0] S00_AXI_AWSIZE

.S00_AXI_AWBURST(S00_AXI_AWBURST), // input wire [1 : 0] S00_AXI_AWBURST

.S00_AXI_AWLOCK(S00_AXI_AWLOCK), // input wire S00_AXI_AWLOCK

.S00_AXI_AWCACHE(S00_AXI_AWCACHE), // input wire [3 : 0] S00_AXI_AWCACHE

.S00_AXI_AWPROT(S00_AXI_AWPROT), // input wire [2 : 0] S00_AXI_AWPROT

.S00_AXI_AWQOS(S00_AXI_AWQOS), // input wire [3 : 0] S00_AXI_AWQOS

.S00_AXI_AWVALID(S00_AXI_AWVALID), // input wire S00_AXI_AWVALID

.S00_AXI_AWREADY(S00_AXI_AWREADY), // output wire S00_AXI_AWREADY

.S00_AXI_WDATA(S00_AXI_WDATA), // input wire [511 : 0] S00_AXI_WDATA

.S00_AXI_WSTRB(S00_AXI_WSTRB), // input wire [63 : 0] S00_AXI_WSTRB

.S00_AXI_WLAST(S00_AXI_WLAST), // input wire S00_AXI_WLAST

.S00_AXI_WVALID(S00_AXI_WVALID), // input wire S00_AXI_WVALID

.S00_AXI_WREADY(S00_AXI_WREADY), // output wire S00_AXI_WREADY

.S00_AXI_BID(S00_AXI_BID), // output wire [3 : 0] S00_AXI_BID

.S00_AXI_BRESP(S00_AXI_BRESP), // output wire [1 : 0] S00_AXI_BRESP

.S00_AXI_BVALID(S00_AXI_BVALID), // output wire S00_AXI_BVALID

.S00_AXI_BREADY(S00_AXI_BREADY), // input wire S00_AXI_BREADY

.S00_AXI_ARID(S00_AXI_ARID), // input wire [3 : 0] S00_AXI_ARID

.S00_AXI_ARADDR(S00_AXI_ARADDR), // input wire [31 : 0] S00_AXI_ARADDR

.S00_AXI_ARLEN(S00_AXI_ARLEN), // input wire [7 : 0] S00_AXI_ARLEN

.S00_AXI_ARSIZE(S00_AXI_ARSIZE), // input wire [2 : 0] S00_AXI_ARSIZE

.S00_AXI_ARBURST(S00_AXI_ARBURST), // input wire [1 : 0] S00_AXI_ARBURST

.S00_AXI_ARLOCK(S00_AXI_ARLOCK), // input wire S00_AXI_ARLOCK

.S00_AXI_ARCACHE(S00_AXI_ARCACHE), // input wire [3 : 0] S00_AXI_ARCACHE

.S00_AXI_ARPROT(S00_AXI_ARPROT), // input wire [2 : 0] S00_AXI_ARPROT

.S00_AXI_ARQOS(S00_AXI_ARQOS), // input wire [3 : 0] S00_AXI_ARQOS

.S00_AXI_ARVALID(S00_AXI_ARVALID), // input wire S00_AXI_ARVALID

.S00_AXI_ARREADY(S00_AXI_ARREADY), // output wire S00_AXI_ARREADY

.S00_AXI_RID(S00_AXI_RID), // output wire [3 : 0] S00_AXI_RID

.S00_AXI_RDATA(S00_AXI_RDATA), // output wire [511 : 0] S00_AXI_RDATA

.S00_AXI_RRESP(S00_AXI_RRESP), // output wire [1 : 0] S00_AXI_RRESP

.S00_AXI_RLAST(S00_AXI_RLAST), // output wire S00_AXI_RLAST

.S00_AXI_RVALID(S00_AXI_RVALID), // output wire S00_AXI_RVALID

.S00_AXI_RREADY(S00_AXI_RREADY), // input wire S00_AXI_RREADY

//chnl 1

.S01_AXI_ARESET_OUT_N(S01_AXI_ARESET_OUT_N), // output wire S01_AXI_ARESET_OUT_N

.S01_AXI_ACLK(clk_125m), // input wire S01_AXI_ACLK

.S01_AXI_AWID(S01_AXI_AWID), // input wire [3 : 0] S01_AXI_AWID

.S01_AXI_AWADDR(S01_AXI_AWADDR), // input wire [31 : 0] S01_AXI_AWADDR

.S01_AXI_AWLEN(S01_AXI_AWLEN), // input wire [7 : 0] S01_AXI_AWLEN

.S01_AXI_AWSIZE(S01_AXI_AWSIZE), // input wire [2 : 0] S01_AXI_AWSIZE

.S01_AXI_AWBURST(S01_AXI_AWBURST), // input wire [1 : 0] S01_AXI_AWBURST

.S01_AXI_AWLOCK(S01_AXI_AWLOCK), // input wire S01_AXI_AWLOCK

.S01_AXI_AWCACHE(S01_AXI_AWCACHE), // input wire [3 : 0] S01_AXI_AWCACHE

.S01_AXI_AWPROT(S01_AXI_AWPROT), // input wire [2 : 0] S01_AXI_AWPROT

.S01_AXI_AWQOS(S01_AXI_AWQOS), // input wire [3 : 0] S01_AXI_AWQOS

.S01_AXI_AWVALID(S01_AXI_AWVALID), // input wire S01_AXI_AWVALID

.S01_AXI_AWREADY(S01_AXI_AWREADY), // output wire S01_AXI_AWREADY

.S01_AXI_WDATA(S01_AXI_WDATA), // input wire [511 : 0] S01_AXI_WDATA

.S01_AXI_WSTRB(S01_AXI_WSTRB), // input wire [63 : 0] S01_AXI_WSTRB

.S01_AXI_WLAST(S01_AXI_WLAST), // input wire S01_AXI_WLAST

.S01_AXI_WVALID(S01_AXI_WVALID), // input wire S01_AXI_WVALID

.S01_AXI_WREADY(S01_AXI_WREADY), // output wire S01_AXI_WREADY

.S01_AXI_BID(S01_AXI_BID), // output wire [3 : 0] S01_AXI_BID

.S01_AXI_BRESP(S01_AXI_BRESP), // output wire [1 : 0] S01_AXI_BRESP

.S01_AXI_BVALID(S01_AXI_BVALID), // output wire S01_AXI_BVALID

.S01_AXI_BREADY(S01_AXI_BREADY), // input wire S01_AXI_BREADY

.S01_AXI_ARID(S01_AXI_ARID), // input wire [3 : 0] S01_AXI_ARID

.S01_AXI_ARADDR(S01_AXI_ARADDR), // input wire [31 : 0] S01_AXI_ARADDR

.S01_AXI_ARLEN(S01_AXI_ARLEN), // input wire [7 : 0] S01_AXI_ARLEN

.S01_AXI_ARSIZE(S01_AXI_ARSIZE), // input wire [2 : 0] S01_AXI_ARSIZE

.S01_AXI_ARBURST(S01_AXI_ARBURST), // input wire [1 : 0] S01_AXI_ARBURST

.S01_AXI_ARLOCK(S01_AXI_ARLOCK), // input wire S01_AXI_ARLOCK

.S01_AXI_ARCACHE(S01_AXI_ARCACHE), // input wire [3 : 0] S01_AXI_ARCACHE

.S01_AXI_ARPROT(S01_AXI_ARPROT), // input wire [2 : 0] S01_AXI_ARPROT

.S01_AXI_ARQOS(S01_AXI_ARQOS), // input wire [3 : 0] S01_AXI_ARQOS

.S01_AXI_ARVALID(S01_AXI_ARVALID), // input wire S01_AXI_ARVALID

.S01_AXI_ARREADY(S01_AXI_ARREADY), // output wire S01_AXI_ARREADY

.S01_AXI_RID(S01_AXI_RID), // output wire [3 : 0] S01_AXI_RID

.S01_AXI_RDATA(S01_AXI_RDATA), // output wire [511 : 0] S01_AXI_RDATA

.S01_AXI_RRESP(S01_AXI_RRESP), // output wire [1 : 0] S01_AXI_RRESP

.S01_AXI_RLAST(S01_AXI_RLAST), // output wire S01_AXI_RLAST

.S01_AXI_RVALID(S01_AXI_RVALID), // output wire S01_AXI_RVALID

.S01_AXI_RREADY(S01_AXI_RREADY), // input wire S01_AXI_RREADY

//chnl 2

.S02_AXI_ARESET_OUT_N(S02_AXI_ARESET_OUT_N), // output wire S02_AXI_ARESET_OUT_N

.S02_AXI_ACLK(clk_75m), // input wire S02_AXI_ACLK

.S02_AXI_AWID(S02_AXI_AWID), // input wire [3 : 0] S02_AXI_AWID

.S02_AXI_AWADDR(S02_AXI_AWADDR), // input wire [31 : 0] S02_AXI_AWADDR

.S02_AXI_AWLEN(S02_AXI_AWLEN), // input wire [7 : 0] S02_AXI_AWLEN

.S02_AXI_AWSIZE(S02_AXI_AWSIZE), // input wire [2 : 0] S02_AXI_AWSIZE

.S02_AXI_AWBURST(S02_AXI_AWBURST), // input wire [1 : 0] S02_AXI_AWBURST

.S02_AXI_AWLOCK(S02_AXI_AWLOCK), // input wire S02_AXI_AWLOCK

.S02_AXI_AWCACHE(S02_AXI_AWCACHE), // input wire [3 : 0] S02_AXI_AWCACHE

.S02_AXI_AWPROT(S02_AXI_AWPROT), // input wire [2 : 0] S02_AXI_AWPROT

.S02_AXI_AWQOS(S02_AXI_AWQOS), // input wire [3 : 0] S02_AXI_AWQOS

.S02_AXI_AWVALID(S02_AXI_AWVALID), // input wire S02_AXI_AWVALID

.S02_AXI_AWREADY(S02_AXI_AWREADY), // output wire S02_AXI_AWREADY

.S02_AXI_WDATA(S02_AXI_WDATA), // input wire [511 : 0] S02_AXI_WDATA

.S02_AXI_WSTRB(S02_AXI_WSTRB), // input wire [63 : 0] S02_AXI_WSTRB

.S02_AXI_WLAST(S02_AXI_WLAST), // input wire S02_AXI_WLAST

.S02_AXI_WVALID(S02_AXI_WVALID), // input wire S02_AXI_WVALID

.S02_AXI_WREADY(S02_AXI_WREADY), // output wire S02_AXI_WREADY

.S02_AXI_BID(S02_AXI_BID), // output wire [3 : 0] S02_AXI_BID

.S02_AXI_BRESP(S02_AXI_BRESP), // output wire [1 : 0] S02_AXI_BRESP

.S02_AXI_BVALID(S02_AXI_BVALID), // output wire S02_AXI_BVALID

.S02_AXI_BREADY(S02_AXI_BREADY), // input wire S02_AXI_BREADY

.S02_AXI_ARID(S02_AXI_ARID), // input wire [3 : 0] S02_AXI_ARID

.S02_AXI_ARADDR(S02_AXI_ARADDR), // input wire [31 : 0] S02_AXI_ARADDR

.S02_AXI_ARLEN(S02_AXI_ARLEN), // input wire [7 : 0] S02_AXI_ARLEN

.S02_AXI_ARSIZE(S02_AXI_ARSIZE), // input wire [2 : 0] S02_AXI_ARSIZE

.S02_AXI_ARBURST(S02_AXI_ARBURST), // input wire [1 : 0] S02_AXI_ARBURST

.S02_AXI_ARLOCK(S02_AXI_ARLOCK), // input wire S02_AXI_ARLOCK

.S02_AXI_ARCACHE(S02_AXI_ARCACHE), // input wire [3 : 0] S02_AXI_ARCACHE

.S02_AXI_ARPROT(S02_AXI_ARPROT), // input wire [2 : 0] S02_AXI_ARPROT

.S02_AXI_ARQOS(S02_AXI_ARQOS), // input wire [3 : 0] S02_AXI_ARQOS

.S02_AXI_ARVALID(S02_AXI_ARVALID), // input wire S02_AXI_ARVALID

.S02_AXI_ARREADY(S02_AXI_ARREADY), // output wire S02_AXI_ARREADY

.S02_AXI_RID(S02_AXI_RID), // output wire [3 : 0] S02_AXI_RID

.S02_AXI_RDATA(S02_AXI_RDATA), // output wire [511 : 0] S02_AXI_RDATA

.S02_AXI_RRESP(S02_AXI_RRESP), // output wire [1 : 0] S02_AXI_RRESP

.S02_AXI_RLAST(S02_AXI_RLAST), // output wire S02_AXI_RLAST

.S02_AXI_RVALID(S02_AXI_RVALID), // output wire S02_AXI_RVALID

.S02_AXI_RREADY(S02_AXI_RREADY), // input wire S02_AXI_RREADY

//chnl 3

.S03_AXI_ARESET_OUT_N(S03_AXI_ARESET_OUT_N), // output wire S03_AXI_ARESET_OUT_N

.S03_AXI_ACLK(clk_75m), // input wire S03_AXI_ACLK

.S03_AXI_AWID(S03_AXI_AWID), // input wire [3 : 0] S03_AXI_AWID

.S03_AXI_AWADDR(S03_AXI_AWADDR), // input wire [31 : 0] S03_AXI_AWADDR

.S03_AXI_AWLEN(S03_AXI_AWLEN), // input wire [7 : 0] S03_AXI_AWLEN

.S03_AXI_AWSIZE(S03_AXI_AWSIZE), // input wire [2 : 0] S03_AXI_AWSIZE

.S03_AXI_AWBURST(S03_AXI_AWBURST), // input wire [1 : 0] S03_AXI_AWBURS

.S03_AXI_AWLOCK(S03_AXI_AWLOCK), // input wire S03_AXI_AWLOCK

.S03_AXI_AWCACHE(S03_AXI_AWCACHE), // input wire [3 : 0] S03_AXI_AWCACHE

.S03_AXI_AWPROT(S03_AXI_AWPROT), // input wire [2 : 0] S03_AXI_AWPROT

.S03_AXI_AWQOS(S03_AXI_AWQOS), // input wire [3 : 0] S03_AXI_AWQOS

.S03_AXI_AWVALID(S03_AXI_AWVALID), // input wire S03_AXI_AWVALID

.S03_AXI_AWREADY(S03_AXI_AWREADY), // output wire S03_AXI_AWREADY

.S03_AXI_WDATA(S03_AXI_WDATA), // input wire [511 : 0] S03_AXI_WDATA

.S03_AXI_WSTRB(S03_AXI_WSTRB), // input wire [63 : 0] S03_AXI_WSTRB

.S03_AXI_WLAST(S03_AXI_WLAST), // input wire S03_AXI_WLAST

.S03_AXI_WVALID(S03_AXI_WVALID), // input wire S03_AXI_WVALID

.S03_AXI_WREADY(S03_AXI_WREADY), // output wire S03_AXI_WREADY

.S03_AXI_BID(S03_AXI_BID), // output wire [3 : 0] S03_AXI_BID

.S03_AXI_BRESP(S03_AXI_BRESP), // output wire [1 : 0] S03_AXI_BRESP

.S03_AXI_BVALID(S03_AXI_BVALID), // output wire S03_AXI_BVALID

.S03_AXI_BREADY(S03_AXI_BREADY), // input wire S03_AXI_BREADY

.S03_AXI_ARID(S03_AXI_ARID), // input wire [3 : 0] S03_AXI_ARID

.S03_AXI_ARADDR(S03_AXI_ARADDR), // input wire [31 : 0] S03_AXI_ARADDR

.S03_AXI_ARLEN(S03_AXI_ARLEN), // input wire [7 : 0] S03_AXI_ARLEN

.S03_AXI_ARSIZE(S03_AXI_ARSIZE), // input wire [2 : 0] S03_AXI_ARSIZE

.S03_AXI_ARBURST(S03_AXI_ARBURST), // input wire [1 : 0] S03_AXI_ARBURST

.S03_AXI_ARLOCK(S03_AXI_ARLOCK), // input wire S03_AXI_ARLOCK

.S03_AXI_ARCACHE(S03_AXI_ARCACHE), // input wire [3 : 0] S03_AXI_ARCACHE

.S03_AXI_ARPROT(S03_AXI_ARPROT), // input wire [2 : 0] S03_AXI_ARPROT

.S03_AXI_ARQOS(S03_AXI_ARQOS), // input wire [3 : 0] S03_AXI_ARQOS

.S03_AXI_ARVALID(S03_AXI_ARVALID), // input wire S03_AXI_ARVALID

.S03_AXI_ARREADY(S03_AXI_ARREADY), // output wire S03_AXI_ARREADY

.S03_AXI_RID(S03_AXI_RID), // output wire [3 : 0] S03_AXI_RID

.S03_AXI_RDATA(S03_AXI_RDATA), // output wire [511 : 0] S03_AXI_RDATA

.S03_AXI_RRESP(S03_AXI_RRESP), // output wire [1 : 0] S03_AXI_RRESP

.S03_AXI_RLAST(S03_AXI_RLAST), // output wire S03_AXI_RLAST

.S03_AXI_RVALID(S03_AXI_RVALID), // output wire S03_AXI_RVALID

.S03_AXI_RREADY(S03_AXI_RREADY), // input wire S03_AXI_RREADY

//master

//ddr4 awaddr

.M00_AXI_ARESET_OUT_N(c0_ddr4_aresetn_n), // output wire M00_AXI_ARESET_OUT_N

.M00_AXI_ACLK(c0_ddr4_clk), // input wire M00_AXI_ACLK

.M00_AXI_AWID(c0_ddr4_s_axi_awid), // output wire [7 : 0] M00_AXI_AWID

.M00_AXI_AWADDR(c0_ddr4_s_axi_awaddr), // output wire [31 : 0] M00_AXI_AWADDR

.M00_AXI_AWLEN(c0_ddr4_s_axi_awlen), // output wire [7 : 0] M00_AXI_AWLEN

.M00_AXI_AWSIZE(c0_ddr4_s_axi_awsize), // output wire [2 : 0] M00_AXI_AWSIZE

.M00_AXI_AWBURST(c0_ddr4_s_axi_awburst), // output wire [1 : 0] M00_AXI_AWBURST

.M00_AXI_AWLOCK(c0_ddr4_s_axi_awlock), // output wire M00_AXI_AWLOCK

.M00_AXI_AWCACHE(c0_ddr4_s_axi_awcache), // output wire [3 : 0] M00_AXI_AWCACHE

.M00_AXI_AWPROT(c0_ddr4_s_axi_awprot), // output wire [2 : 0] M00_AXI_AWPROT

.M00_AXI_AWQOS(c0_ddr4_s_axi_awqos), // output wire [3 : 0] M00_AXI_AWQOS

.M00_AXI_AWVALID(c0_ddr4_s_axi_awvalid), // output wire M00_AXI_AWVALID

.M00_AXI_AWREADY(c0_ddr4_s_axi_awready), // input wire M00_AXI_AWREADY

//ddr4 wdata

.M00_AXI_WDATA(c0_ddr4_s_axi_wdata), // output wire [511 : 0] M00_AXI_WDATA

.M00_AXI_WSTRB(c0_ddr4_s_axi_wstrb), // output wire [63 : 0] M00_AXI_WSTRB

.M00_AXI_WLAST(c0_ddr4_s_axi_wlast), // output wire M00_AXI_WLAST

.M00_AXI_WVALID(c0_ddr4_s_axi_wvalid), // output wire M00_AXI_WVALID

.M00_AXI_WREADY(c0_ddr4_s_axi_wready), // input wire M00_AXI_WREADY

//ddr4 w bresp

.M00_AXI_BID(c0_ddr4_s_axi_bid), // input wire [7 : 0] M00_AXI_BID

.M00_AXI_BRESP(c0_ddr4_s_axi_bresp), // input wire [1 : 0] M00_AXI_BRESP

.M00_AXI_BVALID(c0_ddr4_s_axi_bvalid), // input wire M00_AXI_BVALID

.M00_AXI_BREADY(c0_ddr4_s_axi_bready), // output wire M00_AXI_BREADY

//ddr4 araddr

.M00_AXI_ARID(c0_ddr4_s_axi_arid), // output wire [7 : 0] M00_AXI_ARID

.M00_AXI_ARADDR(c0_ddr4_s_axi_araddr), // output wire [31 : 0] M00_AXI_ARADDR

.M00_AXI_ARLEN(c0_ddr4_s_axi_arlen), // output wire [7 : 0] M00_AXI_ARLEN

.M00_AXI_ARSIZE(c0_ddr4_s_axi_arsize), // output wire [2 : 0] M00_AXI_ARSIZE

.M00_AXI_ARBURST(c0_ddr4_s_axi_arburst), // output wire [1 : 0] M00_AXI_ARBURST

.M00_AXI_ARLOCK(c0_ddr4_s_axi_arlock), // output wire M00_AXI_ARLOCK

.M00_AXI_ARCACHE(c0_ddr4_s_axi_arcache), // output wire [3 : 0] M00_AXI_ARCACHE

.M00_AXI_ARPROT(c0_ddr4_s_axi_arprot), // output wire [2 : 0] M00_AXI_ARPROT

.M00_AXI_ARQOS(c0_ddr4_s_axi_arqos), // output wire [3 : 0] M00_AXI_ARQOS

.M00_AXI_ARVALID(c0_ddr4_s_axi_arvalid), // output wire M00_AXI_ARVALID

.M00_AXI_ARREADY(c0_ddr4_s_axi_arready), // input wire M00_AXI_ARREADY

//ddr4 rdata

.M00_AXI_RID(c0_ddr4_s_axi_rid), // input wire [7 : 0] M00_AXI_RID

.M00_AXI_RDATA(c0_ddr4_s_axi_rdata), // input wire [511 : 0] M00_AXI_RDATA

.M00_AXI_RRESP(c0_ddr4_s_axi_rresp), // input wire [1 : 0] M00_AXI_RRESP

.M00_AXI_RLAST(c0_ddr4_s_axi_rlast), // input wire M00_AXI_RLAST

.M00_AXI_RVALID(c0_ddr4_s_axi_rvalid), // input wire M00_AXI_RVALID

.M00_AXI_RREADY(c0_ddr4_s_axi_rready) // output wire M00_AXI_RREADY

);

例化说明:IP核系统时钟由DDR4的用户时钟提供。IP核的系统复位为低有效复位,由ddr4输出的用户复位信号取反得到。

四个通道的信号连接到四个通道测试模块,四个测试模块为axi主端口,与IP核的从端口交互。DDR4为axi从端口,与ip核的主端口交互。

为了测试在不同的时钟域时的读写情况,0、2、3通道为75MHz时钟,1通道为125MHz时钟。IP核的四个从端口输出低有效复位信号。供四个通道使用。

四、仿真测试:

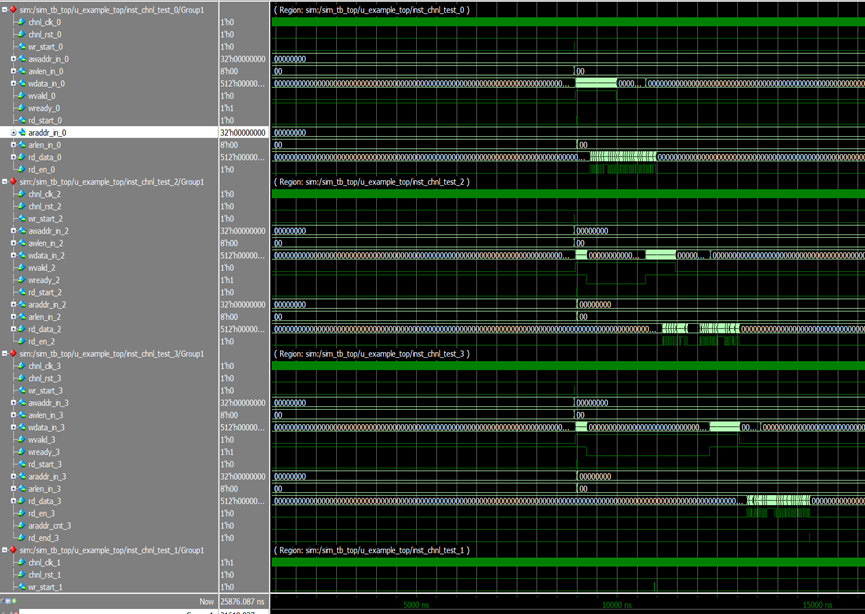

在测试模块中,在同一时刻在不同的起始地址写入128个数据,并在同一时刻在不同的起始地址读出128个数据。

下图为测试通道0、2、3的读写数据波形,可以看到三个通道同时发起读写请求,然后根据通道顺序决定仲裁。通道号越小,优先级越高。

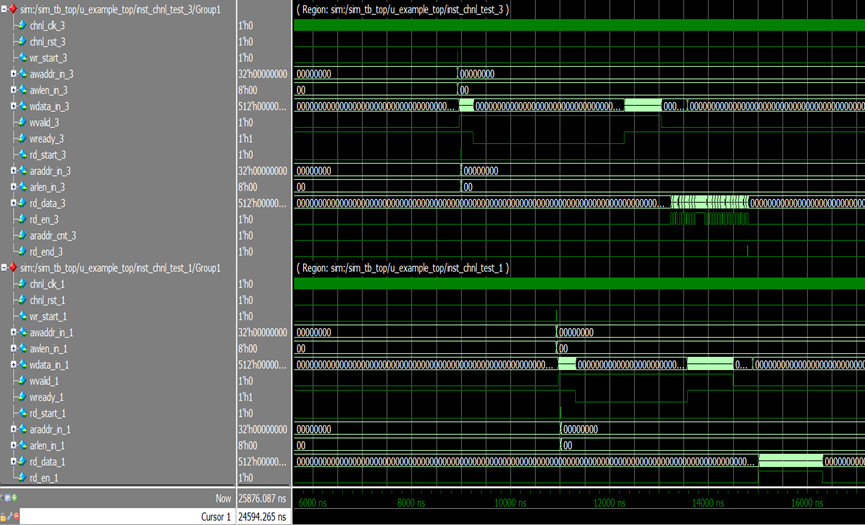

下图为通道1和通道3的读写测试波形,由于通道1的读写请求最晚,所以通道1的响应优先级最小。

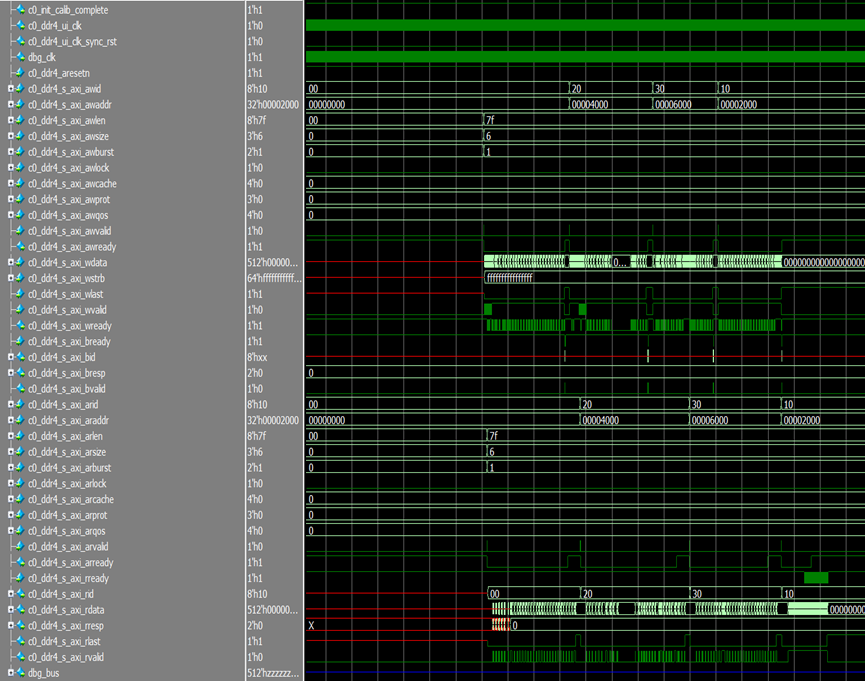

下图为DDR4接口的波形图,可以看到经过interconnect后,将每个读写请求依次进行。因为同时只能读或只能写,所以在读写未完成时交替操作。

本文章由威三学社出品

对课程感兴趣可以私信联系