西安市免费做网站提高工作效率8个方法

一、什么是缓存一致性

缓存一致性关注的是同一个数据在多个高速缓存和内存中的一致性问题。那为什么会产生缓存一致性问题呢?

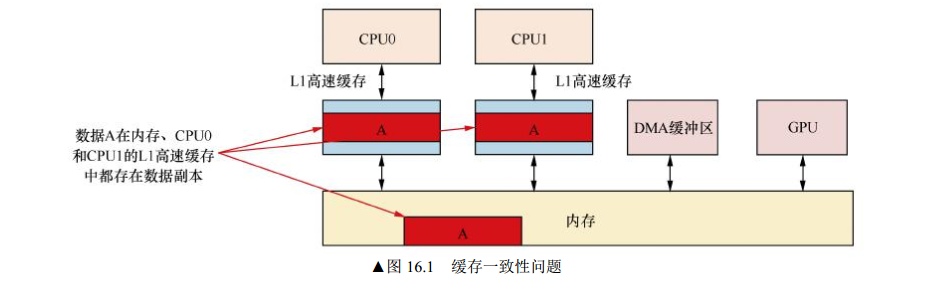

举个例子:CPU0 有自己的 L1 高速缓存, CPU1 也有自己的 L1 高速缓存。 如果 CPU0率先访问内存地址 A, 这个地址的数据就会加载到 CPU0 的 L1 高速缓存里。 如果 CPU1 也想访问这个数据,那应该怎么办呢?它应该从内存中读,还是向 CPU0 要数据呢?这种情况下就产生了缓存一致性问题。因为内存地址 A 的数据在系统中存在两个副本,一个在内存地址 A 中,另一个在 CPU0 本地的 L1 高速缓存里。如果 CPU0 修改了本地的 L1 高速缓存的数据, 那么这两个数据副本就不一致,此时就出现了缓存一致性问题。如下图所示:

数据 A 在三个地方——内存、 CPU0 的高速缓存、 CPU1 的高速缓存。这个系统有 4 个观察者(observer)——CPU0、 CPU1、 DMA 缓冲区以及 GPU,那么在 4 个观察者眼中, 内存 A 的数据会是一致的吗?有没有可能产生不一致的情况呢?这就是缓存一致性的问题,包括了核与核之间的缓存一致性、 DMA 缓冲区和高速缓存之间的一致性等。

二、系统缓存一致性问题

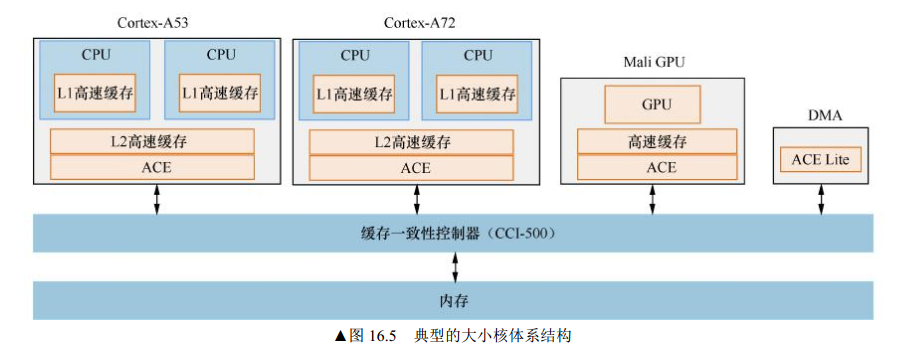

现在 ARM 系统越来越复杂了,从多核发展到多簇,例如大小核体系结构等。下图所示是一个典型的大小核体系结构, 小核由 Cortex-A53 组成, 大核由 Cortex-A72 组成, 两个 Core-A53内核构成了一个 CPU 簇。在一个 CPU 簇里,每个 CPU 都有各自独立的 L1 高速缓存,共享一个 L2 高速缓存, 然后通过一个 ACE 的硬件单元连接到缓存一致性控制器(例如 CCI-500)里。ACE(AXI Coherent Extension)是 AMBA 4 协议中定义的。在这个系统里,除 CPU 之外,还有 GPU,比如 ARM 公司的 Mali GPU。 此外, 还有一些带有 DMA 功能的外设等, 这些设备都有独立访问内存的能力, 因此它们也必须通过 ACE 接口来连接到这个缓存一致性总线上。 这个缓存一致性总线就是用来实现系统级别的缓存一致性的

三、缓存一致性的解决方案

解决缓存一致性问题,通常有 3 种方案。

- 关闭高速缓存。

- 软件维护缓存一致性。

- 硬件维护缓存一致性。

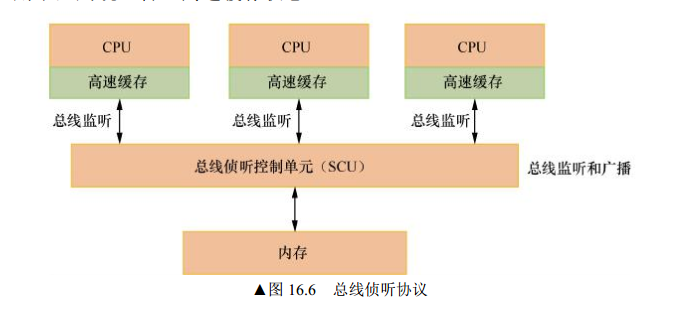

这里只讲第三种。对于多核间的缓存一致性,通常的做法就是在多核里实现一个 MESI 协议,实现一种总线侦听的控制单元,例如 ARM 的 SCU。

对于系统级别的缓存一致性,需要实现一种缓存一致性总线协议。在 2011 年, ARM 公司

在 AMBA 4 协议里提出了 AXI 总线缓存一致性扩展(AXI Coherency Extension, ACE)协议。

ACE 协议用来实现 CPU 簇之间的缓存一致性。另外, ACE Lite 协议用来实现 I/O 设备(比如DMA、 GPU 等)的缓存一致性

3.1 MESI 协议

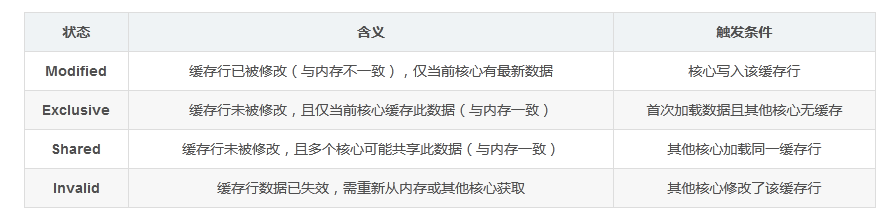

MESI(Modified, Exclusive, Shared, Invalid)是最经典的缓存一致性协议,通过状态机管理缓存行状态。

2. 状态转换与总线消息

总线嗅探(Bus Snooping):每个核心监听总线上的读写操作,根据消息更新自身缓存状态。

关键总线消息:

Read:请求读取某内存地址。

Read Response:响应Read请求,提供数据。

Invalidate:要求其他核心使对应缓存行失效。

Writeback:将Modified状态的数据写回内存。

3. 典型操作流程

核心A读取数据X:

若其他核心无X的缓存,A的缓存行状态为Exclusive。

若其他核心有X的缓存,状态为Shared。

核心A写入数据X:

若原状态为Exclusive,直接修改为Modified。

若原状态为Shared,需发送Invalidate消息使其他核心的缓存失效,再修改为Modified。

核心B读取被A修改的X:

A检测到Read消息,将Modified数据写回内存,B加载后状态为Shared

3.2 转换图

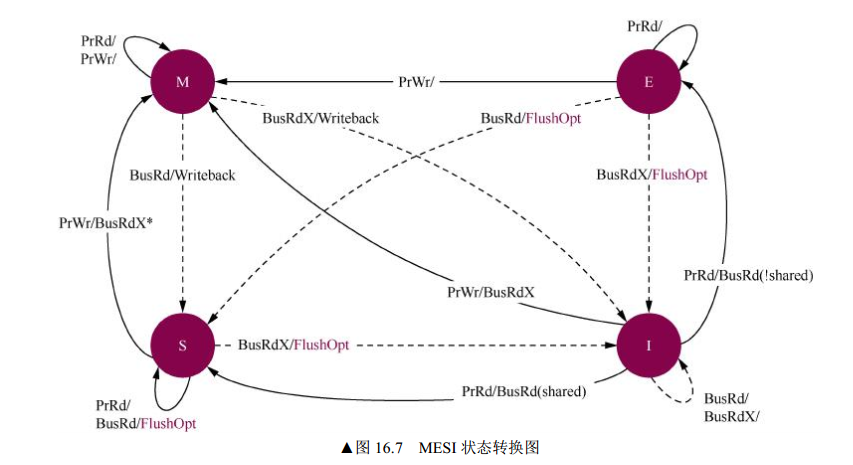

MESI 状态转换图如上图 所示,实线表示处理器请求响应,虚线表示总线监听响应。那如何解读这个图呢?

当本地 CPU 的高速缓存行的状态为 I 时,若 CPU 发出 PrRd 请求,本地缓存未命中,则在总线上产生一个 BusRd 信号。 其他 CPU 会监听到该请求并且检查它们的缓存来判断是否拥有了该副本。下面分两种情况来考虑。

1、如果 CPU 发现本地副本, 并且这个高速缓存行的状态为 S,见图 16.7 中从 I 状态到 S

状态的“PrRd/BusRd(shared)”实线箭头,那么在总线上回复一个 FlushOpt 信号, 即

把当前的高速缓存行发送到总线上,高速缓存行的状态还是 S,见 S 状态的“PrRd/BusRd/FlushOpt”实线箭头。

2、如果 CPU 发现本地副本并且高速缓存行的状态为 E,见图 16.7 中从 I 状态到 E 状态的

“PrRd/BusRd(!shared)” 实线箭头, 则在总线上回应 FlushOpt 信号, 即把当前的高速缓

存行发送到总线上, 高速缓存行的状态变成 S, 见 E 状态到 S 状态的“BusRd/FlushOpt”

虚线箭头。

参考:

CPU多级缓存与缓存一致性协议-CSDN博客

https://zhuanlan.zhihu.com/p/15183216054