web程序设计asp.net实用网站开发答案十大流量平台

目录

一、基本概述

1.1 DDS简介

1.2 DDS工作原理

1.2.1 核心组成部分

1.2.2 工作流程

1.2.3 输出频率计算

1.3 常见的RAM、ROM、FIFO等IP核的参数设置和调用过程

1.3.1 RAM IP核的参数设置和调用过程

1.3.2 ROM IP核的参数设置和调用过程

1.3.3 FIFO IP核的参数设置和调用过程

二、波形仿真器的设计与制作

2.1 内容与要求

2.2 具体步骤

2.2.1 相位累加器

2.2.2 波形存储器ROM

2.2.3 顶层电路设计

三、DE2-115设计实现

一、基本概述

1.1 DDS简介

DDS信号发生器即直接数字频率合成(Direct Digital Frequency Synthesis,简称DDS)是一种利用数字技术生成信号的方法。它通过数字信号处理技术,将数字信号转换为模拟信号,从而生成高质量的正弦波、方波、三角波等信号。

1.2 DDS工作原理

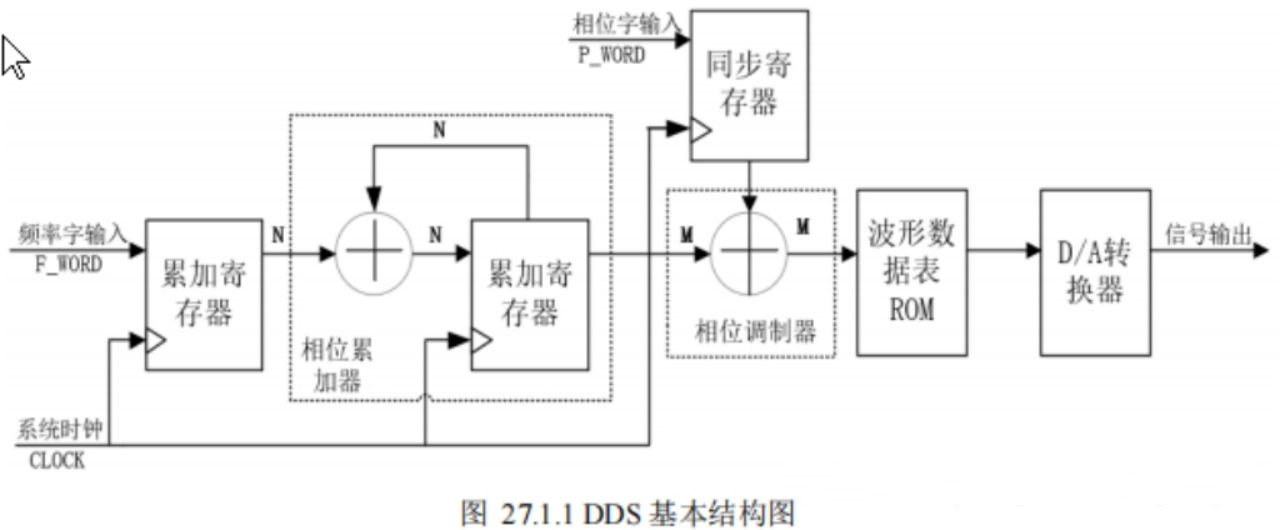

1.2.1 核心组成部分

DDS系统主要由以下几个模块构成:

·相位累加器(Phase Accumulator)

· 波形查找表(Waveform Look-Up Table, LUT)

· 数模转换器(DAC)

· 低通滤波器(LPF)

1.2.2 工作流程

(1)相位累加

相位累加器是DDS信号发生器的核心部分,用于生成相位信息。它由一个累加器和一个频率控制字(Frequency Control Word, FCW)组成。每次时钟周期,频率控制字会被加到累加器中,累加器的输出即为当前的相位值。

· 输入:频率控制字(Frequency Tuning Word, FTW),由用户设定。

· 作用:相位累加器在时钟信号(fclkfclk)的驱动下,对FTW进行累加,生成线性递增的相位值(地址)。

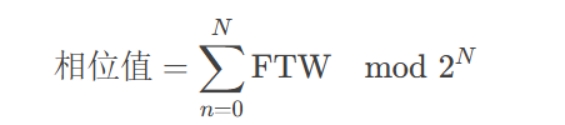

· 公式:

其中,NN 为相位累加器的位数(通常24~32位),决定频率分辨率。

(2)波形查找

查找表(Lookup Table, LUT)存储了正弦波或其他波形的幅度值。相位累加器的输出作为查找表的地址,查找表根据该地址输出对应的幅度值。查找表通常存储的是一个完整周期的波形数据。波形选择模块用于选择不同的波形,如正弦波、方波、三角波等。通过改变查找表的内容或逻辑控制,可以生成不同的波形。

· 波形存储器(LUT):预存目标波形(如正弦波、方波)的离散采样值。

· 寻址:相位累加器的输出作为地址,从LUT中读取对应的波形幅值数据。

· 分辨率:LUT的深度和位宽影响波形精度。

(3)数模转换(DAC)

DAC将数字幅度值转换为模拟信号。DAC的分辨率(如8位、12位、16位)决定了输出信号的精度和质量。

· 将查找表输出的数字幅值转换为模拟电压信号。

· DAC的转换速度和位数直接影响输出信号的质量(如信噪比、谐波失真)。

(4)低通滤波

· 滤除DAC输出的高频量化噪声和时钟馈通信号。

· 截止频率通常略高于所需信号的最大频率。

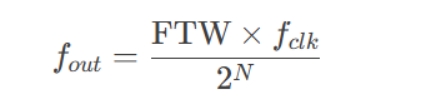

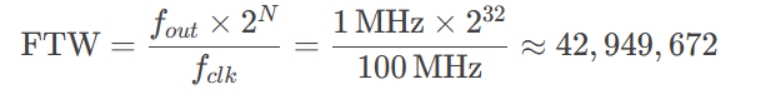

1.2.3 输出频率计算

DDS的输出频率由以下公式决定:

· fclkfclk:系统时钟频率(如100 MHz)。

· NN:相位累加器位数(如32位)。

· FTW:频率控制字,由用户编程设置。

比如: 若 fclk=100 MHzfclk=100MHz,N=32N=32,要输出 1 MHz1MHz 正弦波:

1.3 常见的RAM、ROM、FIFO等IP核的参数设置和调用过程

IP软核是预先设计好的、可重复使用的数字电路模块,用于简化复杂系统的设计。它们通常以Verilog HDL或VHDL等硬件描述语言编写,可以在FPGA或ASIC中实现。

1.3.1 RAM IP核的参数设置和调用过程

RAM 是随机存取存储器(Random Access Memory)的简称,是一个易失性存储器。 RAM 工作时可以随时从任何一个指定的地址写入或读出数据,同时我们还能修改其存储的数据,即写入新的数据,这是 ROM 所并不具备的功能。在 FPGA 中这也是其与 ROM 的最大区别。ROM 是只读存储器,而 RAM 是可写可读存储器,在我们 FPGA 中使用这两个存储器主要也是要区分这一点,因为这两个存储器使用的都是我们 FPGA 内部的 RAM 资源,不同的是 ROM 是只用到了 RAM 资源的读数据端口。

单端口RAM参数:

· 数据宽度(Data Width):8/16/32/64位等

· 存储深度(Depth):根据需求设置(如1024, 2048等)

· 操作模式:通常为"Write First"、"Read First"或"No Change"

· 初始化文件:可加载.mif或.hex文件初始化RAM内容

· 寄存器选项:输出是否寄存(增加一个时钟周期延迟但提高时序性能)

双端口RAM参数:

除单端口参数外还需设置:

端口A和端口B的操作模式

是否允许同时读写

冲突解决策略

1.3.2 ROM IP核的参数设置和调用过程

ROM 是只读存储器(Read-Only Memory)的简称,是一种只能读出事先所存数据的固态半导体存储器。其特性是一旦储存资料就无法再将之改变或删除,且资料不会因为电源关闭而消失。而事 实上在 FPGA 中通过 IP 核生成的 ROM 或 RAM(RAM 将在下一节为大家讲解)调用的都是FPGA 内部的 RAM 资源,掉电内容都会丢失(这也很容易解释,FPGA 芯片内部本来就没有掉电非易失存储器单元)。用 IP 核生成的 ROM 模块只是提前添加了数据文件(.coe 格式)(.mf/.nex格式),在 FPGA 运行时通过数据文件给 ROM 模块初始化,才使得 ROM 模块像个“真正”的掉电非易失存储器;也正是这个原因,ROM 模块的内容必须提前在数据文件中写死,无法在电路中修改。

常见参数设置

· 数据宽度:同RAM

· 存储深度:同RAM

· 初始化文件:必须提供.mif或.hex文件

· 输出寄存器:可选是否寄存输出

1.3.3 FIFO IP核的参数设置和调用过程

FIFO(First In First Out,即先入先出),是一种数据缓冲器,用来实现数据先入先出的读写方式。与 ROM 或 RAM 的按地址读写方式不同,FIFO 的读写遵循“先进先出”的原则,即数据按顺序写入 FIFO,先被写入的数据同样在读取的时候先被读出,所以 FIFO存储器没有地址线。FIFO 有一个写端口和一个读端口外部无需使用者控制地址,使用方便。

FIFO 存储器主要是作为缓存,应用在同步时钟系统和异步时钟系统中,在很多的设计中都会使用,后面实例中如:多比特数据做跨时钟域的转换、前后带宽不同步等都用到了FIFO。FIFO 根据读写时钟是否相同,分为 SCFIFO(同步 FIFO)和 DCFIFO(异步FIFO),SCFIFO 的读写为同一时钟,应用在同步时钟系统中;DCFIFO 的读写时钟不同,应用在异步时钟系统中。

数据的产生模块与数据使用模块不对应时就会使用到FIFO,如两者的时钟频率不同无法在同一时钟下进行传输(多比特数据做跨时钟域的转换) ;两者的数据带宽不同下传输(前后带宽不同步)。

基本参数:

· FIFO实现方式:基于Block RAM或Distributed RAM

· 数据宽度:8/16/32/64位等

· FIFO深度:16/32/64/128/256等

· 满/空标志:设置几乎满/几乎空的阈值

高级参数:

· 读写时钟域:同步或异步FIFO

· 握手信号:可选是否添加数据有效信号

· 复位类型:同步或异步复位

二、波形仿真器的设计与制作

2.1 内容与要求

采用数字频率合成(Direct Digital FrequencySynthesis,简称DDS)设计制作一个波形发生器,仿真后,在DE2-115开发板上实践。要求: 1)利用DDS技术合成正弦波和方波; 2)输出信号的频率范围为10Hz~5MHz,最小频率分辨率小于1kHz; 3)使用嵌入式逻辑分析仪SignalTap II实时测试输出波形的离散数据。

2.2 具体步骤

(1)在Quartus中创建新工程,步骤在之前的博客中有具体说明

2.2.1 相位累加器

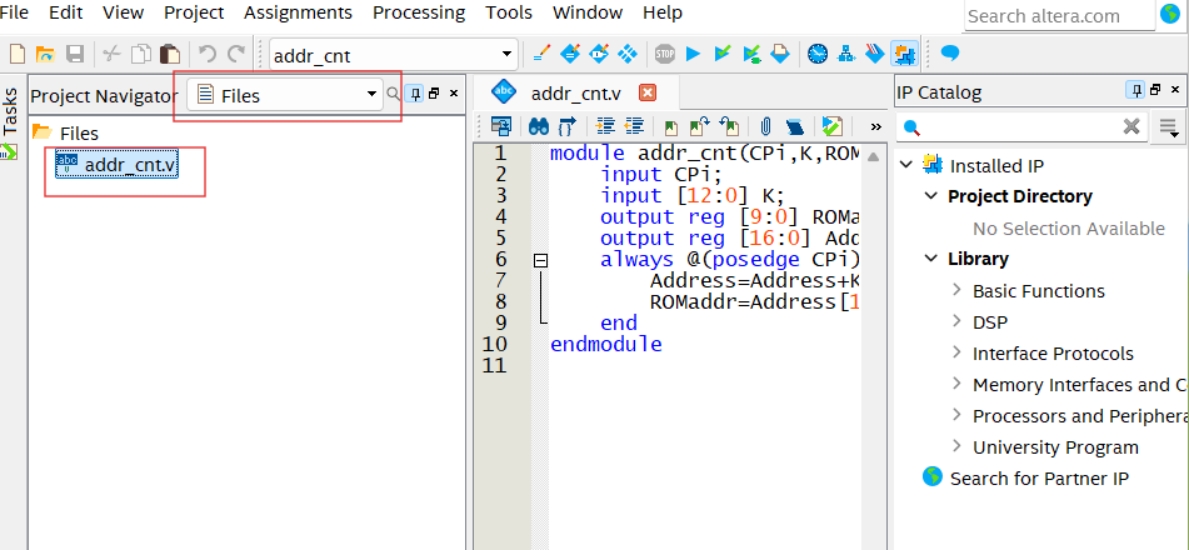

(2)编写代码

module addr_cnt(CPi,K,ROMaddr,Address);

input CPi;

input [12:0] K;

output reg [9:0] ROMaddr;

output reg [16:0] Address;

always @(posedge CPi) begin

Address=Address+K;

ROMaddr=Address[16:7];

end

endmodule(3)将 addr_cnt 设置为顶层文件

将Project Navigator 设置为 Files ,之后右键addr_cnt.v ,选中 Set as Top-Level Entity

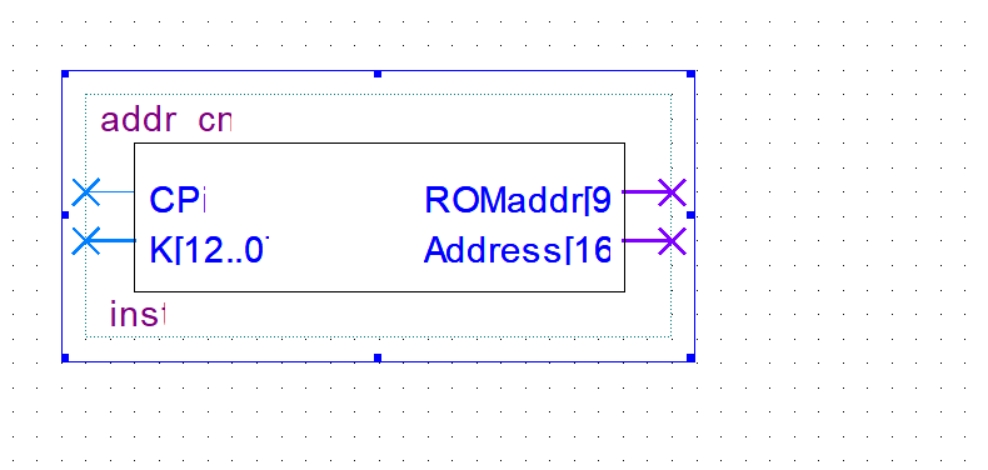

打开生成的.bsf文件如下图所示:

生成并打开.bsf文件

右键addr_cnt.v,在弹出的选项中选择 *Create Symbol Files for Current File,*之后生成的 .bsf 文件会保存在工程目录下,找到对应的文件打开即可

2.2.2 波形存储器ROM

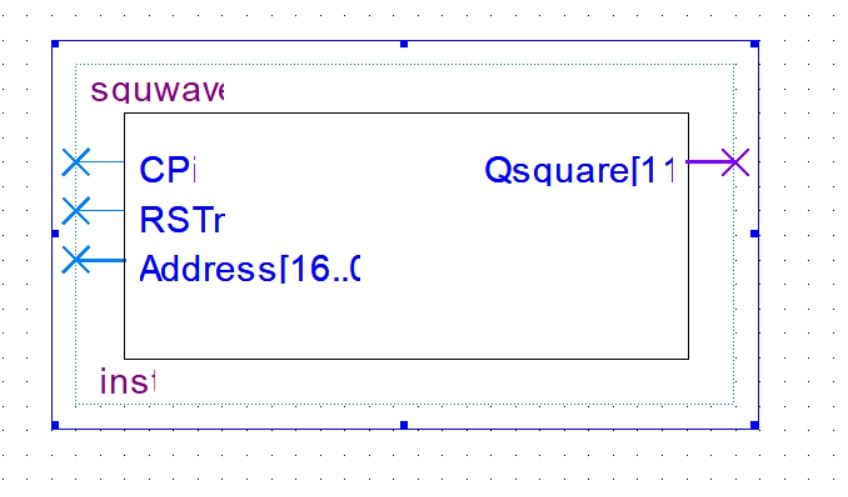

方波模块

代码如下:

module squwave(CPi,RSTn,Address,Qsquare);

input CPi;

input RSTn;

input [16:0] Address;

output reg [11:0] Qsquare;

always @(posedge CPi)

if (!RSTn)Qsquare=12'h000;

else begin

if(Address<=17'h0FFFF)

Qsquare=12'hFFF;

else Qsquare=12'h000;

end

endmodule将该模块设置为顶层文件,并编译生成 .bsf 如下图:

正弦波形存储器

首先编译一个C程序( Dev C++ 或者别的编译器都行),编译之前建议先在对应的Quartus工程目录下新建一个文件夹,将C程序保存在该文件夹内

/myMIF.c/

#include <stdio.h>

#include <math.h>

#define PI 3.141592

#define DEPTH 1024

#define WIDTH 12

int main(void)

{

int n,temp;

float v;

FILE *fp;

fp=fopen("Sine1024.mif","w+");

if(NULL==fp)printf("Can not creat file!\r\n");

else

{

printf("File created successfully!\n");

fprintf(fp,"DEPTH=%d;\n",DEPTH);

fprintf(fp,"WIDTH=%d;\n",WIDTH);

fprintf(fp,"ADDRESS_RADIX=HEX;\n");

fprintf(fp,"DATA_RADIX=HEX;\n");

fprintf(fp,"CONTENT\n");

fprintf(fp,"BEGIN\n");

for(n=0;n<DEPTH;n++)

{

v=sin(2*PI*n/DEPTH);

temp=(int)((v+1)*4095/2);

fprintf(fp,"%04x : %03x;\n",n,temp);

}

fprintf(fp,"END;\n");

fclose(fp);

}

} 编译运行以上代码,会生成 myMIF.exe文件以及Sine 1024.mif 文件,如下图:

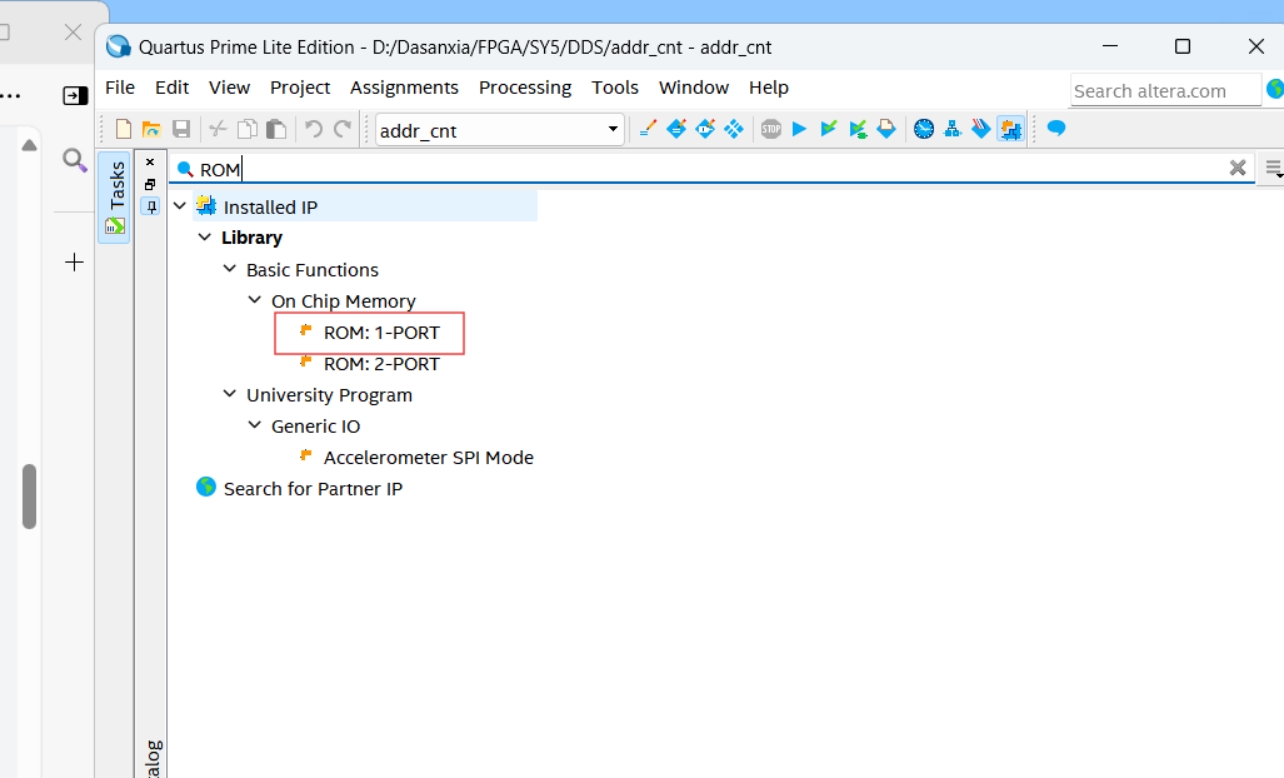

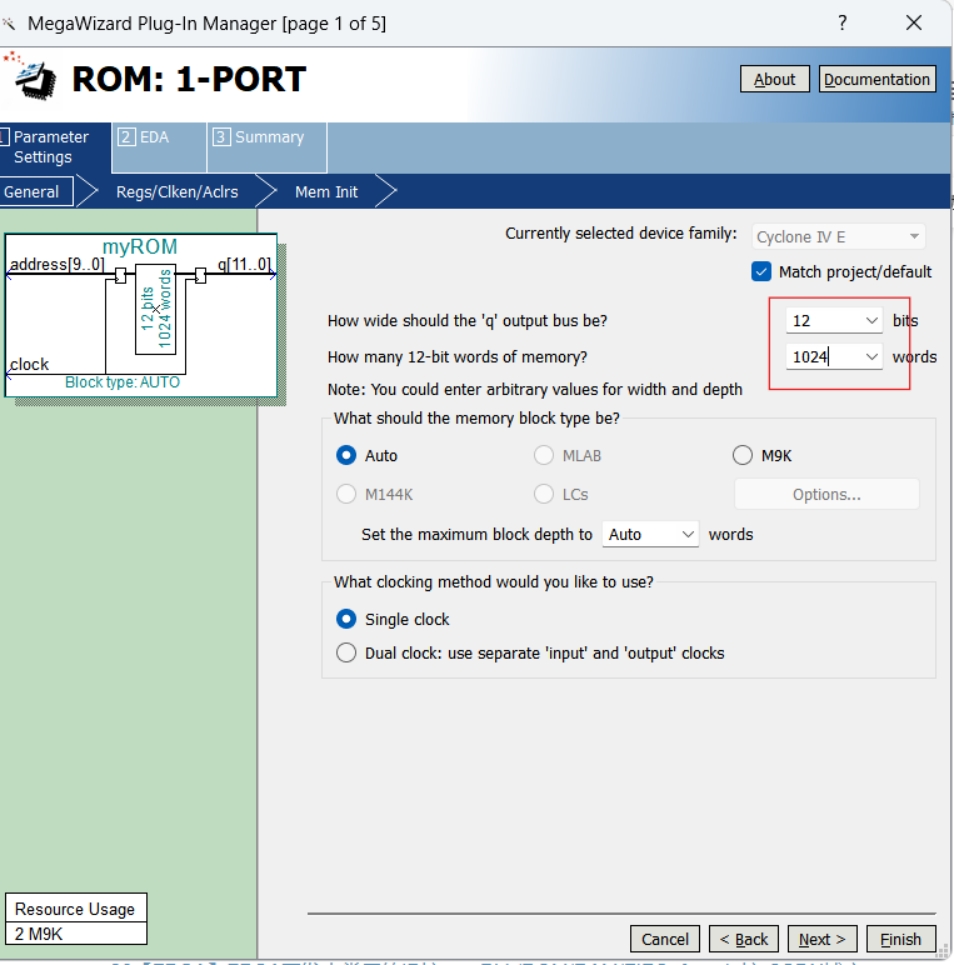

使用Quartus调用LPM_ROM定制正弦波形存储器:点击Tools--->IP Catalog,并在IP Catalog搜索框搜索 ROM ,双击 找到 ROM 1-PORT并双击

在弹出的弹框里面修改命名,如下图所示:

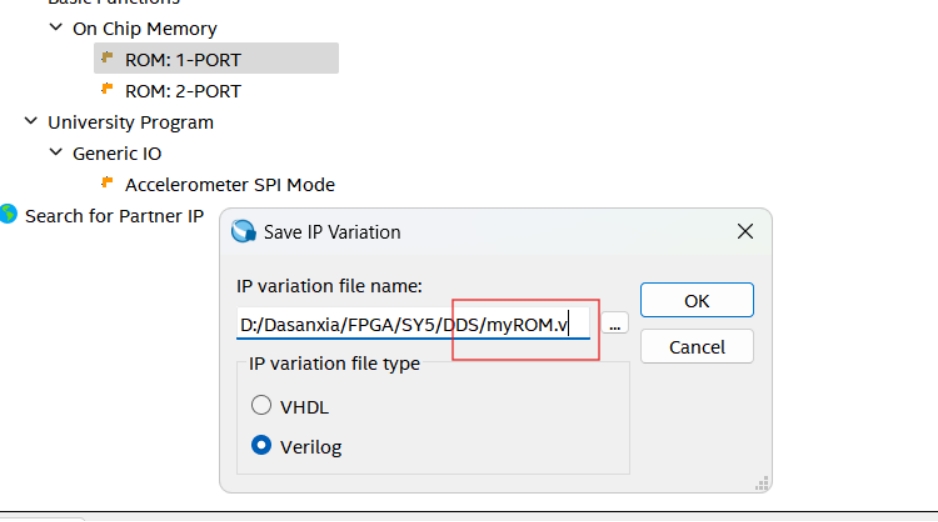

点击OK,会弹出如下界面:

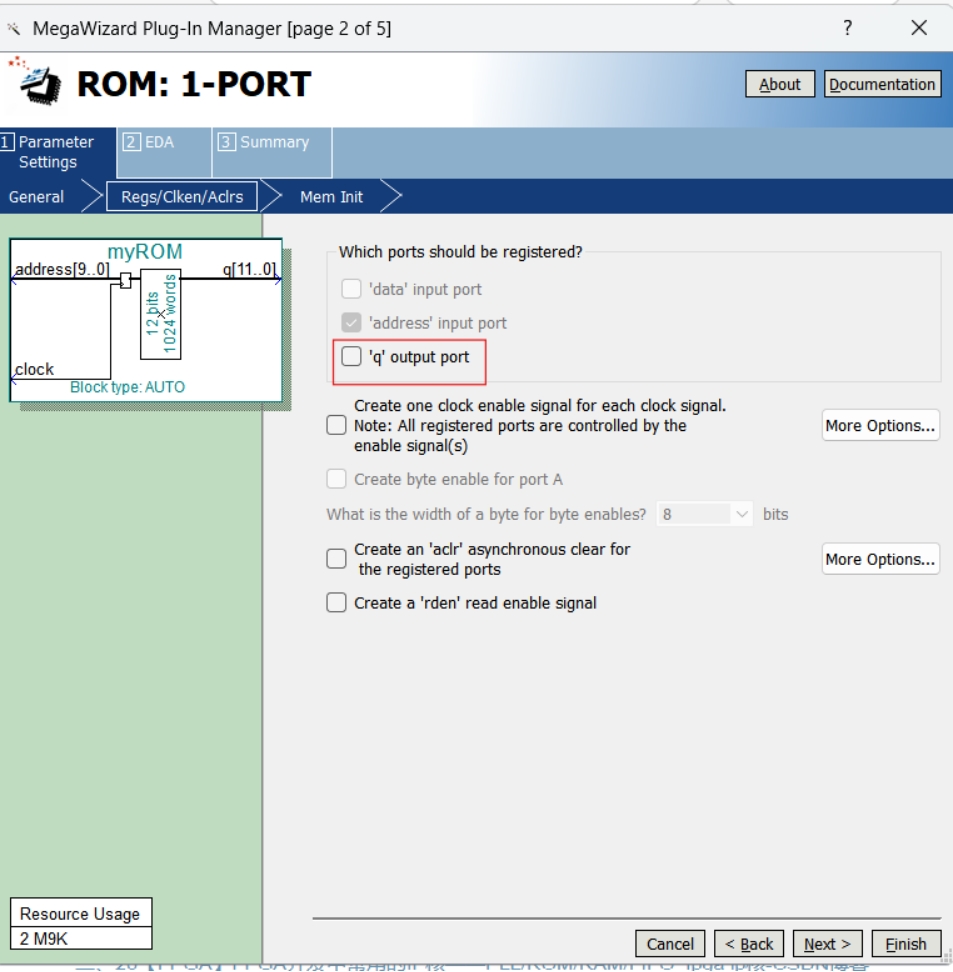

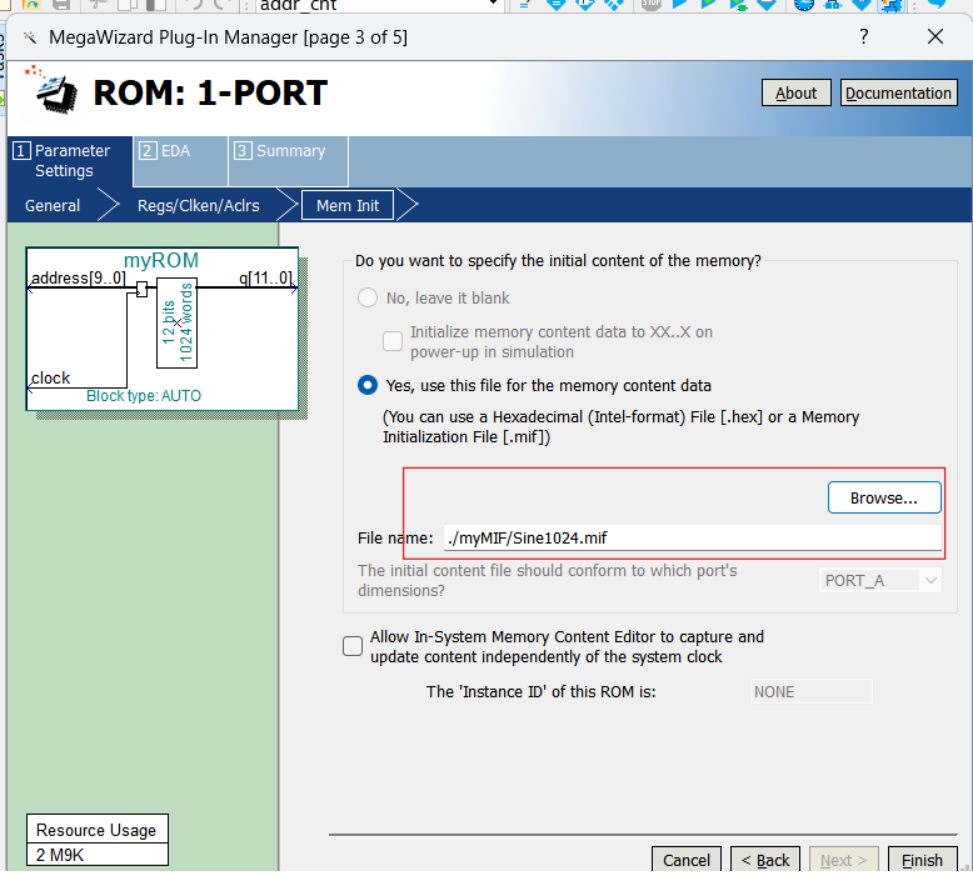

修改以下参数:

取消 ‘q’output port的勾选

点击 Browse..,并选中之前生成好的 Sine1024.mif

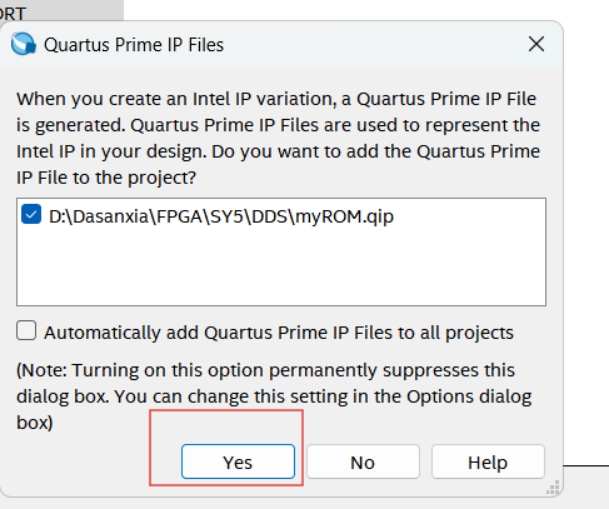

之后一直Next,直到 Finish,ROM配置完成

锁相环倍频电路

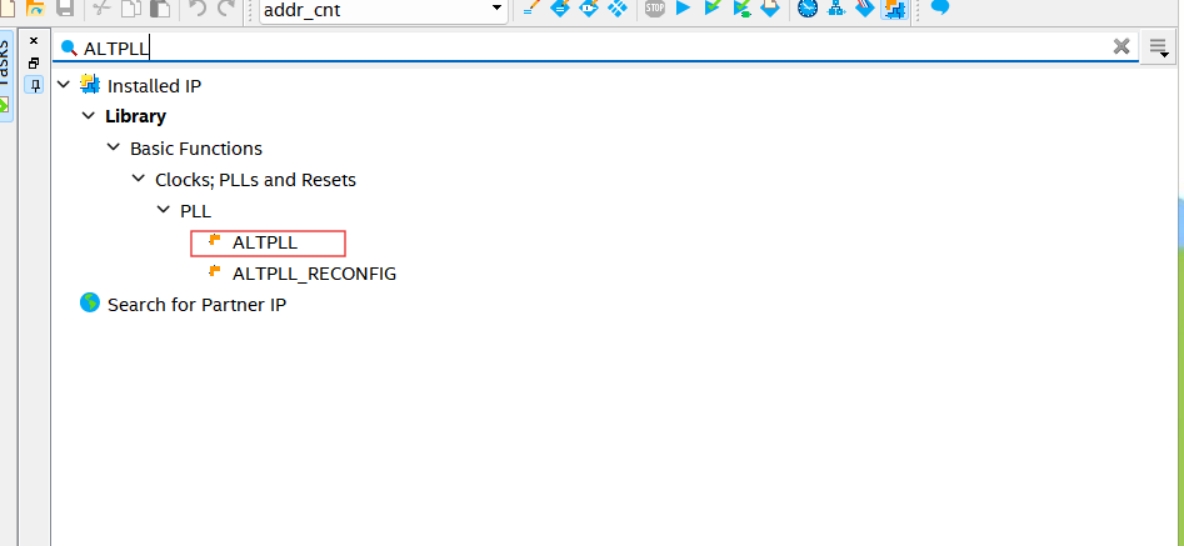

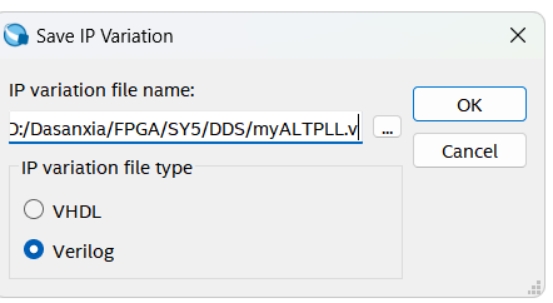

在IP Catalog 搜索栏中搜索 ALTPLL,选中 ALTPLL 并双击

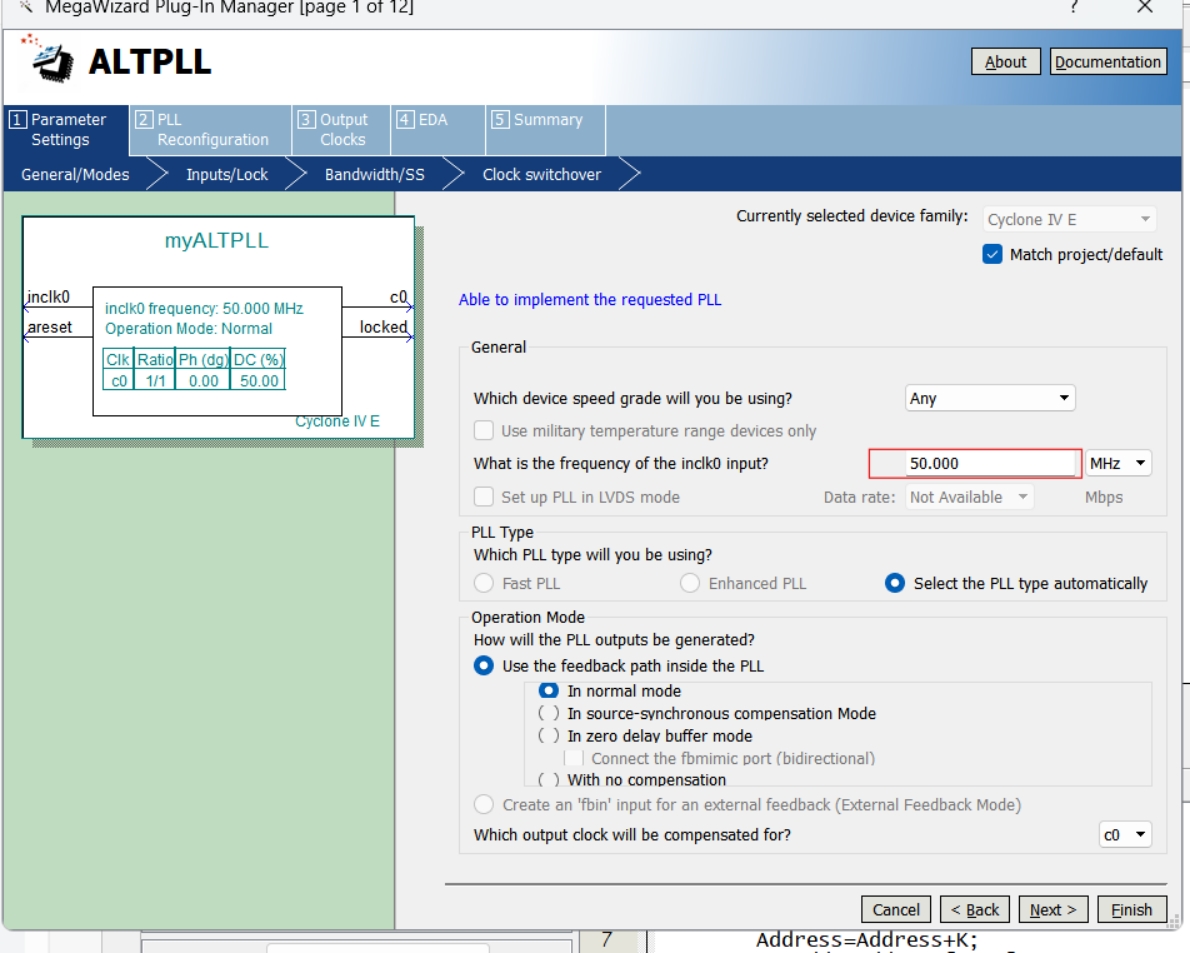

修改如图所示的参数

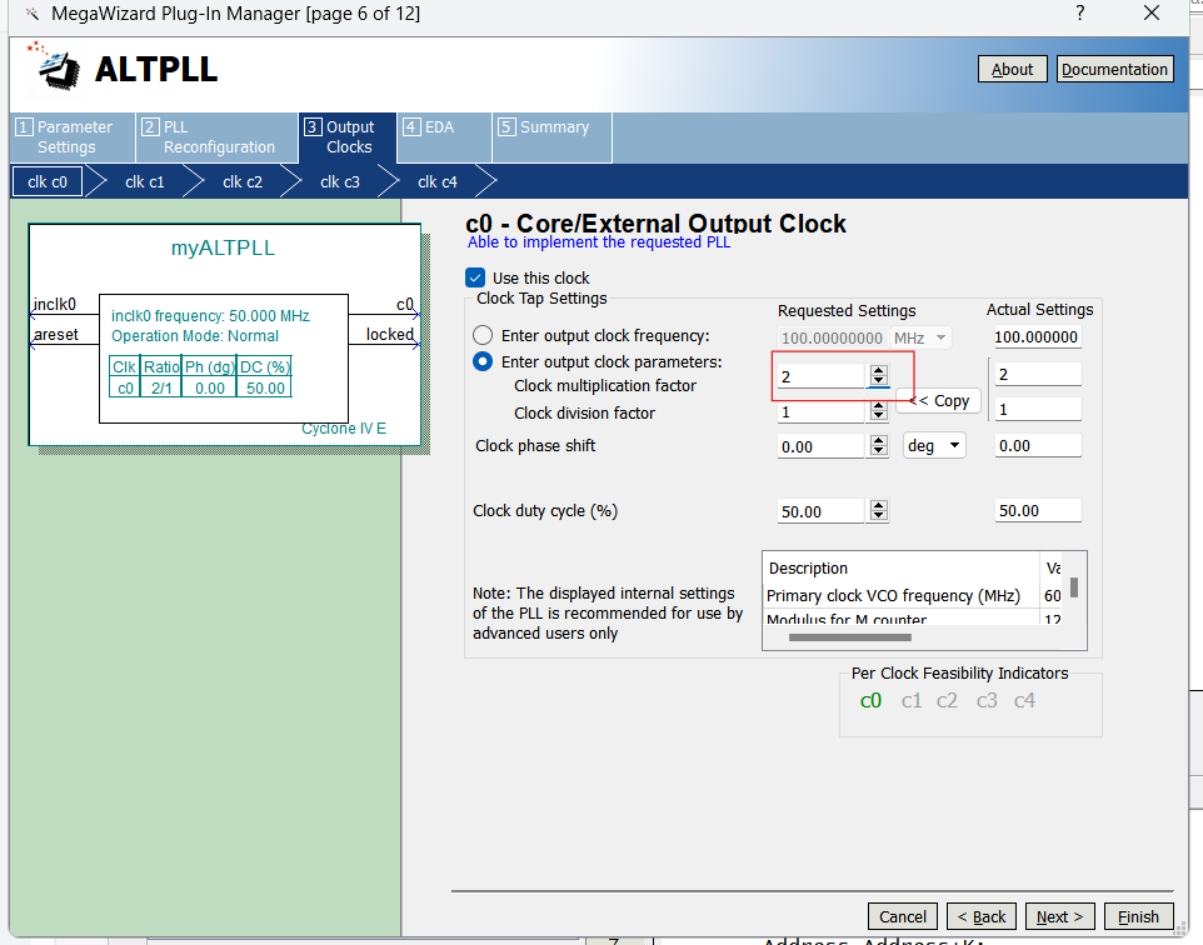

之后一直 Next 默认选项,直到出现以下界面,修改Clock multi...的参数

之后也是一直默认选项,直到 Finish

2.2.3 顶层电路设计

代码如下:

module DDS_top (CLOCK_50,RSTn,WaveSel,K,

WaveValue,LEDG,CLOCK_100);

input CLOCK_50;

input RSTn;

input [1:0] WaveSel;

input [12:0] K;

output reg [11:0] WaveValue;

wire [9:0] ROMaddr/* synthesis keep */;

wire [16:0] Address;

wire [11:0] Qsine,Qsquare;

output [0:0] LEDG;

output CLOCK_100;

wire CPi=CLOCK_100;

myALTPLL PLL100M_CP_inst(

.inclk0(CLOCK_50),

.c0(CLOCK_100),

.locked(LEDG[0])

);

addr_cnt U0_instance(CPi,K,ROMaddr,Address);

myROM ROM_inst(

.address(ROMaddr),

.clock(CPi),

.q(Qsine)

);

squwave U1(CPi,RSTn,Address,Qsquare);

always @(posedge CPi)

begin

case(WaveSel)

2'b01:WaveValue=Qsine;

2'b10:WaveValue=Qsquare;

default:WaveValue=Qsine;

endcase

end

endmodule跟之前一样,将该模块设置为顶层文件并进行编译

三、DE2-115设计实现

配置引脚

可以直接导入DE2_115_pin_assignments.csv文件进行配置,也可以手动进行配置

module DE2_115_DDS_top(CLOCK_50,KEY,SW,GPIO_0,LEDG);

input CLOCK_50;

input [3:3] KEY;

input [17:0] SW;

output [12:0] GPIO_0;

output [0:0] LEDG;

wire CLOCK_100;

assign GPIO_0[12]=CLOCK_100;

wire RSTn=KEY[3];

wire [1:0] WaveSel=SW[17:16];

wire [12:0] K=SW[12:0];

wire [11:0] WaveValue;

assign GPIO_0[11:0]=WaveValue;

DDS_top DE2(CLOCK_50,RSTn,WaveSel,K,WaveValue,LEDG,CLOCK_100);

endmodule引脚配置完成要再次编译运行

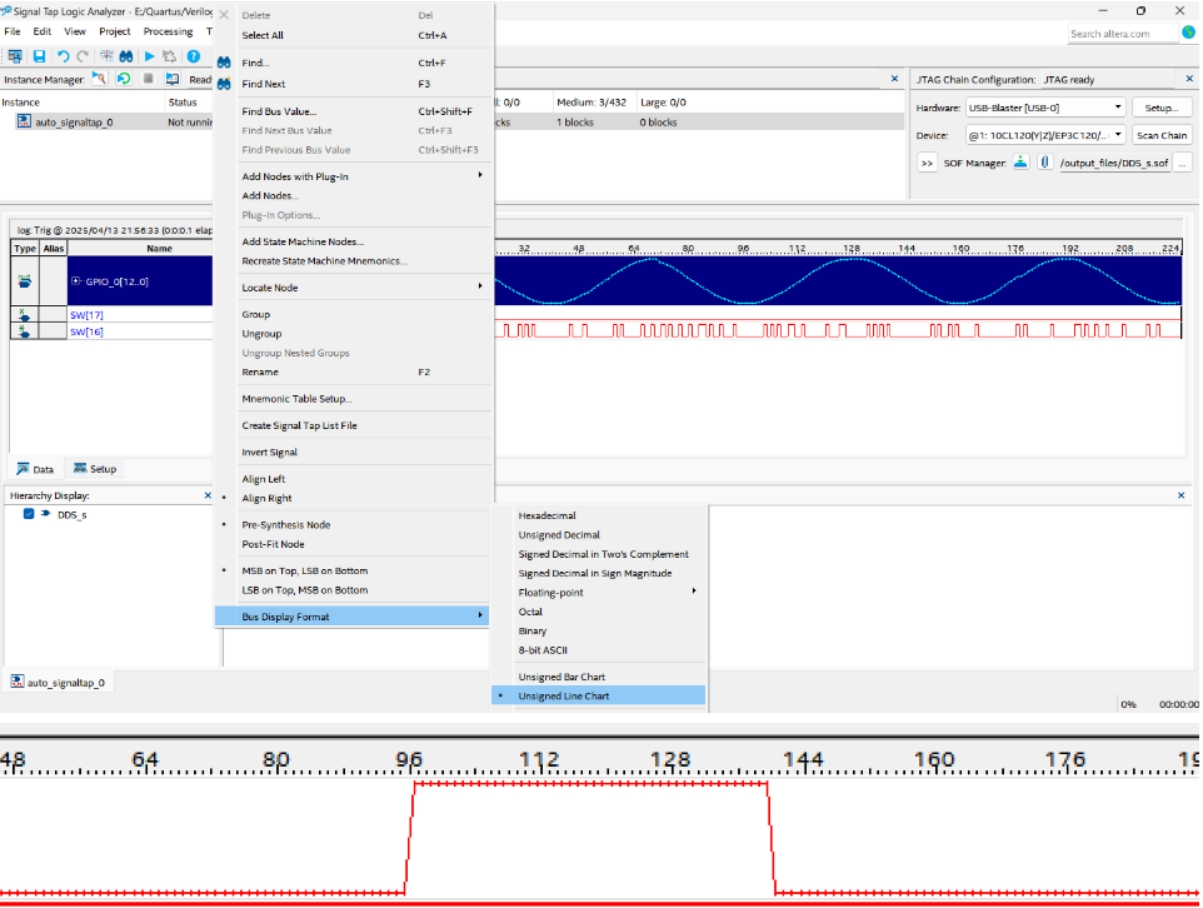

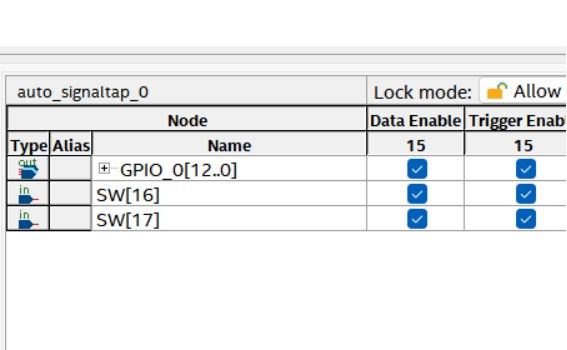

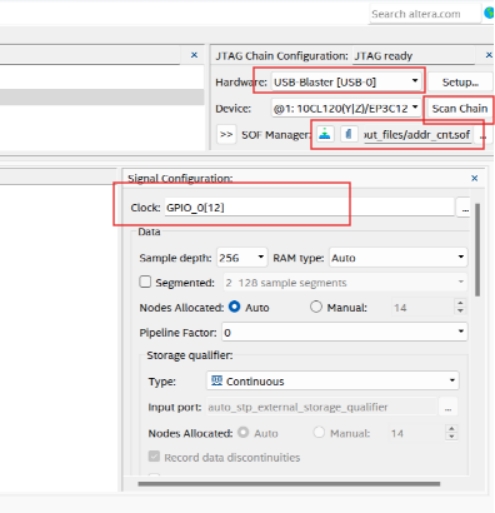

接下来就可以使用SignalTap ll实时测试输出波形的离散数据,选择Tools-->SignalTap ll Logic Analyzer

右键 Setup 上方空白处,点击 Add Node... 进行添加

全部确认无误后,保存文件并编译(要连接开发板)

波形图如下: