已购买域名 如何做网站南宁seo团队哪家好

FPGA 的开发流程可知,在 FPGA 开发的过程中会产生很多不同功能的文件,为了方便随时查找到对应文件,所以在开始开发设计之前,我们第一个需要考虑的问题是工程内部各种文件的管理。如 果不进行文件分类,而是将所有文件存放在一起,非常不易于后期文件的查找、管理和移植。下面我们就开始讲解我们所有工程文件的统一管理模式。、

| 文件夹名 | 功能说明 |

|---|---|

doc | 存放项目开发过程中的辅助文档,如波形图、流程图、设计说明等 |

prj | 存放项目工程文件,如 Quartus/Vivado 工程文件、约束文件(XDC/SDC)、顶层配置等 |

rtl | 存放 RTL(Register Transfer Level)级代码,如 Verilog/VHDL 源码模块 |

sim | 存放仿真文件,包括测试平台 testbench、仿真脚本等 |

接下来我们只讲一篇简单的流程应用作为举例。

“点亮 LED”实验是使用的XC7A100TFGG484-2I、XC7A35TFGG484-2I、XC7A200TFBG484-2I的KEY0 按键来控制 LED0 灯亮灭。按键没有被按下时,LED0 灯保持常灭;当按键 KEY0 被按下时, LED0 灯被点亮;当按键 KEY0 被松开时, LED0 灯被被熄灭。

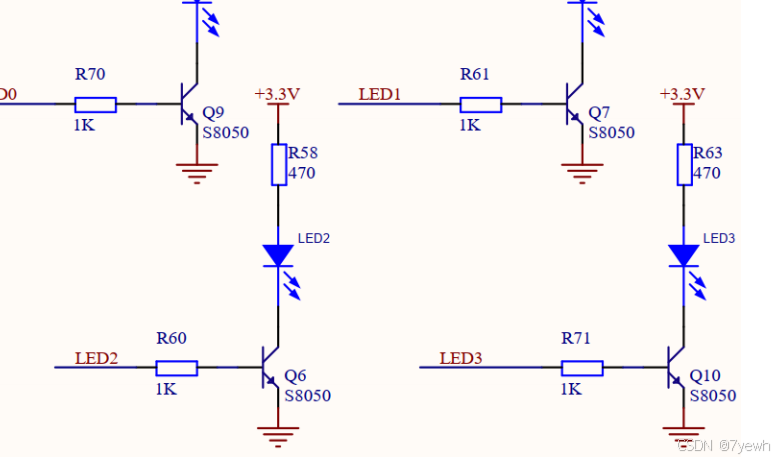

发光二极管的原理图,LED0 到 LED3 这 4 个发光二极管的阴极分别连到 S8050 ( NPN三极管)的集电极上,阳极都与 3.3V 电压相连,三极管的基极分别与 FPGA 相连,这是由于 FPGA 的 IO口的电压只有 1.3 5V ,电压较低,所以此处连接三极管是为了起到放大电压的作用。这样就可以通过改变三极管的状态来控制 LED 的亮灭。当 FPGA 输出到为高电平时,三极管导通, LED 灯亮;当 FPGA 输出到为低电平时,三极管截止,LED 灯灭。原理图中 LED 与三极管之间的电阻起到限流作用。

更多的硬件内容在我的硬件篇当中,不懂的话可以去看看。

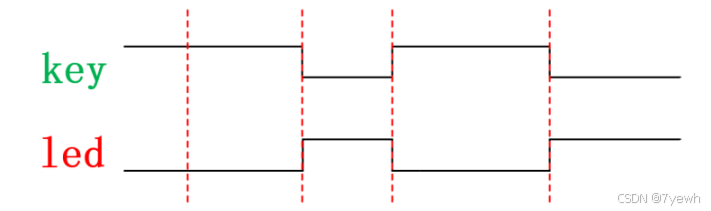

因此我们可以产生这样的一个波形就能解决问题,FPGA更像是一切问题回归到波形。

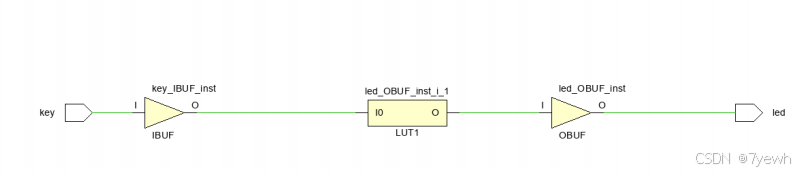

因此我们的程序写的也非常的简单。

module led( input key, output led

);assign led = ~key; endmodule之后我们就进行仿真就行,也是非常的简单,就是要针对上述的代码写个应用实例,非常像LINUX中的内核跟用户,如果你之前只会LINUX系列的主控的话,就这样去理解就好了。如下所示代码。

`timescale 1ns / 1ns //仿真单位/仿真精度module tb_led(); reg key;wire led;initial beginkey <= 1'b1; //按键上电默认高电平#200 //延迟 200nskey <= 1'b1; //按键没有被按下#1000 key <= 1'b0; //按键被按下#600 key <= 1'b1; #1000 key <= 1'b0;

endled u_led(.key (key),.led (led)

);

endmodule接着我们通过Modelsim 软件来进行仿真。

最后回到我们的软件芯片平台,还是上述那个代码。

module led(

input key,

output led

);

assign led = ~key;

endmodule

将文件工程加入进去即可。

因此,你要针对代码区增加你的硬件描述。

注意, Vivado 的约束文件是以“ .xdc ”为后缀的文本文件,其中存储的是一条条的 xdc 约束命令。

我们双击打开 led.xdc 文件,开始对工程进行约束。约束一般分为两种,一种是 IO 管脚的约束,另外

一种是对时序进行约束。我们先来看下 IO 管脚的约束,约束语句如下:

#IO 管脚约束

set_Property -dict {PACKAGE_PIN T4 IOSTANDARD LVCMOS15} [get_ports key]

set_Property -dict {PACKAGE_PIN V9 IOSTANDARD LVCMOS15} [get_ports led]

之后就是程序固化了。

当我们调试好一个工程后我们不能每次上电都要去下载一次代码,那样显得操作太麻烦。为了能够让工程上电就能运行,所以我们还需要最后一个步骤就是生成固化文件,然后将文件固化到板载 flash 中去,这样上电后程序就能启动。这里我们向读者提供三种方法固化工程,在生成固化文件之前我们先打开我们的工程时序约束文件,在时序约束文件里添加这样一段原语:

程序固化 = 把 bitstream 文件烧进外部 Flash,让 FPGA 上电即加载,永久保存配置。

FPGA 芯片本身是SRAM 架构,上电后内容全丢,每次必须加载配置文件(bitstream)才能工作。

在开发阶段,我们使用 JTAG 下载临时运行(掉电就没了);

在产品部署阶段,就需要将 bitstream 固化进外部 Flash,上电自动加载。

FPGA → 配置时钟 CCLK

FPGA → 配置数据 DIN/D0

FPGA ← 状态监测 DONE/INIT_B

因此我们添加如下代码

set_Property CFGBVS VCCO [current_design]

配置引脚电压参考源为 VCCO

set_Property CONFIG_VOLTAGE 3.3 [current_design]

设置 FPGA 配置电压为 3.3V

set_Property BITSTREAM.GENERAL.COMPRESS true [current_design]

启用 bitstream 压缩

set_Property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]

设置 FPGA 从 Flash 加载配置数据的速率为 50 Mbps

set_Property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

配置使用 Quad SPI 模式(4线 SPI)加载 bitstream

set_Property BITSTREAM.CONFIG.SPI_FALL_EDGE Yes [current_design]

在 SPI 的下降沿采样数据