杭州专业网站制作设计网店推广运营

FPGA——基于DE2_115实现DDS信号发生器

文章目录

- FPGA——基于DE2_115实现DDS信号发生器

- 一、实验要求

- 二、实现过程

- (1)新建工程

- 二、波形存储器ROM

- (1)方波模块

- (2)正弦波形存储器

- (3)锁相环倍频电路

- (4)顶层模块

- 三、DE2_115验证

- (1)顶层模块

- (2)设置引脚

- (3)烧录

- (4)波形仿真

- (5)实现效果

- 四、参考文献

- 五、总结

一、实验要求

采用直接数字频率合成(Direct Digital FrequencySynthesis,简称DDS)设计制作一个波形发生器,仿真后,在DE2-115开发板上实践。

要求:(1)利用DDS技术合成正弦波和方波;

(2)输出信号的频率范围为10Hz~5MHz,最小频率分辨率小于1kHz;

( 3)使用嵌入式逻辑分析仪SignalTap II实时测试输出波形的离散数据。

二、实现过程

(1)新建工程

完成工程创建后添加模块代码实现各模块

(2)相位累加器

新建代码后跳转到VScode时会默认起一个名字最好另存为对应文件名否则在后面运行会报错。

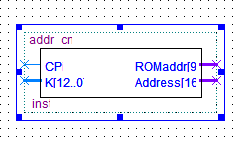

新建保存完代码后将代码文件添加到工程中并将addr_cnt.v设置为顶层模块

选中顶层文件右键选择Set as Top…编译运行成功后再次右键选择Create Symbol Files for Current File再打开.bsf文件,就可以看到生成该模块的符号。

相关代码:

addr_cnt.v

module addr_cnt(CPi,K,ROMaddr,Address);input CPi;input [12:0] K;output reg [9:0] ROMaddr;output reg [16:0] Address;always @(posedge CPi) beginAddress=Address+K;ROMaddr=Address[16:7];end

endmodule符号:

二、波形存储器ROM

(1)方波模块

首先实现 方波模块这一部分的操作和前面的相位累加器的过程是一样的步骤添加代码然后设置为顶层模块然后生成模块符号查看。

新建代码后跳转到VScode时会默认起一个名字最好另存为对应文件名否则在后面运行会报错。

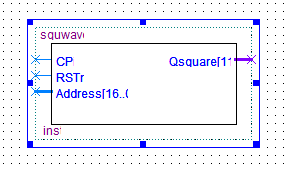

新建保存完代码后将代码文件添加到工程中并将squwave.v设置为顶层模块

选中squwave.v文件右键选择Set as Top…编译运行成功后再次右键选择Create Symbol Files for Current File再打开.bsf文件,就可以看到生成该模块的符号。

相关代码:

squwave.v

module squwave(CPi,RSTn,Address,Qsquare);input CPi;input RSTn;input [16:0] Address;output reg [11:0] Qsquare;always @(posedge CPi)if (!RSTn)Qsquare=12'h000; else beginif(Address<=17'h0FFFF)Qsquare=12'hFFF;else Qsquare=12'h000;end

endmodule符号:

接着是正弦波形存储器

(2)正弦波形存储器

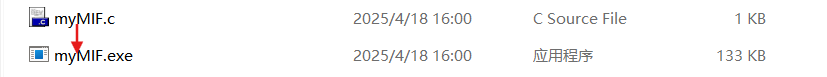

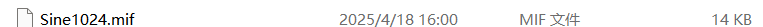

这里编写C语言程序,生成存储器的初始化文件Sine1024.mif。

相关代码如下:

myMIF.c

/*myMIF.c*/

#include <stdio.h>

#include <math.h>

#define PI 3.141592

#define DEPTH 1024

#define WIDTH 12

int main(void)

{int n,temp;float v;FILE *fp;fp=fopen("Sine1024.mif","w+");if(NULL==fp)printf("Can not creat file!\r\n");else{printf("File created successfully!\n");fprintf(fp,"DEPTH=%d;\n",DEPTH);fprintf(fp,"WIDTH=%d;\n",WIDTH);fprintf(fp,"ADDRESS_RADIX=HEX;\n");fprintf(fp,"DATA_RADIX=HEX;\n");fprintf(fp,"CONTENT\n");fprintf(fp,"BEGIN\n");for(n=0;n<DEPTH;n++){v=sin(2*PI*n/DEPTH);temp=(int)((v+1)*4095/2);fprintf(fp,"%04x : %03x;\n",n,temp);}fprintf(fp,"END;\n");fclose(fp);}} 编译运行后生成.exe再运行.exe会生成Sine1024.mif

接下来调用LPM_ROM定制正弦波形存储器:点击Tools然后选择IP Catalog

过程如下:

(没有截图的部分直接点击next即可)

完成ROM配置之后接下来实现锁相环倍频电路

(3)锁相环倍频电路

过程如下:

(没有截图的部分直接点击next即可)

完成之后接下来是顶层模块

(4)顶层模块

相关代码:

DDS_top.v

module DDS_top (CLOCK_50,RSTn,WaveSel,K,

WaveValue,LEDG,CLOCK_100);input CLOCK_50;input RSTn;input [1:0] WaveSel;input [12:0] K;output reg [11:0] WaveValue;wire [9:0] ROMaddr/* synthesis keep */;wire [16:0] Address;wire [11:0] Qsine,Qsquare;output [0:0] LEDG;output CLOCK_100;wire CPi=CLOCK_100;PLL100M_CP PLL100M_CP_inst(.inclk0(CLOCK_50),.c0(CLOCK_100),.locked(LEDG[0]));addr_cnt U0_instance(CPi,K,ROMaddr,Address);SineROM ROM_inst(.address(ROMaddr),.clock(CPi),.q(Qsine));squwave U1(CPi,RSTn,Address,Qsquare);always @(posedge CPi)begincase(WaveSel)2'b01:WaveValue=Qsine;2'b10:WaveValue=Qsquare;default:WaveValue=Qsine;endcaseend

endmodule

新建代码后跳转到VScode时会默认起一个名字最好另存为对应文件名否则在后面运行会报错。

新建保存完代码后将代码文件添加到工程中并将DDS_top .v设置为顶层模块

选中DDS_top 文件右键选择Set as Top…编译运行。

三、DE2_115验证

完成上面的全部过程后接下来进行上板验证:

(1)顶层模块

相关代码:

DE2_115_DDS_top.v

module DE2_115_DDS_top(CLOCK_50,KEY,SW,GPIO_0,LEDG);input CLOCK_50;input [3:3] KEY;input [17:0] SW;output [12:0] GPIO_0;output [0:0] LEDG;wire CLOCK_100;assign GPIO_0[12]=CLOCK_100;wire RSTn=KEY[3];wire [1:0] WaveSel=SW[17:16];wire [12:0] K=SW[12:0];wire [11:0] WaveValue;assign GPIO_0[11:0]=WaveValue;DDS_top DE2(CLOCK_50,RSTn,WaveSel,K,WaveValue,LEDG,CLOCK_100);

endmodule重新添加这个为新的顶层模块

新建代码后跳转到VScode时会默认起一个名字最好另存为对应文件名否则在后面运行会报错。

新建保存完代码后将代码文件添加到工程中并将DDS_top .v设置为顶层模块

选中DDS_top 文件右键选择Set as Top…编译运行。

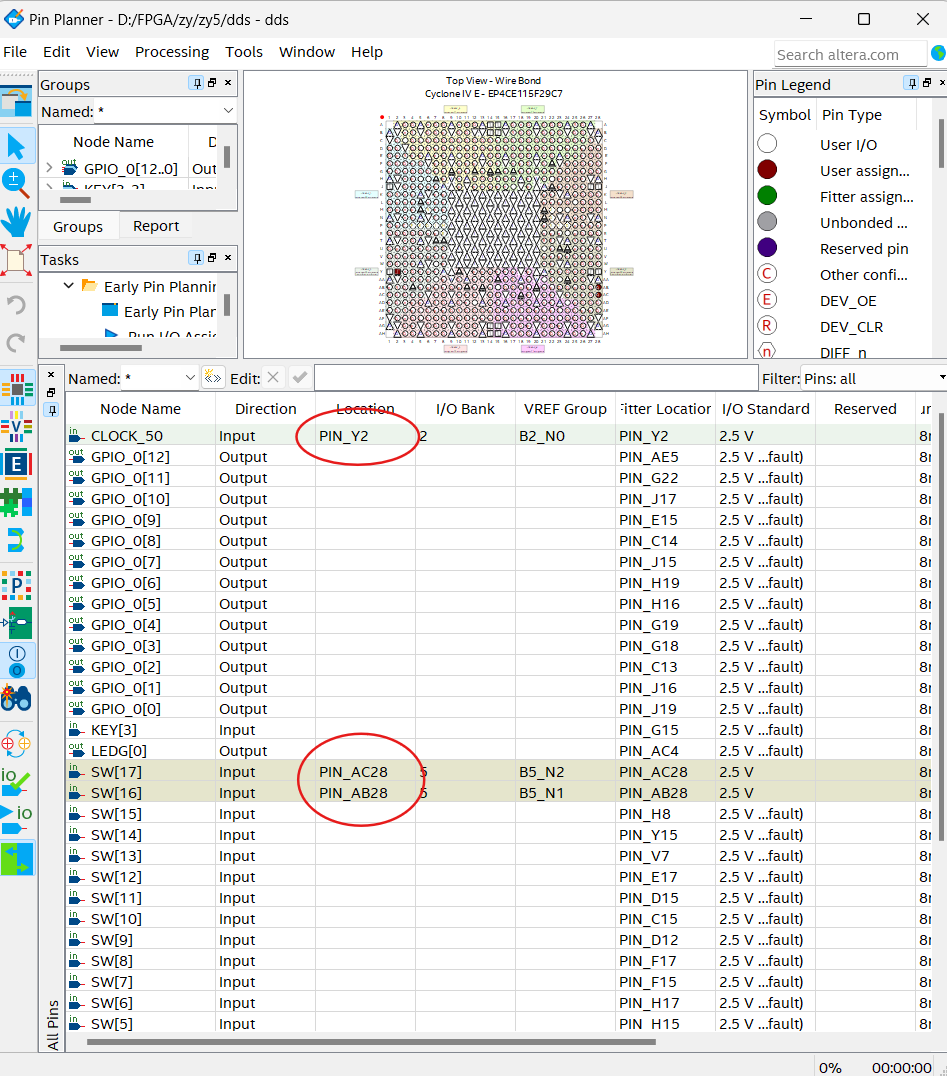

(2)设置引脚

这里图片里面选择引脚的时候没注意选择的是sw1、sw0的。

可以根据DE2 _115说明书查看对应要使用的引脚。

(3)烧录

(4)波形仿真

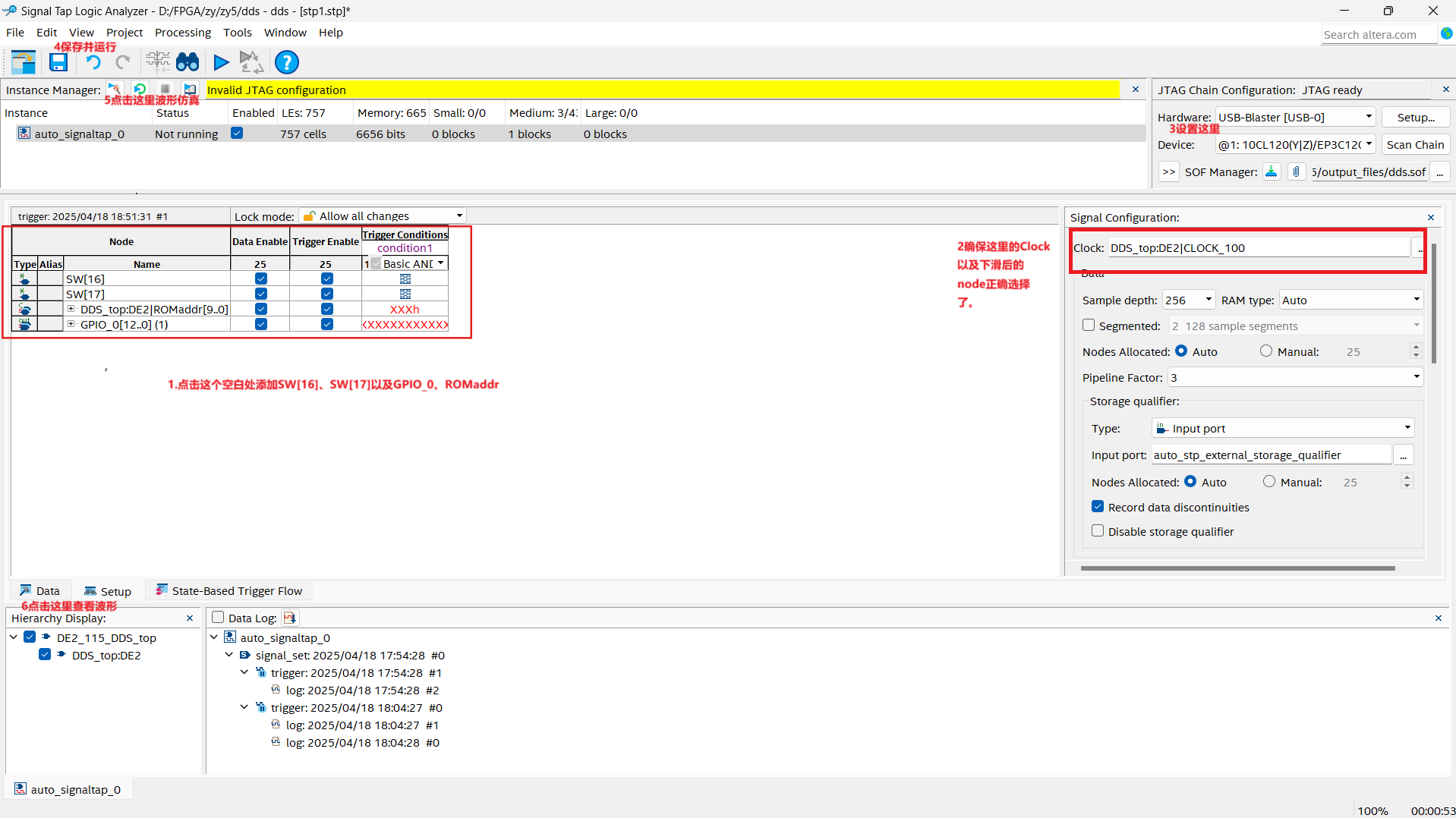

按照图片里面的文字说明设置就可以了

(5)实现效果

拨动自己设置的对应引脚的开关就可以发现波形图有变化:

四、参考文献

【DE2-115】Verilog实现DDS+Quartus仿真波形

DDS信号发生器设计(Quartus)

Verilog_HDL与FPGA数字系统设计【第2版】第8.7节

五、总结

本次实验的完成加强了对Quartus软件的操作熟练度同时学习到了关于波形存储器ROM的方波模块、正弦波形存储器、锁相环倍频电路的相关知识此外也让我知道了如何实现一个DDS信号发生器。