硬件学习笔记--53 DC-DC Buck工作原理、选型及应用介绍

DCDC Buck转换器作为现代电子系统中不可或缺的电源管理器件,其选型和应用对系统性能有着决定性影响。本文将从Buck转换器基本原理出发,详细解析选型关键参数、外围器件设计、PCB布局要点等方面,帮助工程师全面掌握Buck转换器的设计技巧。

1.Buck转换器基本原理

Buck转换器(降压型DC-DC转换器)是一种输出电压低于输入电压的非隔离直流变换器,广泛应用于各种电子设备的电源系统中。与线性稳压器(LDO)相比,Buck转换器具有显著的高效率优势,通常效率在70%以上,高效率设计甚至可达95%以上。

基本工作原理:Buck变换器的主电路由开关管、二极管(或同步MOS管)、输出滤波电感和输出滤波电容构成。当开关管闭合时,电感被充磁储能,电流线性增加,同时给电容充电并为负载提供能量;当开关管关断时,储能电感通过续流二极管(或同步MOS管)放电,电流线性减小,输出电压靠输出电容放电和减小的电感电流维持6。通过控制开关管开启关断的占空比,可以精确控制输出电压的大小。

Buck转换器的工作模式根据电感电流是否连续可分为四种:连续导通模式(CCM)、边界导通模式(BCM)、非连续导通模式(DCM)和强制连续导通模式(FCCM)。不同模式下电感的电流波形特性不同,对转换器的效率和纹波性能有显著影响。

2.Buck转换器关键选型参数

2.1 电气特性参数

1)输入电压范围:必须考虑实际使用中的输入电压波动范围,确保不超过器件规格。例如工业应用常需要宽输入范围(如4.5V-60V)的Buck转换器。

2)输出电压:有固定输出和可调输出两种类型。可调输出通过外部电阻分压网络设置,提供设计灵活性。

3)输出电流能力:需评估后级电路的瞬间峰值电流和发热情况,一般按80%降额原则选择(如实际需要2A则选2.5A及以上)。

4)开关频率:影响外部电感和电容的选型。高频(1-2MHz)可减小电感体积但增加开关损耗;低频(几百kHz)有利于效率但需要更大电感。

2.2 性能指标参数

1)效率:需关注轻载和重载两种情况,高效率设计可达95%以上。同步Buck通常比异步Buck效率高5-15%。

2)纹波噪声:一般要求控制在200mV至50mV以下,高速高精度系统可能要求<10mV。轻载和重载下的纹波都需要关注。

3)负载调整率:衡量负载变化时输出电压的稳定性,优质Buck转换器通常为3%-5%。

4)线性调整率:反映输入电压变化时输出电压的稳定性,一般要求<1%。

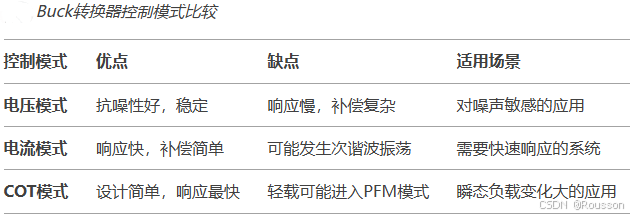

2.3 控制模式选择

Buck转换器的控制模式直接影响环路设计和动态响应:

1)电压模式(VM):设计复杂,响应慢,但抗噪性好。

2)峰值电流模式(PCM):消除了输入电压响应延迟,提供高增益和过流保护,补偿更简单。

3)固定导通时间模式(COT):无需环路补偿,瞬态响应快,全负载高效率,设计简单。

3.外围关键器件设计与选型

Buck转换器性能很大程度上取决于外围器件的正确选择和设计,主要包括电感、输入输出电容等。

3.1电感选型要点

电感是Buck转换器中最重要的外围器件之一,选型需考虑以下参数:

电感值计算:基本公式为Lₘᵢₙ=(Vᵢₙ-Vₒᵤₜ)×Vₒᵤₜ/(ΔI×f×Vᵢₙ),其中ΔI一般取输出电流的20%-40%。实际选择时可略大于计算值。

a)电流参数:

饱和电流(Isat):电感量下降20-30%对应的电流,峰值电流不应超过此值温升电流(Iᵣₘₛ):使电感温升不超过40°C的电流,有效值电流不应超过此值

b)DCR(直流电阻):影响效率,应尽可能小以减少导通损耗。

举例:对于输入24V、输出5V/3A、频率500kHz的设计,取ΔI为30%Iₒᵤₜ(0.9A),计算得Lₘᵢₙ≈7.64μH,选择10μH电感。峰值电流Iₚₑₐₖ=3A+0.45A=3.45A,故选择饱和电流≥5A的电感。

3.2 电容选型要点

1)输入电容:减少输入电压纹波,提供瞬态电流。计算公式为Cᵢₙ=(Iₒᵤₜ×D×(1-D))/(f×ΔVᵢₙ)5。建议使用低ESR陶瓷电容,如X7R/X5R类型。

2)输出电容:影响输出电压纹波和瞬态响应。计算公式考虑纹波和瞬态响应两方面5。同样推荐低ESR陶瓷电容。

3)BST电容:用于高边驱动,一般0.1-1μF低ESR陶瓷电容,耐压高于输入电压。

设计实例:上述24V转5V/3A设计中,输入电容计算约需2.7μF,实际选用4-5个2.2μF并联;输出电容计算约需47μF,实际选用2个22μF并联。

3.3 二极管选型(异步Buck)

异步Buck需要续流二极管,选型要点:

1)反向电压≥最大输入电压

2)峰值电流>最大电感电流

3)正向压降小以减少损耗

4)肖特基二极管是优选

4.3.外围关键器件设计与选型

4. PCB布局设计要点

良好的PCB布局对Buck转换器性能至关重要,主要考虑以下方面:

1)功率回路最小化:输入电容、开关节点、电感和输出电容形成的功率回路面积应尽可能小,以降低寄生电感和EMI。

2)关键元件布局:输入电容尽量靠近芯片Vin引脚;电感靠近SW引脚但远离反馈走线;反馈电阻靠近FB引脚,走线远离噪声源。

3)接地设计:采用星型接地或单点接地;功率地和信号地分开;电容地端增加适当过孔。

4)热管理:大电流路径使用足够宽的铜箔;高热元件下方可增加散热过孔;必要时使用散热片。