高速电路中的时序设计

1 时序设计概述

在高速电路设计中,由于趋肤效应、临近干扰、电流高速变化等因素,设计者不能单纯地从数字电路的角度来审查自己的产品,而要把信号看做不稳定的模拟信号。采用频谱分析仪对高速信号进行分析,可以发现,信号的高频噪声主要来自于信号的变化沿而不是信号的周期频率。例如,一个1MHz的信号,虽然时钟周期为1μs,但如果其变化沿时间为纳秒级,则在频谱仪上可以观察到数百兆赫兹的谱线。因此,高速电路设计者更加关注的是信号的边沿,因为信号边沿往往也是信号频谱最高,最容易受到干扰的地方。

在高速电路中,数据的采样基于某特定时钟,即数据信号及其对应的时钟信号应保持某种同步关系,这样的设计称为同步设计。在同步设计中,由于数据的读取都是基于时钟,根据以上分析,为了得到稳定的数据,时钟的采样点应远离数据的变化沿。

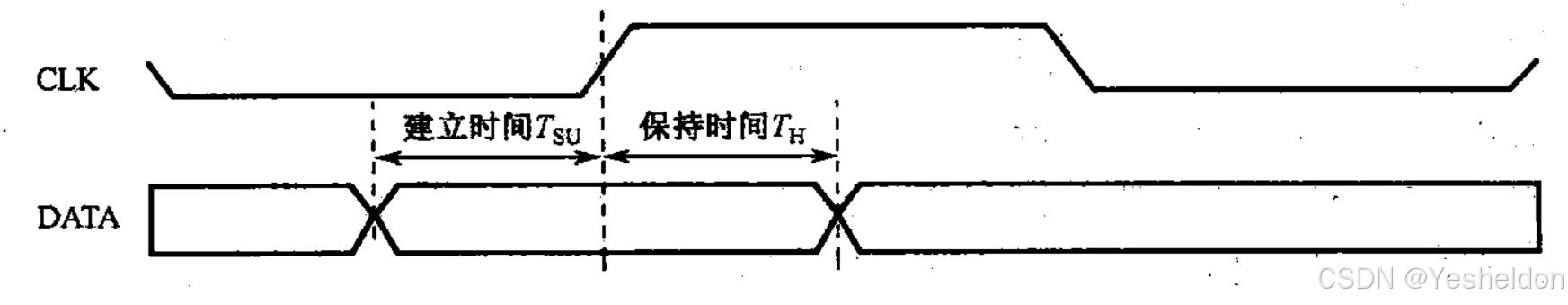

下图所示是利用时钟CLK上升沿采样数据DATA的示意图。DATA发生变化后,需要等待至少Tsu时间(建立时间)才能被采样,而采样之后,至少在Th时间(保持时间)内,DATA不能发生变化。可以看出,器件的建立时间和保持时间的要求,正是为了保证时钟的采样点远离数据的变化沿。如果这些要求在接收端得不到满足,则接收端采样到的DATA信号的状态将得不到保证。

因此,时序设计的目标就是实现对接收端输入数据的可靠采样。

2 时序参数介绍

为了进行时序分析,需要从器件资料中获取以下关键参数。

- F:时钟频率。该参数取决于器件工作速率的要求。

- Tcycle:时钟周期,等于时钟频率F的倒数,Tcycle=1/F。

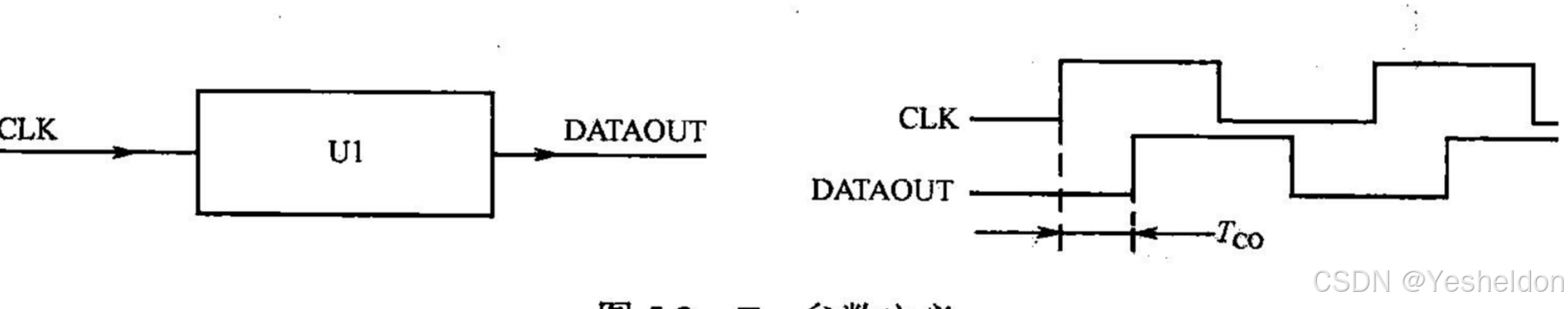

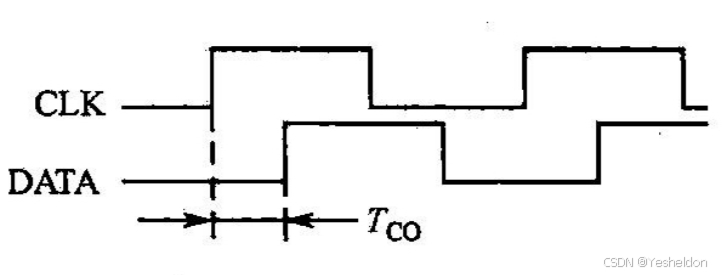

- Tco:输出数据相对时钟的延时。该参数可从发送端器件的资料中获得。前文提到,接收端的输入数据需要利用时钟进行采样,而发送端的输出数据,同样也要参考时钟。受器件制造工艺的限制,在发出时钟后,数据出现在器件引脚上需要一定的延时,这段延时就称为Tco。该参数取决于器件的制造工艺。Tco参数的定义如下图所示。

- Tsu(min):接收端对输入信号建立时间的要求。该参数可从接收端器件的资料中获得。

- Th(min):接收端对输入信号保持时间的要求。该参数可从接收端器件的资料中获得。

除以上五个参数外,时序设计中,还涉及以下的中间数据。

- L:信号走线长度。

- Ttqint:信号在PCB上的传输延时。单位长度的走线,在PCB上的传输延时取决于该走线位于内层还是外层,外层走线(表层和底层)的单位延时较小,约为140ps/in(皮秒每英寸),内层走线(中间层)的单位延时较大,约为180ps/in。根据信号走线长度L以及单位延时,可计算出Ttqint。

- Tsu(margin):输入信号建立时间裕量。该参数与输入信号建立时间Tsu及最小建立时间要求Tsu(min)之间的关系为,Tsu(margin)=Tsu-Tsu(min),为实现接收端对输入信号的可靠采样,要求Tsu(margin)>0。

- Th(margin):输入信号保持时间裕量。该参数与输入信号保持时间Th及最小保持时间要求Th(min)之间的关系为,Th(margin)=Th-Tu(min),为实现接收端对输入信号的可靠采样,要求Th(margin)>0。

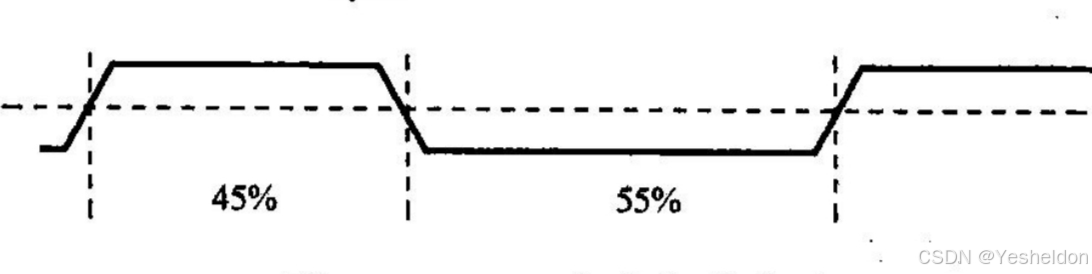

以上参数均是时序设计的关键参数,对于普通的时序分析已经足够。但是对于一些特殊的应用,例如,DDR SDRAM,其采用双边沿数据采样,因此采样频率比单边沿采样高一倍,需注意的是,此时的采样周期不能简单地采用时钟周期的一半,即Tcycle/2来计算,而是要从器件资料中提取时钟占空比参数(Duty Cycle)。占空比指信号处于高电平和低电平的时间的比值。例如,如下图所示,器件资料上定义某信号的占空比为45/55,频率为100MHz,则在一个周期中,该信号处于高电平和低电平的时间分别为4.5ns和5.5ns,采样周期应取这两个时间的最小值,即Tcycle×0.45=4.5ns。

在第一节提到,时序设计的目标就是实现对接收端输入数据的可靠采样。而可靠采样就是要满足以下两个不等式:

Tsu(margin) > 0 (5.1)

Th(margin) > 0 (5.2)

本章的后续内容将围绕如何满足以上两个不等式而展开。

理解要点:

时序分析的关键参数有F、Tcycle、Tco、Tsu(min)、Th(min)。前两个参数的取值依赖于设计的要求,后三个参数可从器件资料上获得,与具体设计无关。

3 源同步系统时序设计

3.1 源同步系统时序设计原理

1. 源同步系统时序设计分析

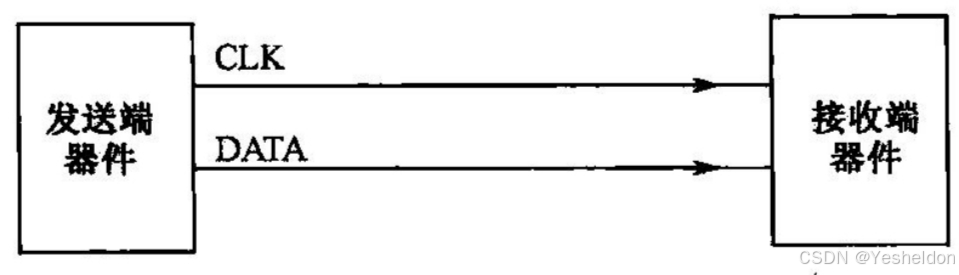

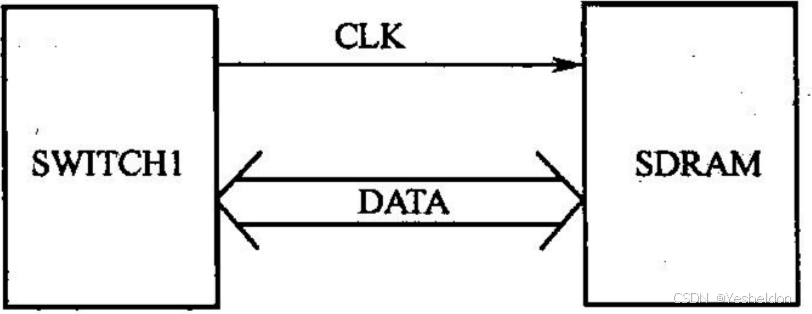

源同步指数据和时钟由同一个器件驱动发出的情况,如下图所示为常见的源同步系统拓扑结构。

该同步系统的特点是,时钟和数据均由发送端器件发出,在接收端,利用接收到的时钟信号CLK采样输入数据信号DATA。以下将按步骤分析如何满足该同步系统的时序要求。

1)发送端的时序

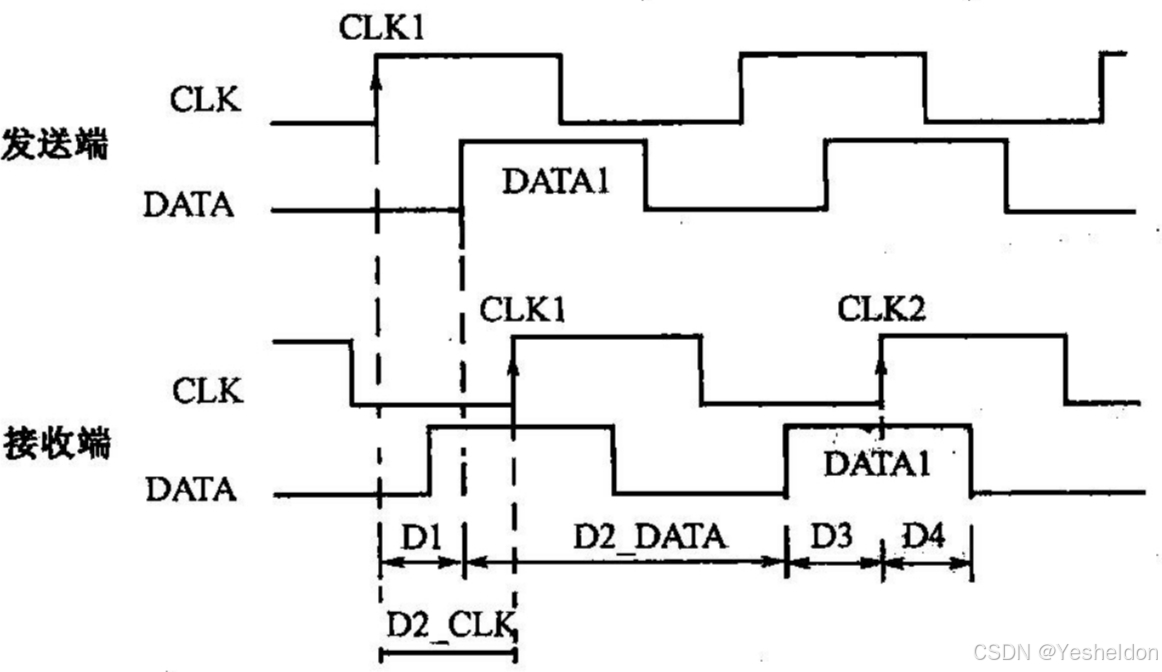

在发送端,DATA基于CLK的上升沿发出(对于双边沿采样的情况,则是基于CLK的上升沿和下降沿),DATA的边沿相对CLK上升沿的延时为Tco。因此在发送端器件的引脚上,可测得CLK和DATA的时序图如下图所示。

器件资料往往同时提供Tco参数的最小值Tco(min)和最大值Tco(max),后面会提到,在建立时间和保持时间的计算中,分别需要用到这两个参数。

2)传输路径上的延时

在从发送端到接收端传输路径的走线上,需要经历传输延时,CLK和DATA各自对应的传输延时为Tflight-clk和Tflight-data。

3)接收端的时序分析

在第二节已经讨论过,在接收端,输入信号的建立时间和保持时间需得到满足。

假定在发送端的某个时刻,数据线上发出的信号是DATA1,驱动该数据输出的时钟沿为CLK1,由于Tco延时的存在,若CLK和DATA信号的走线等长,即Tglight-clk=Tflight-data,

则在接收端,CLK1并不能作为DATA1的采样参考沿。为了实现接收端时钟对数据的可靠采样,应调整CLK和DATA的走线长度,有两种方法可利用:其一是使Tflight-data>Tflight-clk,即DATA信号相对CLK信号延时,对DATA1而言,在接收端,其采样参考沿为CLK2(CLK2比CLK1延时一个周期),其二是使Tflight-data<Tflight-clk,即CLK信号相对DATA信号进行延时,对DATA1而言,在接收端,其采样参考沿仍然为CLK1。如下图所示为第一种方法的图示。

时序参数D1、D2、D3、D4的含义如下。

D1:Tco,发送端器件输出数据相对时钟的延时。

D2_DATA1:DATA信号的走线延时。

D2_CLK:CLK信号的走线延时。

D3:Tsu,在接收端,DATA信号的建立时间。

D4:Th,在接收端,DATA信号的保持时间。

由于DATA信号的走线长度大于CLK信号,即Tflight-data>Tflight-clk,则有:

D2_DATA1-D2_CLK = Tflight-data-Tflight-clk

由上图可得

D1 + D2_DATA + D3- D2_CLK=Tcycle (5.3)

式(5.3)是源同步系统时序计算的基础公式。

2. 抖动和串扰对时序分析的影响

时序计算中还需考虑时钟抖动和数据间串扰对时序分析的影响。

1)时钟抖动对时序分析的影响

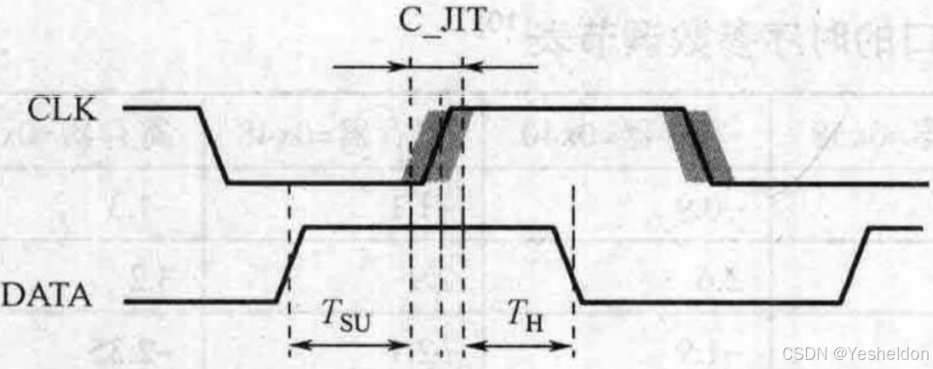

第6章将对抖动进行详细的介绍,在本小节,只需要对时钟抖动做一个初步的了解即可。抖动指信号的各个有效边沿相对于其理想位置的偏离。时钟抖动对时序计算的影响如下图所示。

上图中,由于时钟抖动C_JIT的存在,数据信号D1的建立时间Tsu和保持时间Th都受到了影响,因此,C_JIT参数应从时序裕量中减去。

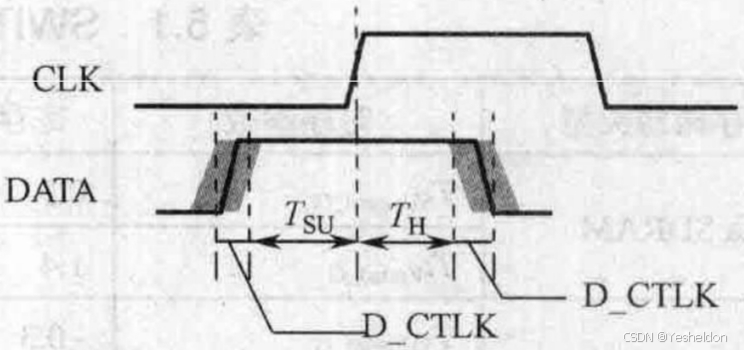

2)数据串扰对时序分析的影响

串扰将在以后章介绍,串扰是指走线相邻的数据信号之间的相互干扰。串扰可能导致数据信号的边沿发生抖动,从而对时序造成影响。

下图中,由于数据串扰的存在,数据信号的有效边沿相对其理想边沿发生了偏移。根据D_CTLK定义,该参数将影响数据信号DATA的建立时间Tsu和保持时间Th,因此,D_CTLK参数也应从时序裕量中减去。

综合上述,结合式(5.3),可以得出以下两式:

Tco(max)+(Tflight-data-Tflight-clk)+Tsu(min)+Tsu(margin)+C_JIT+D_CTLK = Tcycle (5.4)

Tco(min)+(Tflight-data-Tflight-clk)-Tth(min)-Tth(margin)-C_JIT-D_CTLK > Th(min) (5.5)

为满足式(5.1)和式(5.2),则有:

Tco(max)+(Tflight-data-Tflight-clk)+Tsu(min)+Tsu(margin)+C_JIT+D_CTLK < Tcycle (5.6)

Tco(min)+(Tflight-data-Tflight-clk)-Tth(min)-Tth(margin)-C_JIT-D_CTLK > Th(min) (5.7)

式(5.6)和式(5.7)即为源同步系统时序设计判据。

3.2 源同步系统时序设计范例一

1. 时序参数

本小节以某款以太网交换芯片SWITCH1为例,介绍其SDRAM接口的时序分析方法。SWITCH1是一款八口的百兆以太网交换芯片,支持各端口之间数据包的线速(无阻塞)交换。SWITCH1需外接两种存储器:控制存储器(Control SDRAM)和数据存储器(Data SDRAM),分别为控制流和数据流提供缓存,这两种外部缓存都采用SDRAM作为存储器。本设计的存储接口框图如下图所示。

后续章将对SDRAM进行详细的介绍,由于本小节只涉及时序的计算,因此不对SDRAM的应用做过多讨论。

SWITCH1的存储器接口支持多种速率,为获得最高的交换性能,本设计中,将接口速率设置为最高的167MHz,即有:

F = 167MHz

Tcycle = 6ns

SWITCH1的Tco参数值为:

Tco(max),0 = 4ns, Tco(min),0 = 1ns

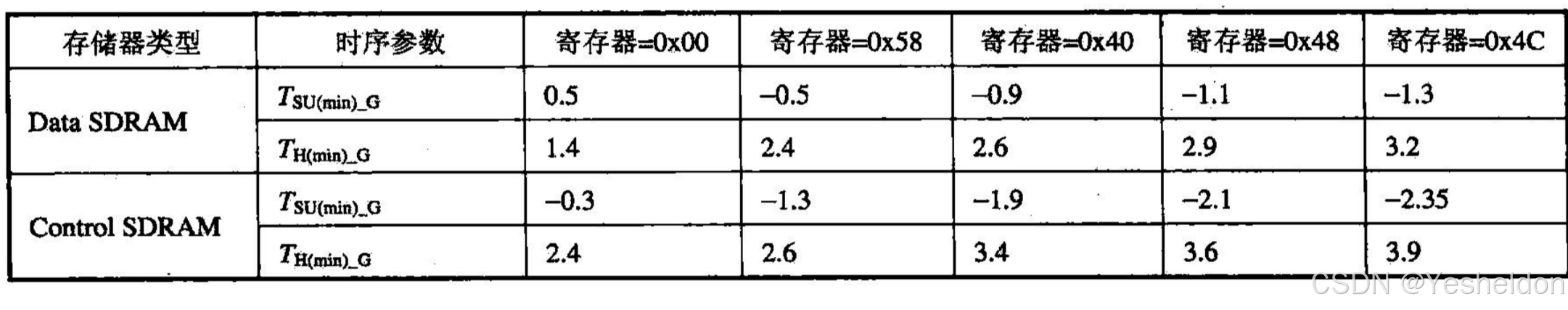

同时SWITCH1存储器接口可建立时间、保持时间的要求,可通过内部寄存器进行调节,如下所示为参数调节表,表中,各时序参数的单位是ns(纳秒)。

在本设计中,存储器选择为 Micron 公司的某 SDRAM,其时序参数如下:

Tco(max),S = 5.5ns

Tco(min),S = 2ns

Th(min),S = 1.5ns

为便于区分,SWITCH1 侧的时序参数以_G为后缀,SDRAM 侧的时序参数以_S为后缀。

2. 时序计算

简化起见,在下面的计算中暂不考虑 C_JIT 和 D_CTLK 两参数对时序裕量的影响。由于存储接口的数据总线为双向,根据式(5.6)和式(5.7),整理时序计算公式如下:在 SWITCH1 发往 SDRAM 的数据流方向上,SDRAM 作为接收端:

Tco(max)_G + (Tflight-data - Tflight-clk) + Tsu(min)_S < Tcycle (5.8)

Tco(min)_G + (Tflight-data - Tflight-clk) > Th(min)_S (5.9)

在 SDRAM 发往 SWITCH1 的数据流方向上,SWITCH1 作为接收端。与前一方向的数据流不同的是,在 SDRAM 一侧,需等待 SWITCH1 发送的时钟信号 CLK 到达,并满足 SDRAM 的 Tco 参数后,数据信号 DATA 才能发出,因此计算公式如下:

Tco(max)_S + (Tflight-data + Tflight-clk) + Tsu(min)_G < Tcycle (5.10)

Tco(min)_S + (Tflight-data - Tflight-clk) > Th(min)_G (5.11)

本例中,时序计算的目的有二,其一是对 CLK 和 DATA 信号走线长度的关系做出定义;其二是确定最佳的寄存器参数值。

根据式(5.8)~式(5.11),分别对不同寄存器参数值条件下的 DATA 和 CLK 走线长度进行计算。

(1)DATA SDRAM 的时序计算

(1)寄存器=0x00,各时序参数值如下:

Tco(max)_G= 4ns, Tco(min)_G= 1ns,

Tsu(min)_G= 0.5ns, Th(min)_G= 1.4ns,

Tco(max)_S = 5.5ns, Tco(min)_S = 2ns,

Tsu(min)_S = 1.5ns, Th(min)_S = 1ns

代入式(5.8)~式(5.11),有:

4 + (Tflight-data - Tflight-clk) + 1.5 < 6 (5.12)

1 + (Tflight-data - Tflight-clk) > 1 (5.13)

5.5 + (Tflight-data + Tflight-clk) + 0.5 < 6 (5.14)

2 + (Tflight-data + Tflight-clk) > 1.4 (5.15)

计算结果如下:

0 < Tflight-data - Tflight-clk < 0

-0.6 < Tflight-data + Tflight-clk < 0

要求数据与时钟的走线延时之和小于 0,显然是不现实的,因此在本设计中,不能将寄存器设置为 0x00。

(2)寄存器=0x58,各时序参数值如下:

Tco(max)_G= 4ns, Tco(min)_G= 1ns,

Tsu(min)_G= 0.5ns, Th(min)_G= 2.4ns,

Tco(max)_S = 5.5ns, Tco(min)_S = 2ns,

Tsu(min)_S = 1.5ns, Th(min)_S = 1ns

代入式(5.8)~(5.11),有:

4 + (Tflight-data - Tflight-clk) + 1.5 < 6 (5.16)

1 + (Tflight-data - Tflight-clk) > 2.4 (5.17)

5.5 + (Tflight-data + Tflight-clk) + (-0.5) < 6 (5.18)

2 + (Tflight-data + Tflight-clk) > 2.4 (5.19)

计算结果如下:

0 < Tflight-data - Tflight-clk < 0.5

0.4 < Tflight-data + Tflight-clk < 1

该结果符合要求,因此 0x58 是可选的寄存器参数值。

(3)寄存器=0x40,依据同样的方法,可得到计算结果如下:

0 < Tflight-data - Tflight-clk < 0.5

0.6 < Tflight-data + Tflight-clk < 1.4

该结果符合要求,因此 0x40 同样是可选的寄存器参数值。

(4)寄存器=0x48,计算结果如下:

0.9 < Tflight-data - Tflight-clk < 1.6

该结果符合要求,因此 0x48 也是可选的寄存器参数值。

(5)寄存器=0x4C,依据同样的方法,可得到计算结果如下:

0 < Tflight-data - Tflight-clk < 0.5

1.2 < Tflight-data + Tflight-clk < 1.8

该结果符合要求,因此 0x4C 也是可选的寄存器参数值。

(6)结论。对于 DATA SDRAM,0x58、0x40、0x48、0x4C 是可选的寄存器参数值,但在本设计中,SWITCH1 与 SDRAM 相距较近,走线长度没有必要很长(在第 8 章将提到,走线长度太长,可能引发信号质量等问题),因此 0x58 是最优的寄存器参数值,此时,CLK 和 DATA 信号走线延时的关系为:

0 < Tflight-data - Tflight-clk < 0.5

0.4 < Tflight-data + Tflight-clk < 1

2)CONTROL SDRAM 的时序计算

对 CONTROL SDRAM 接口的时序计算,方法与 DATA SDRAM 相同,此处不再赘述。有兴趣的读者可自行计算并验证,0x00 是最佳的寄存器参数值,此时,CLK 和 DATA 信号走线延时的关系为:

0 < Tflight-data-Tflight-clk < 0.5

0.4 < Tflight-data+Tflight-clk < 0.8

理解要点:

源同步系统时序计算的公式为:

Tco(max)+(Tflight-data+Tflight-clk)+Tsu(min)+C_JIT+D_CTLK < Tcycle

Tco(min)+(Tflight-data-Tflight-clk)-Th(min)-C_JIT-D_CTLK > Th(min)

3.3 源同步系统时序设计范例二

1. 时间窗在时序计算中的应用

在开始范例的讨论之前,先介绍一种在源同步系统中,相对式(5.6)、式(5.7),更为常用的时序计算方法,即时间窗法。

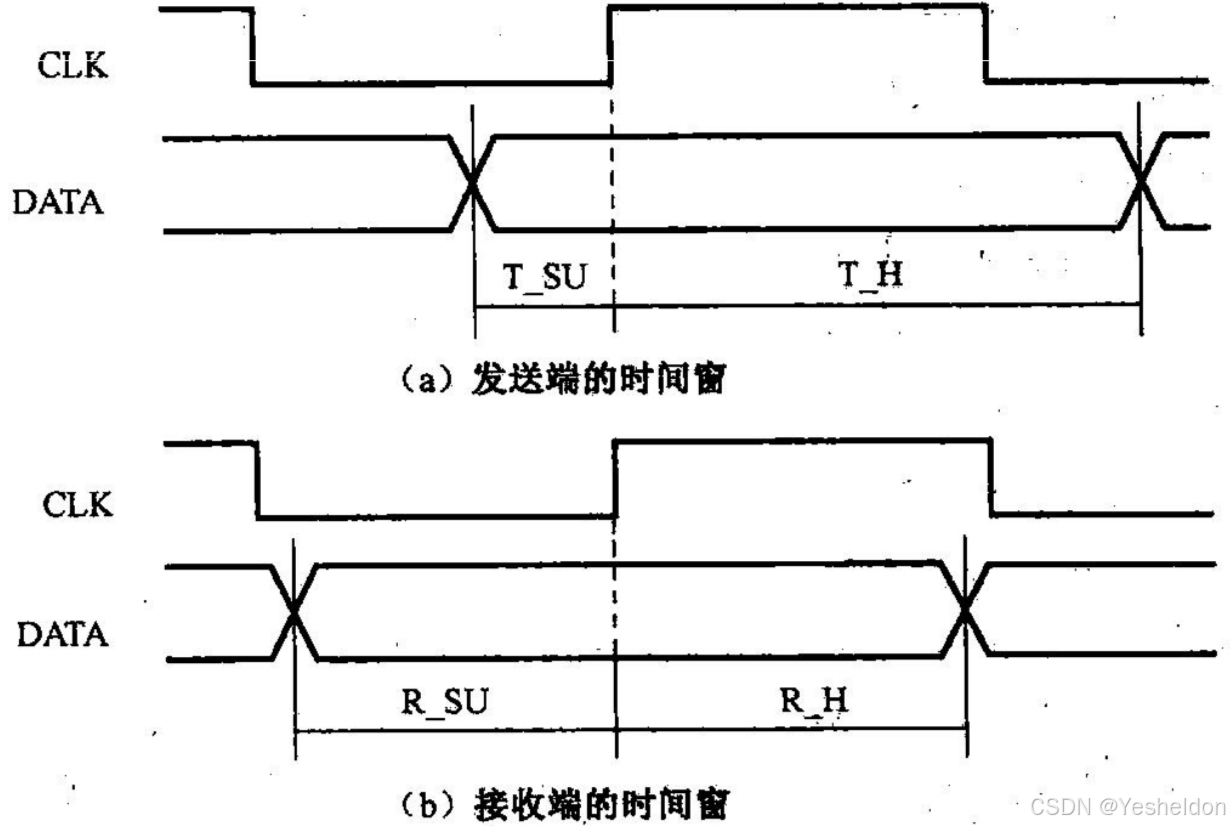

由于源同步系统的时钟 CLK 和数据 DATA 都源自同一发送端器件,因此,可以简单地利用时间窗平移,获得最佳的时序裕量。

如下图(a)所示发送端的时序关系,T_SU、T_H 分别为在发送端测得的数据 DATA 相对时钟 CLK 的建立时间和保持时间,下图(b)表示接收端的时序关系,R_SU、R_H 分别为在接收端测得的数据 DATA 相对时钟 CLK 的建立时间和保持时间。需要说明的是,R_SU、R_H 就是在前面提到的 Tsu、Th 参数,而 T_H 本身与时序要求无关,但这两个参数对时间窗的运用有重要的意义。

时间窗的应用有两个步骤:

第一步,衡量发送端的时钟窗口是否大于接收端的时钟窗口。当且仅当式(5.20)成立时,接收端的时序要求才能得到满足:

T_SU + T_H ≥ R_SU + R_H (5.20)

若式(5.20)不满足,则无论采用什么方法,接收端的时序要求也不可能得到满足。

第二步,估算 CLK 和 DATA 信号的走线延时。当以下两式中的一式成立时,只有对 CLK 或 DATA 信号进行延时后,才能满足接收端建立时间和保持时间参数的要求:

T_SU < Tsu(min) (5.21)

T_H < Th(min) (5.22)

在这一步,以上两式不可能同时成立,否则,第一步就不可能通过。

若以上两式都不成立,表示 CLK 和 DATA 信号走线等长,即可直接满足接收端的时序要求。

2. 时序计算

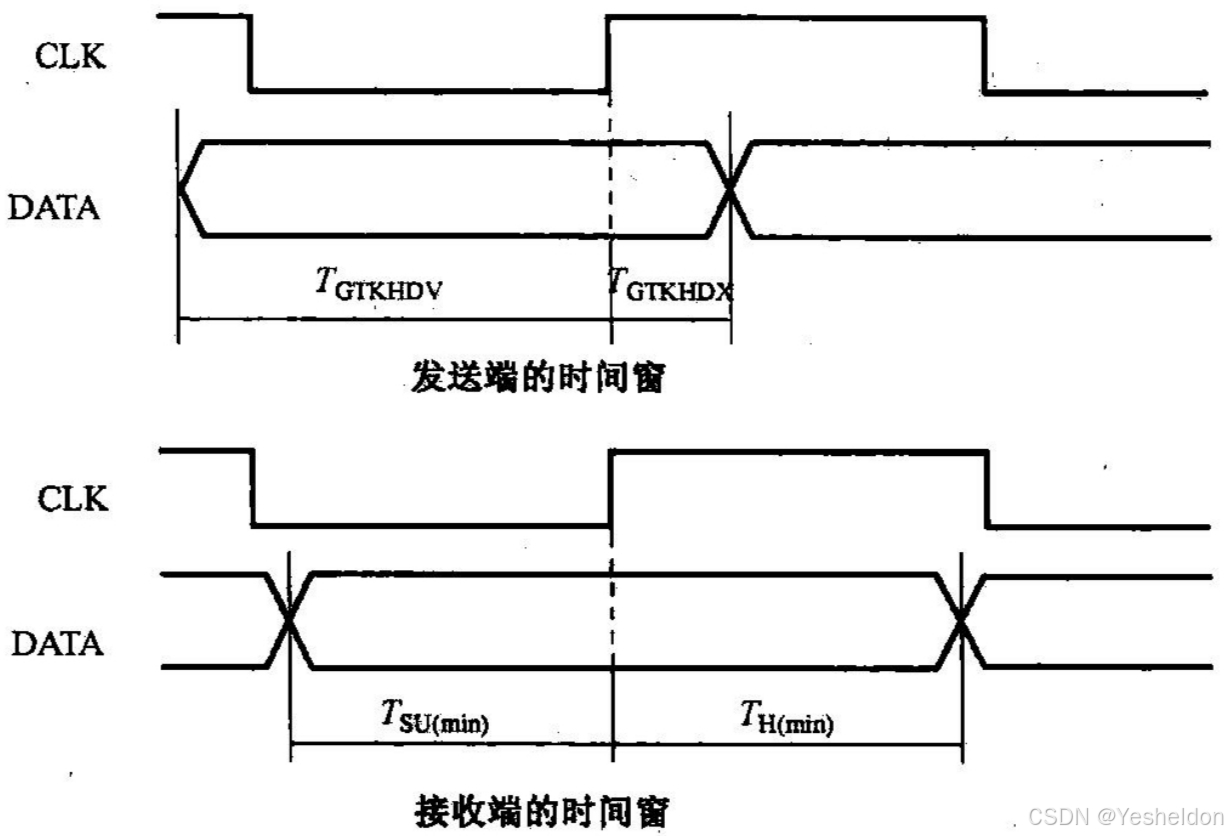

本例以 Freescale 公司的 MPC8548 与某 PHY 芯片之间的 GMII 接口(千兆速率媒质无关接口)为例,探讨基于时间窗的时序设计。

首先讨论数据流从 CPU 发送到 PHY 的这个方向。

CPU 一端的时序参数如下,

T_GTKHDV(min)=2.5ns,该参数是指 CPU 输出端的数据建立时间。

T_GTKHDV(max)=0.5ns,该参数是指 CPU 输出端的数据保持时间。

PHY 一端的时序参数如下:

Tsu(min) = 1.2ns

Th(min) = 1.2ns

发送端和接收端时间窗如下图所示。

第一步,衡量发送端的时钟窗口是否能覆盖接收端时钟窗口。

由于 T_GTKHDV(min) + T_GTKHDV(max) > Tsu(min) + Th(min),该条件满足。

第二步,估算 CLK 和 DATA 信号的走线延时。

由于 T_GTKHDV(min) < Th(min),因此需对信号线进行延时才能满足接收端的时序要求。计算可得,通过使数据 DATA 相对时钟 CLK 延时 0.7ns,能实现接收端的时序要求。此时,在接收端,数据 DATA 的建立时间裕量 Tsu(margin)=0.6ns,保持时间裕量 Th(margin)=0ns。

接下来对本例做进一步的拓展。

在第一步中,已经验证了发送端时间窗大于接收端时间窗。事实上,这两个时间窗的差正是该系统总的时间裕量,即,该系统的建立时间裕量和保持时间裕量的总和 T_total(margin) 为:

Ttotal(margin) = T_GTKHDV(min) + T_GTKHDV(max) - Tsu(min) - Th(min) (5.23)

由于接收端总的时间裕量一定,Tsu(margin) 越大,则 Th(margin) 越小,反之亦然。

最优的时序设计是建立时间裕量和保持时间裕量相等的情形。因此当式(5.24)成立时,时序设计达到最优:

Tsu(margin) = Th(margin) = 0.5 × Ttotal(margin) (5.24)

显然,在前面的计算结果中,Tsu(margin) 占据了 T_total(margin) 的全部,而 Th(margin) 为 0,这样的时序设计不是最优的。将该结果做进一步的优化,使数据 DATA 相对时钟 CLK 延时 1ns,此时,在接收端,Tsu(margin)=Th(margin)=0.3ns。

相比较式(5.7),时间窗的计算方法具有简单直观的特点。但应用时间窗方法的前提是,发送端器件的资料上提供有类似 T_SU 和 T_H 这样的参数,许多器件的发送端接口只提供 Tco 参数,在这种情况下,仍需基于式(5.6)、式(5.7)来进行时序计算。