Cortex-M3 02-地址映射

Cortex-M3 02-地址映射

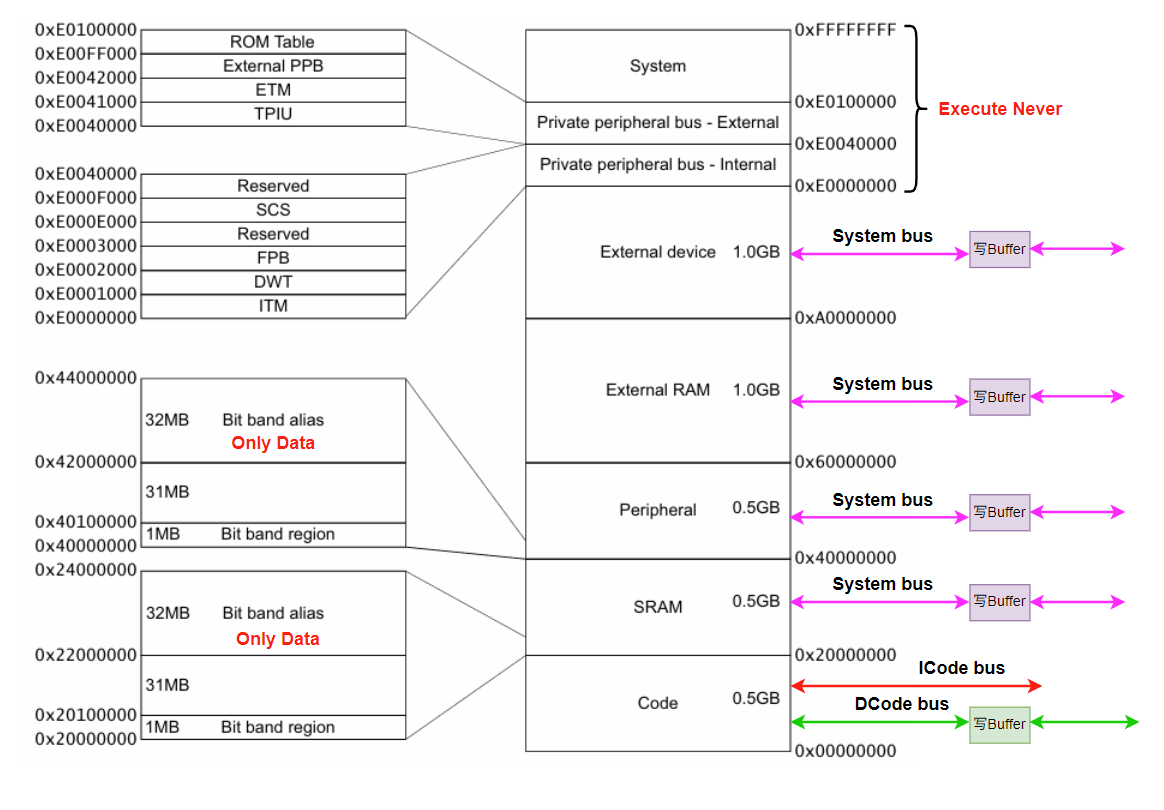

系统地址映射

支持32位的预定义内存空间,划分为八个部分:

- Code区

- 一般为ROM或flash内存,指令取指在ICode总线上执行,数据访问在DCode总线上执行;

- SRAM区

- 一般为片上RAM,指令取指和数据访问都在系统总线上执行;

- Peripheral区

- 片上外设空间,指令取指和数据访问都在系统总线上执行;

- RAM区(两部分)

- 外部RAM,指令取指和数据访问都在系统总线上执行;

- Device区(两部分)

- 分为共享设备和非共享设备空间,指令取指和数据访问都在系统总线上执行;

- System区

- 包含PPB的系统段和厂商自定义的系统外设;

- 对于PPB段寄存器的访问,限制为 Strongly-ordered memory,小端访问,仅支持字对齐访问,不支持 byte and halfword访问。

- SCS(System Control Space) 容量为4KB,划分为系统控制和定义、CPUID处理器自定义空间、系统配置和状态、故障报告、系统定时器、Nested Vectored Interrupt Controller (NVIC)、 Protected Memory System Architecture (PMSA)和系统调试。

Cortex-M3支持非对齐访问,通过DCode和System总线接口可以将非对齐的指令转换成多个对齐的指令,从而实现非对齐的访问。非对齐的访问仅限于单 load/store指令,PPB空间不支持非对齐访问。在数据和指令以及系统总线上有一个写buffer,这个buffer的作用提高系统写入数据的效率。指令DMB和DSB两个可以刷新该buffer,将buffer内的数据写入指定的地址空间。

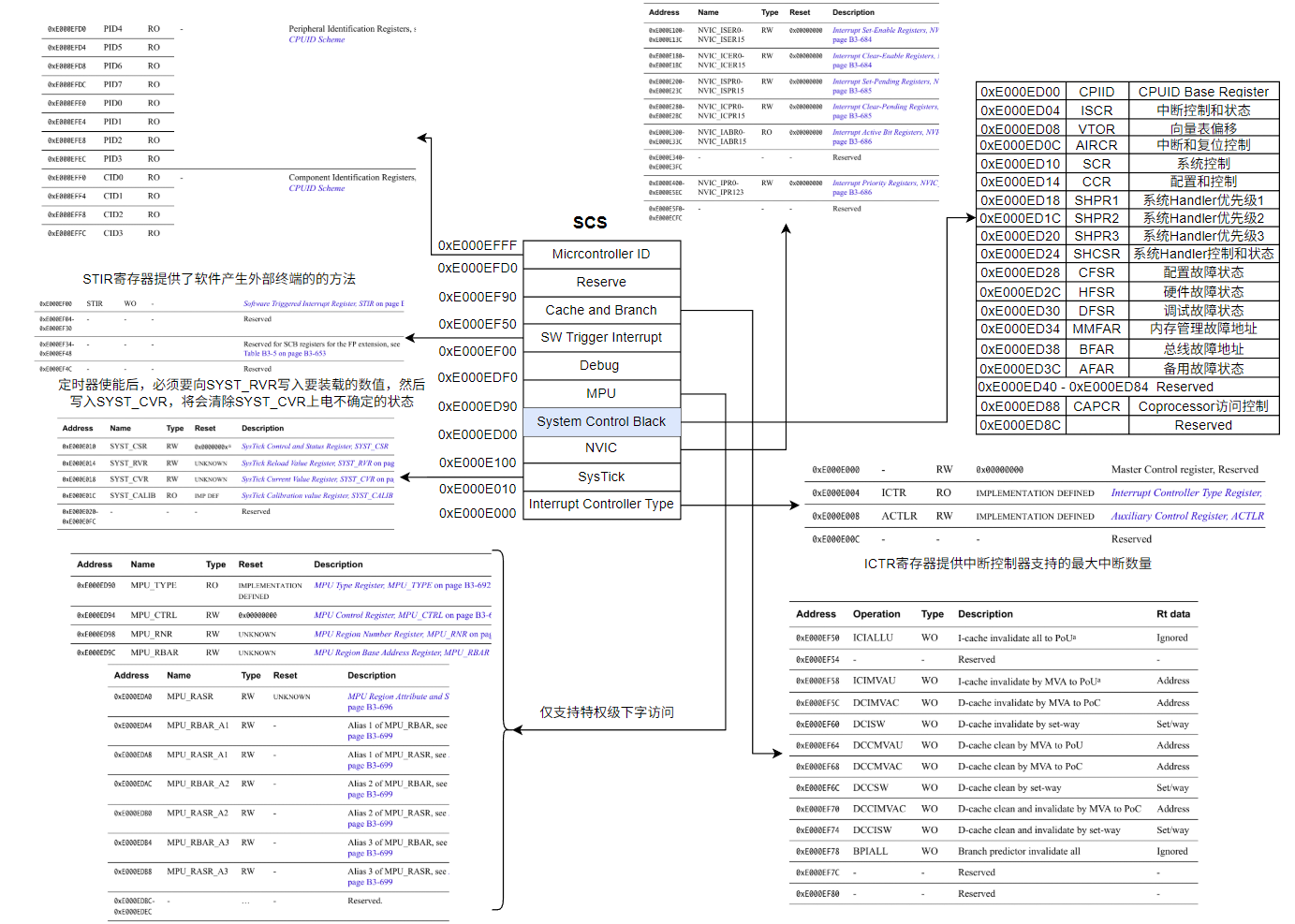

System Control Space

System Control Space 系统控制空间是以4KB映射的地址空间,提供32bit的寄存器用于关键特性状态和控制特性设定,空间下的寄存器分为以下几组:

- 系统控制和识别

- CPUID处理器识别

- 系统配置与状态

- 故障报告

- 嘀嗒定时器

- 嵌套向量中断控制器

- 内存保护

- 系统调试

系统控制器块

在SCS空间下包含系统控制块,系统控制块提供关键特性信息的状态和配置,如软件复位控制、中断模型的基地址管理、系统中断管理(中断使能,状态查看,设置中断状态,设置优先级)、优先级分组控制、电源管理、故障状态信息和调试状态信息。

- CPUID Base Register : 提供处理器的识别信息;

- Interrupt Control and State Register, ICSR : 提供NMI、PendSV和SysTick的软件控制方法和状态信息;

- Vector Table Offset Register, VTOR:保存向量表的地址;

- Application Interrupt and Reset Control Register, AIRCR: 设置或返回中断控制数据;

- System Control Register, SCR: 设置或返回系统控制数据;

- Configuration and Control Register, CCR: 设置或返回配置和控制数据,配置cache和分支预测;

- System Handler Priority Register 1, SHPR1: 设置或返回系统中断4-7的优先级;

- System Handler Priority Register 2, SHPR2:设置或返回系统中断8-11的优先级;

- System Handler Priority Register 3, SHPR3:设置或返回系统中断12-15的优先级;

- System Handler Control and State Register, SHCSR: 控制和提供系统例外的active和pending状态;

- Configurable Fault Status Register, CFSR: 包含MemManage、 BusFault和 UsageFault,其中MemManage域显示MPU的状态信息,BusFault记录来自取指令和数据访问带来的错误信息,UsageFault记录指令的执行错误信息和数据的访问错误状态信息;

- HardFault Status Register, HFSR: 记录一切HardFault的原因;

- MemManage Fault Address Register, MMFAR: 记录当MPU故障时的内存地址;

- BusFault Address Register, BFAR: 记录数据访问错误时的地址;

- Auxiliary Fault Status Register, AFSR: 备用故障状态寄存器;

- Coprocessor Access Control Register, CPACR:指定协处理器的访问;

- Interrupt Controller Type Register, ICTR: 记录中断控制器的一些信息;

- Software Triggered Interrupt Register, STIR: 提供软件触发外部中断的方法;

具体寄存器的定义请查看ARM v7-M Architecture Reference Manual - B3.2.2 System control and ID registers。

嘀嗒定时器

嘀嗒定时器是ARMv7-M的必要组成部分,可以为RTOS实时操作系统提供基础tick,也可以在裸机中当作普通定时器使用。该模块包括四个寄存器,分别为:

- 控制和状态寄存器:用于配置 SysTick的时钟,使能 SysTick中断和记录计数器的状态;

- 重装载寄存器:记录重装载的数值;

- 当前数值寄存器:显示当前的计数值;

- 数值校准寄存器:记录着10ms时的重装载值;

具体寄存器的定义请查看ARM v7-M Architecture Reference Manual - B3.3.2 System timer register support in the SCS。

嵌套向量中断控制器

Nested Vectored Interrupt Controller, NVIC最多支持496个中断,通过读ICTR寄存器可以了解实际支持的中断数量,支持电平和脉冲输入信号。除此之外,还支持以下特性:

- 可以通过 Interrupt Set-Enable or Interrupt Clear-Enable中断使能或清除寄存器来控制中断的开和关;

- 软件可以通过Set-Pending Register and Clear-Pending 寄存器控制中断的pending状态;

- 软件可以通过Active bit来确定中断的状态;

在SCS空间下的ICTR和STIR 寄存器与NVIC相关,其中ICTR是一个只读寄存器,记录着外部中断的数量,STIR寄存器是一个只写的寄存器,通过写入可以改变外部中断的pending状态。在NVIC中与外部中断相关的寄存器还有以下几组:

- Interrupt Set-Enable Registers,ISER:中断设置使能寄存器,一共16组,具体使用几组由ICTR寄存器的INTLINESNUM决定,寄存器的32bit对应32个外部中断。

- Interrupt Clear-Enable Registers, ICER:中断关闭寄存器,数量同上,写1关闭中断;

- Interrupt Set-Pending Registers,ISPR:中断使能Pending寄存器,数量同上,可以改变中断的pending状态,例如写1将中断状态改为pending;

- Interrupt Clear-Pending Registers, ICPR:中断清除Pending寄存器,数量同上;

- Interrupt Active Bit Registers,IABR:中断激活位寄存器,数量同上,只读寄存器,0代表中断处于unactive状态,1代表中断处于active状态;

- Interrupt Priority Registers, IPR: 中断优先级寄存器,一共124组,每个32bit寄存器分成4组,每组代表一个外部中断的优先级,一共可以设置124*4=496个中断的优先级。

具体寄存器的定义请查看ARM v7-M Architecture Reference Manual - B3.4.3 NVIC register support in the SCS。

MPU 内存保护单元

MPU是内存的保护单元,是ARMv7-M可选的一个组件,由于是一个可选的组件,在这里只讨论下不支持MPU时的行为,具体请参考ARM v7-M架构手册。当MPU关闭时,指令的访问使用默认的系统映射属性,只有一个限制,就是在访问 Execute-Never区域时会产生MemManage的例外。数据的访问使用默认的系统映射,没有限制;程序流的猜测功能正常,推测执行也是正常的。

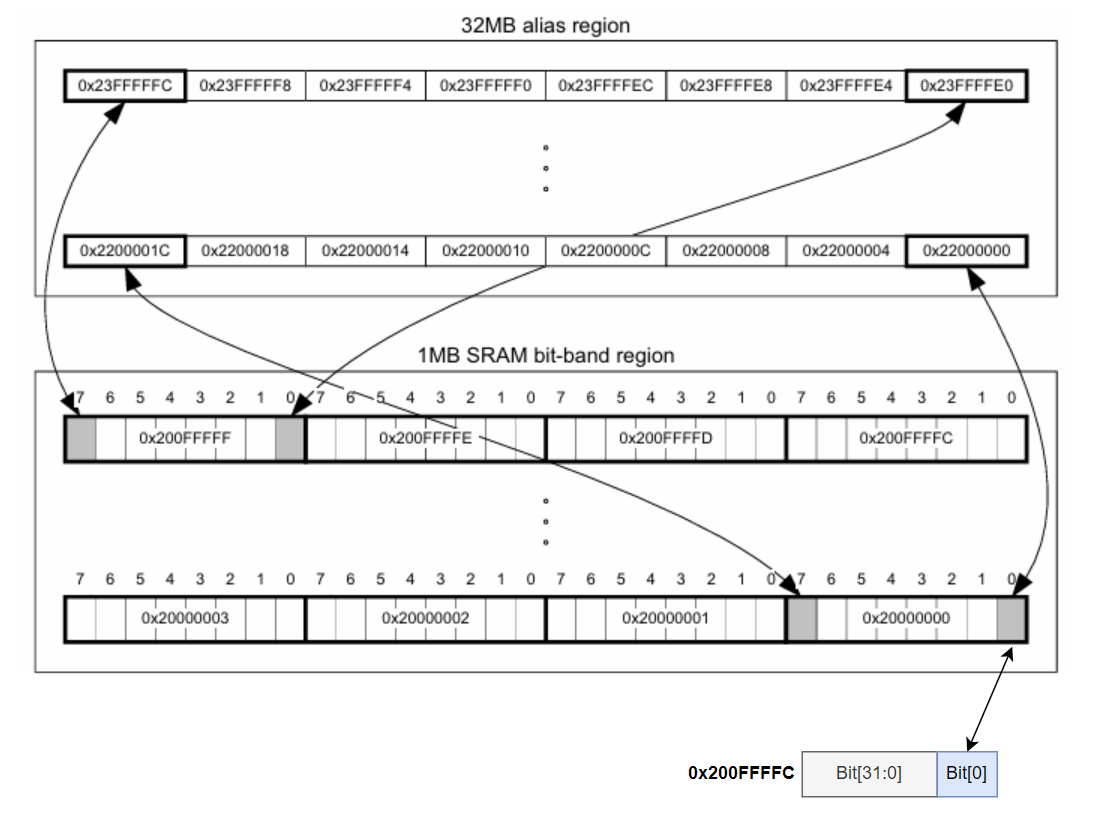

Bit-banding访问

在系统地址空间中有两段内存支持Bit-banding访问,分别是SRAM区的0x20000000~0x20100000和外设区的0x40000000-0x4010000,大小为1MB的空间。Bit-banding访问的方式大致可以理解为在其他的地址空间有一个别名或者理解为地址,通过这个地址可以访问上述两个区,这里核心点在于访问的形式是Bit。

SRAM区的0x20000000~0x20100000对应的alias区为0x22000000-0x23FFFFFC,例如访问0x22000000实则是对0x20000000的Bit0进行读写。外设区的0x40000000-0x4010000对应的alias区为0x42000000-0x44000000。在对alias区访问时只有Bit[0]是有效的,其他31位的数值是忽略的。下面有一个计算公式,算 bitWordAddr地址:

bitWordOffset=(byteOffset∗32)+(bitNumber∗4)

bitWordOffset = (byteOffset*32) + (bitNumber * 4)

bitWordOffset=(byteOffset∗32)+(bitNumber∗4)

bitWordAddr=bitBandBase+bitWord0ffset bitWordAddr = bitBandBase + bitWord0ffset bitWordAddr=bitBandBase+bitWord0ffset

其中bitWordOffset是Bit位在对应区的偏移,bitBandBase是alias区的起始地址;

思考设计Bit-banding的访问形式有何意义?

Bit-banding访问在仅修改某一个位的场合中发挥作用,可以将原理的读-改位-写三个步骤简化成一步,通过访问这一位对应的alias区的地址就可以轻松的实现这一位的读写。

总结

Cortex-M内核是采用ARMv7-M指令集设计的处理器核,在ARMv7-M指令集中设定了处理器核大致的内存分布,芯片厂商仅需根据这个大致分布去添加外部的存储或外设器件即可。因此使用Cortex-M内核的微处理器存储映射大致相同。在地址映射中,由一个特殊的区域,称为Bit-bangding,通过该机制,可以更方便的访问外设和RAM区。地址映射还有一个区域,称为系统控制空间,里面包含了用于中断、嘀嗒定时器和调试等相关的寄存器设置,我在此称为内核相关寄存器。