FPGA教程系列-Vivado IP核DDS核

FPGA教程系列-Vivado IP核DDS核

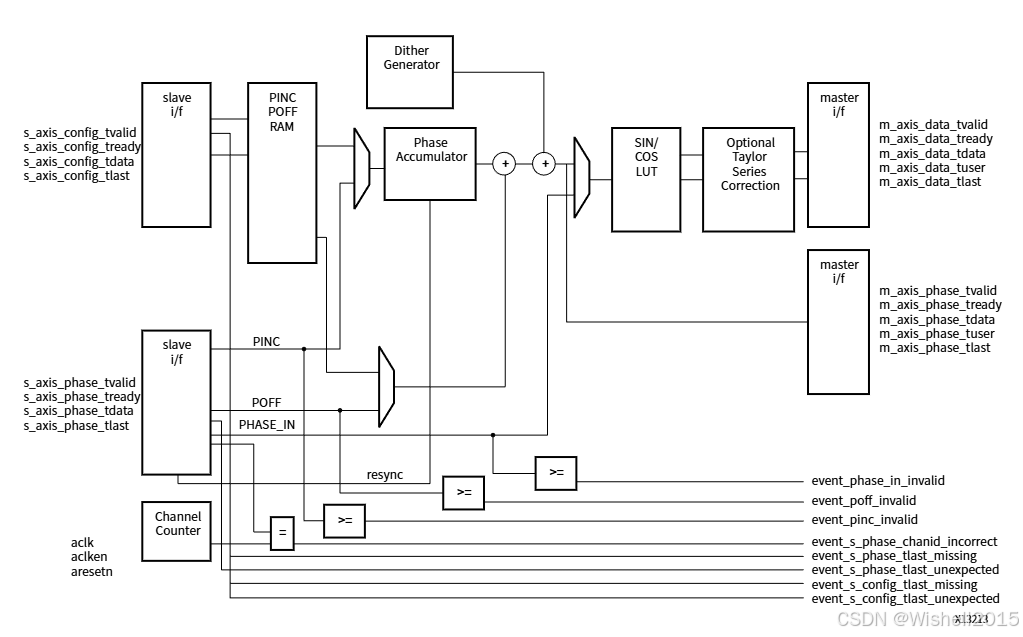

直接数字合成器(DDS)或数控振荡器(NCO)是许多数字通信系统的重要组成部分。正交合成器用于构建数字下行和上行转换器和解调器。它们还用于实现各种类型的调制方案,包括 PSK(相移键控)、FSK(频移键控)和 MSK(最小移位键控)。数字生成复值或实值正弦波的常用方法是采用查找表方案。查找表存储正弦波的样本。数字积分器用于生成合适的相位参数,该参数由查找表映射到所需的输出波形。简单的用户界面可接受系统级参数,如所需的输出频率和生成波形的杂散抑制。直接数字合成器(DDS)或数控振荡器(NCO)是许多数字通信系统的重要组成部分。正交合成器用于构建数字下行和上行转换器和解调器。它们还用于实现各种类型的调制方案,包括 PSK(相移键控)、FSK(频移键控)和 MSK(最小移位键控)。数字生成复值或实值正弦波的常用方法是采用查找表方案。查找表存储正弦波的样本。数字积分器用于生成合适的相位参数,该参数由查找表映射到所需的输出波形。简单的用户界面可接受系统级参数,如所需的输出频率和生成波形的杂散抑制。

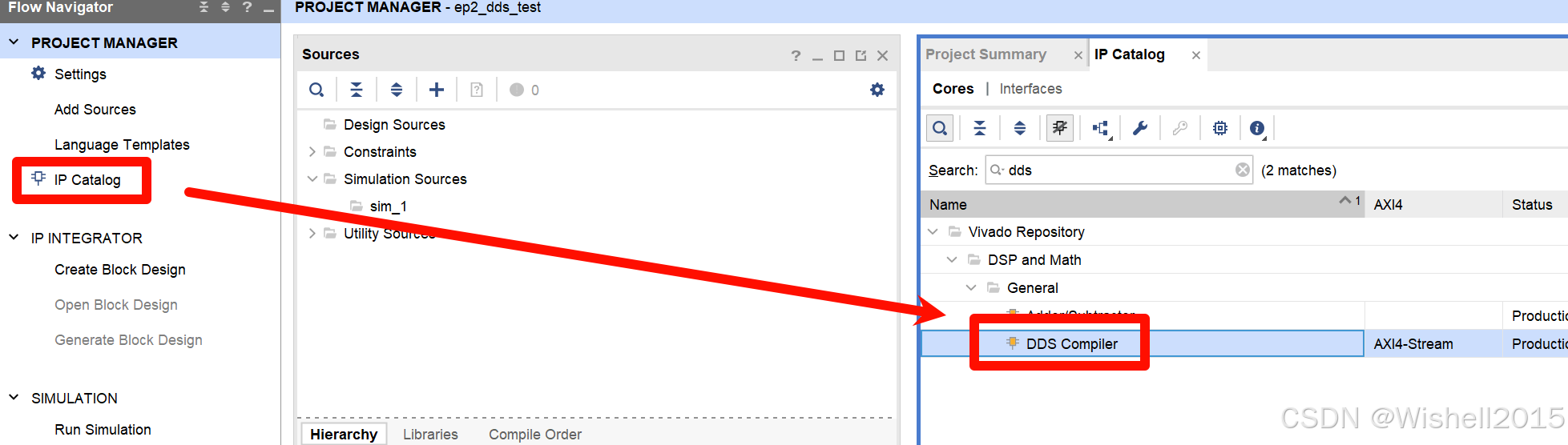

进入IP核设置

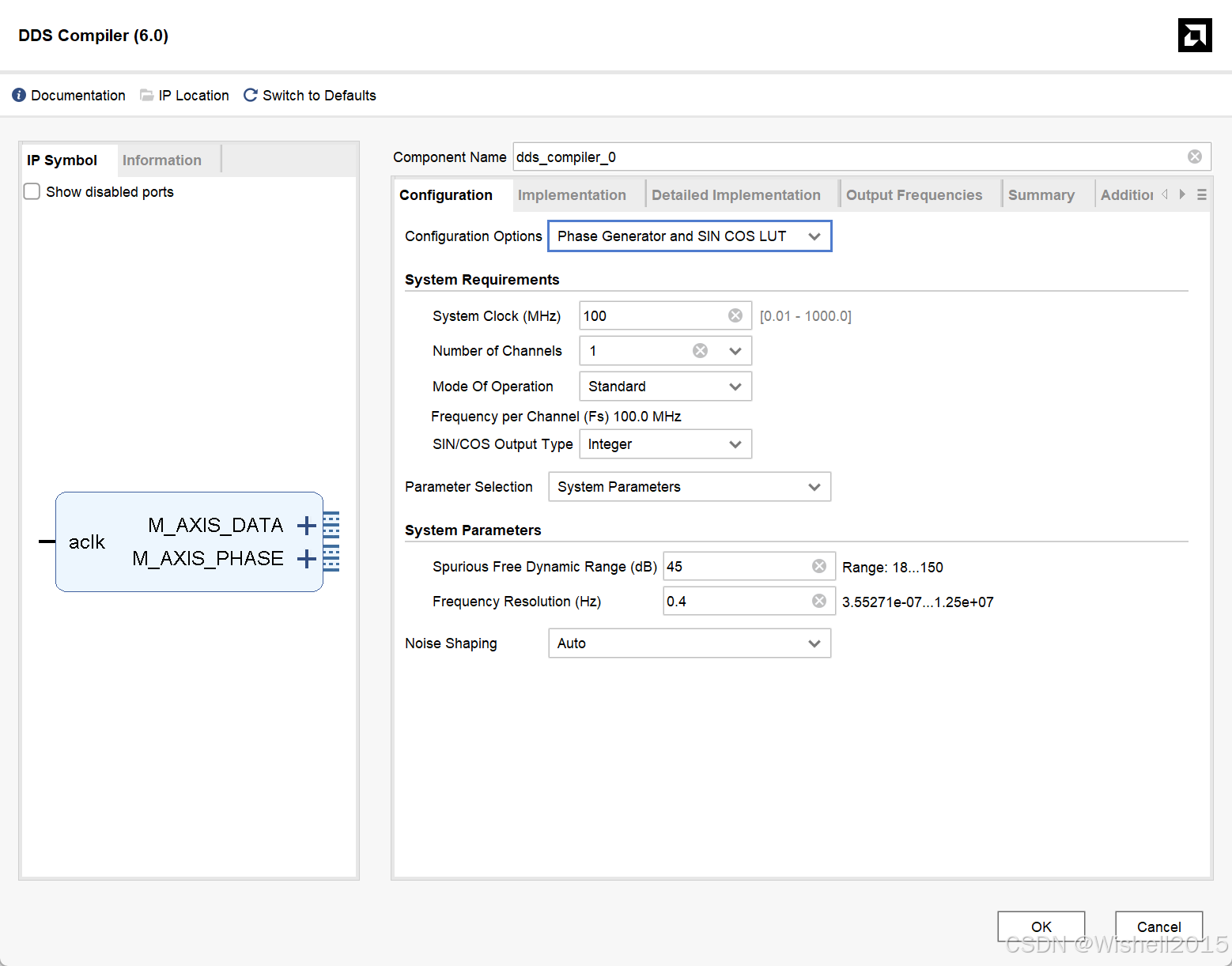

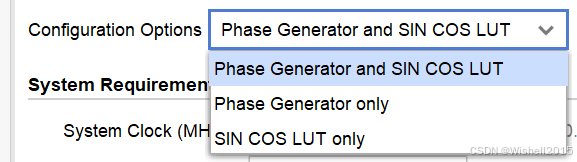

模式配置

Phase Generator:相位发生器由一个累加器和一个可选的加法器组成,用于添加相位偏移。在定制内核时,相位增量(PINC)和相位偏移(POFF)可独立配置为固定、可编程(使用 CONFIG 通道)或流式(使用输入 PHASE 通道)。

SIN/COS LUT:当仅配置为正弦/余弦 LUT 时,不执行相位发生器, PHASE_IN 信号使用输入 PHASE 通道输入,并使用查找表转换为正弦和余弦输出。通过利用正弦波形的对称性,实现了高效的内存使用。内核可配置为仅正弦输出、仅余弦输出或两者(正交)输出。每个输出可独立配置为负输出。使用可选的泰勒级数校正功能可提高精度。这就利用了支持 DSP 片的 FPGA 系列,实现了高速运行下的高 SFDR。

Phase Generator and SIN/COS LUT (DDS):相位发生器与 SIN/COS LUT 配合使用,可提供相位截断 DDS 或泰勒级校正 DDS。可在这两个模块之间添加一个可选的抖动发生器,以提供相位抖动 DDS。

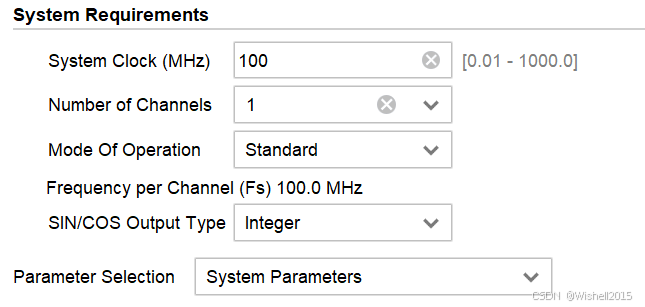

系统设置

system clock(MHz)系统时钟:50MHz工作时钟,即50MHz采样率。

Number of chanels通道数量:设为1,单通道模式,通道的采样频率等于采样时钟50MHz。如果设置多通道模式,那么每个通道的频率为50MHz/N,N为通道数量。

Mode of operation模式:Standard标准模式,Rasterized栅格模式。两种情况下,输出的频率和频率分辨率、相位增量等参量的计算方式不同。Standard模式下计算出来的相位增量可能是小数,而在FPGA中要对相位进行截断取整,存在相位误差,对噪声要求较高的场合,可以使用8处的噪声整形配置来弥补,使用相位抖动(Phase Dithering)或者泰勒级数纠正(Taylor Series Correct)来补偿相位误差;Rasterized Mode配置下,相位增量一定是整数,不存在截断效应,没有Standard模式下的时间基抖动。

一般情况下,多选择Standard标准模式。

system Parameters系统参数:包括System parameters和Hardware parameters。一般设置System parameters。

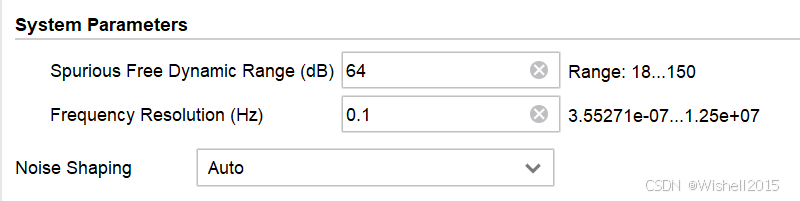

系统参数

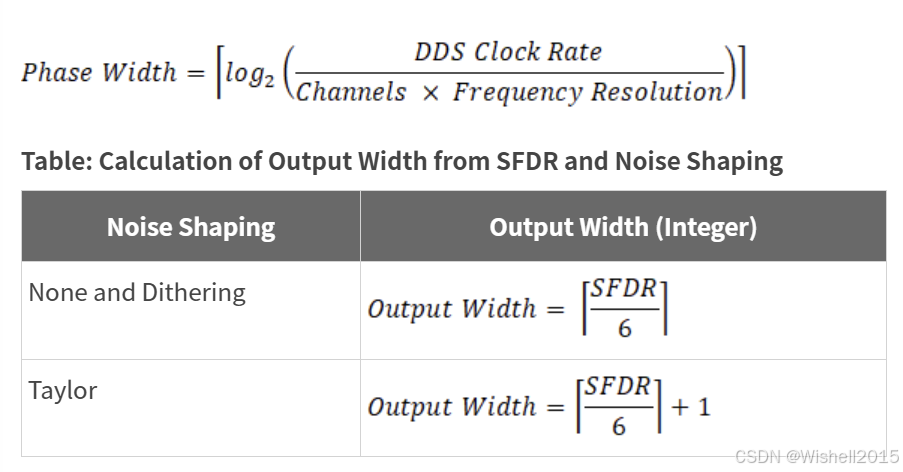

SpuriousFree Dynamic Range无杂散动态范围:对应幅度,对应M_AXIS_DATA通道,SFDR越大,用于表示幅度的数据的位宽越大.其输出位宽满足如下公式:

Frequency Resolution配置频率分辨率:对应相位的增量配置、位宽,对应M_AXIS_PHASE通道,频率分辨率越小,用于表示相位的数据的位宽越大;

Noise shape: Auto根据设计的SFDR参数自动选择是否使用整形;None不整形;Phase Dithering相位抖动,在使用相位截断技术时,产生随机的噪声来使得量化误差随机;

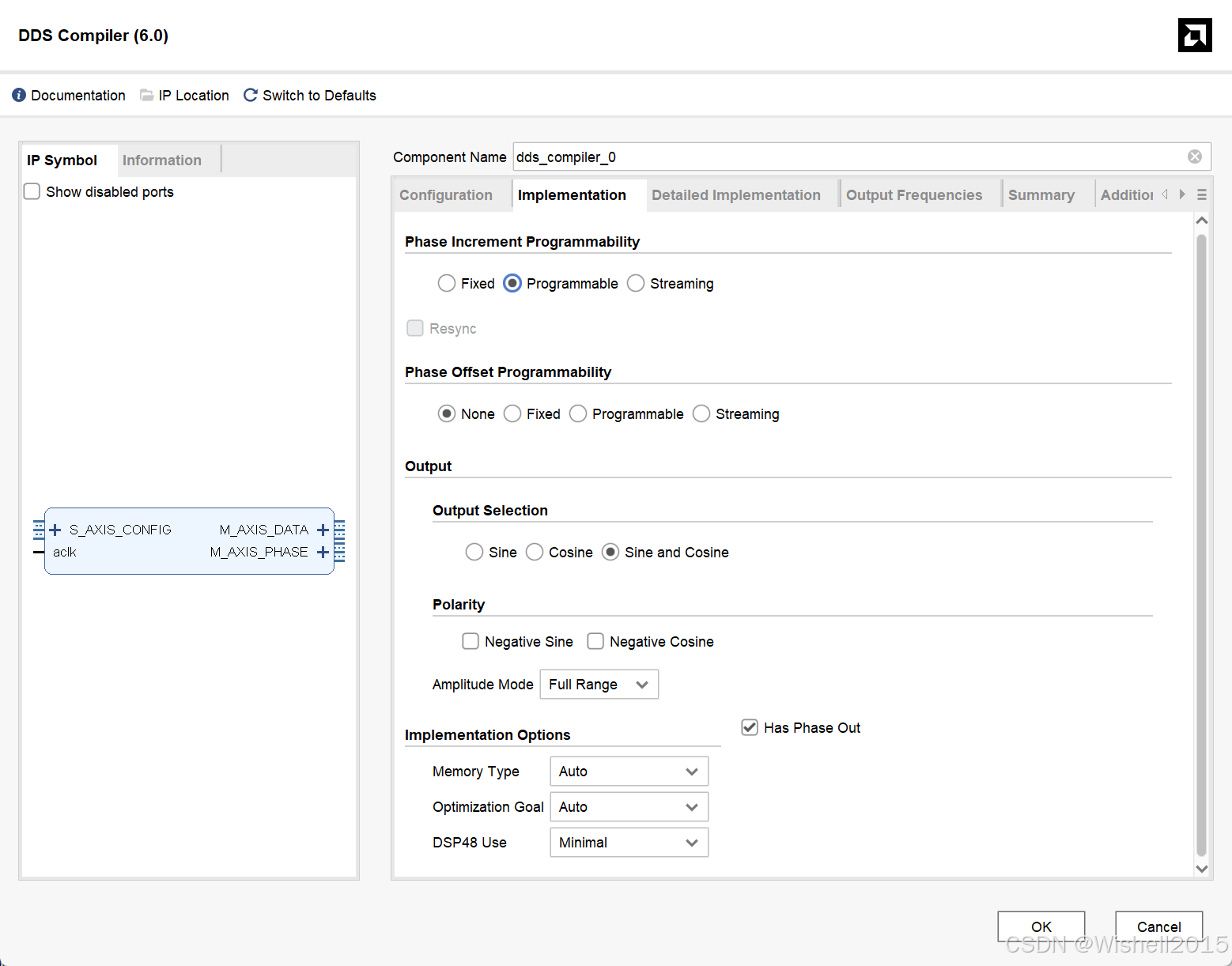

Phase Increment Programmability(相位增量可编程性)

- Fixed(固定) :相位增量为常数,输出频率不可动态调整

- Programmable(可编程) :相位增量可通过外部接口实时修改,实现动态调频(最常用)

- Streaming(流式) :相位增量以数据流形式持续输入,适合高速连续频率变化

Resync(重同步)

- 勾选后,当参数更新时自动插入重同步周期,使相位平滑过渡

- 避免信号出现相位跳变,适用于对相位连续性要求高的应用

Phase Offset Programmability(相位偏移可编程性)

- None(无) :无相位偏移,从0相位开始

- Fixed(固定) :固定的初始相位偏移

- Programmable(可编程) :可实时修改相位偏移,实现动态相移

- Streaming(流式) :连续相位变化输入

Output Selection(输出选择)

- Sine(正弦波) :仅输出正弦信号

- Cosine(余弦波) :仅输出余弦信号

- Sine and Cosine(正弦+余弦) :同时输出两种信号(最常用)

Polarity(极性)

- Negative Sine(负正弦) :输出反相正弦波

- Negative Cosine(负荷弦) :输出反相余弦波

- 未勾选时输出正常极性信号

Amplitude Mode(幅度模式)

- Full Range(全范围) :输出幅度覆盖DAC满量程

- 其他选项限制幅度范围,用于降低功耗或匹配电路电平

Has Phase Out(是否包含相位输出)

- 勾选后额外输出当前相位值,用于监控或反馈控制

Memory Type(存储器类型)

- Auto(自动) :工具自动选择最优存储器

- Block RAM:使用专用块RAM(速度快,数量有限)

- Distributed RAM:使用分布式RAM(资源丰富,速度较慢)

Optimization Goal(优化目标)

- Auto(自动) :工具自动优化

- Speed(速度) :优先提高工作频率

- Area(面积) :优先减少资源消耗

DSP48 Use(DSP48单元使用)

- Minimal(最小化) :尽量少用DSP48乘法器

- Auto(自动) :工具自动分配

- Maximum(最大化) :尽可能多用DSP48

配置建议

- 需要动态调频/相移:选择"Programmable"模式

- 需要高精度相位连续性:勾选"Resync"

- 需要多通道信号:选择"Sine and Cosine"输出

- FPGA资源紧张:优先选择"Area"优化和"Minimal"DSP48使用

这些参数的合理配置直接影响DDS输出的信号质量(频率精度、相位噪声)和系统性能(工作频率、资源占用)

第三页配置默认即可。

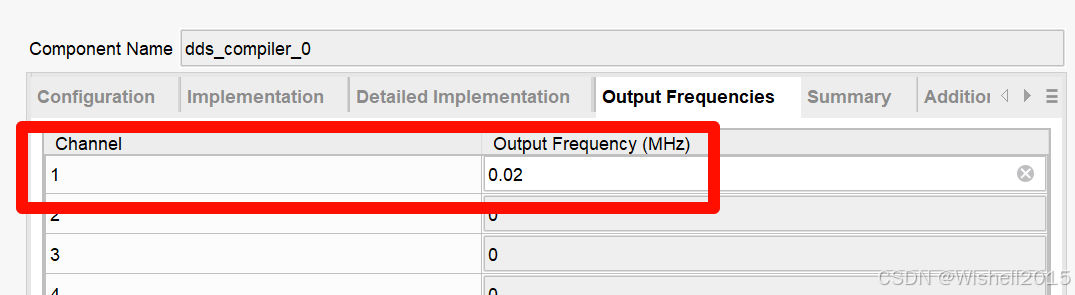

输出频率设置:

完成以后generate就可以了,还是具体根据需求进行配置。