matlab和FPGA联合仿真时读写.txt文件数据的方法

在FPGA开发过程中,往往需要将MATLAB生成的数据作为原始激励灌入FPGA进行仿真。为了验证FPGA计算是否正确,又需要将FPGA计算结果导入MATLAB绘图与MATLAB计算结果对比。

下面是MATLAB“写.txt”、“读.txt”,Verilog“读.txt”、“写.txt”的代码。.txt中的数据是二进制的。

1.MATLAB导出数据生成.txt文件:

function Write_data(filename,n,data)%filename:存储地址。n:二进制位宽。data:数据

data=round(data);

for i=1:length(data)

if(data(i)<0)

data(i)=data(i)+2^n;

end

end

bin_data=dec2bin(data,n);

fid=fopen(filename,'wt');

for j=1:size(bin_data,1)%size(array,1)表示矩阵array的行数。size(array,2)表示列数

fprintf(fid,'%s\n',bin_data(j,:));%array(i,:)表示提取矩阵array的第i行的所有元素

end

fclose(fid);

end2.MATLAB读取.txt文件导入数据:

function [data_bin2dec]=Read_Data(filename,T)%T表示.txt中的二进制位宽

data_bin_txt=textread(filename,'%s');

MAX_DATA=2^(T-1);%判断正负的阈值

data_bin2dec=zeros(length(data_bin_txt),1);%一个列向量

for i=1:length(data_bin_txt)

if(convert_bin2dec(data_bin_txt(i),0)>MAX_DATA)

data_bin2dec(i)=convert_bin2dec(data_bin_txt(i),1)-2^T;

else

data_bin2dec(i)=convert_bin2dec(data_bin_txt(i),0);

end

end

end

%%

function [x]=convert_bin2dec(bintring,sign)

if sign==0

x=bin2dec(bintring);

else

x=num2cell(bin2dec(bintring));

bin_size=size(bintring,2);

y=x;

y=cellfun(@(y,bin_size)cal_sign_y(y,bin_size),y,num2cell(ones(size(y,1),1)*bin_size));

x=y;

end

end

%%

function y_i=cal_sign_y(y_i,bin_size)

if y_i>=2^(bin_size-1)

y_i=y_i-2^bin_size;

end

end3.FPGA读取.txt文件导入数据:

reg [WIDTH-1:0] mem_a[DEPTH:0];

initial $readmemb("C:/xxx/xxx/xxx.txt",mem_a);//将.txt文件读到数组mem_a中

task data_stream();//生成数据流,用于RTL仿真

integer i;

for(i=0;i<DEPTH;i=i+1)begin

din_valid=1;

din=mem_a[i];

#20;

din_valid=0;

din=din;

#80;

end

endtaskVerilog在读.txt文件时,只能识别16进制、二进制。不要求每个数据单独占一行,但要有空格。

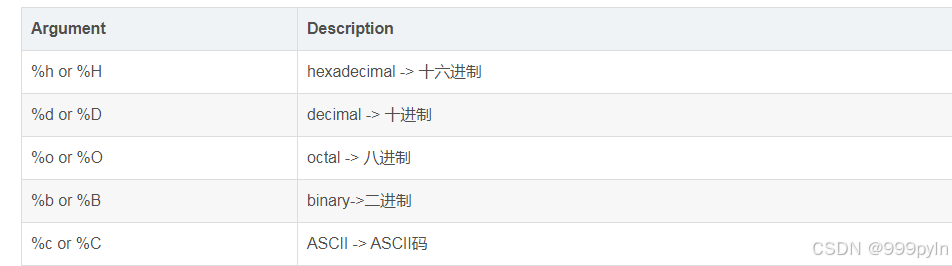

4.FPGA导出数据保存到.txt文件中:

integer bt;

initial begin

bt=$fopen("C:/xxx/xxx/fpga_out.txt"","wb");

end

always@(posedge clk)begin

if(dout_valid)

$fdisplay(bt,"%b",data_out);

end$fdisplay(bt,存储形式,想要存的数据);

生成的fpga_out.txt会自动换行;

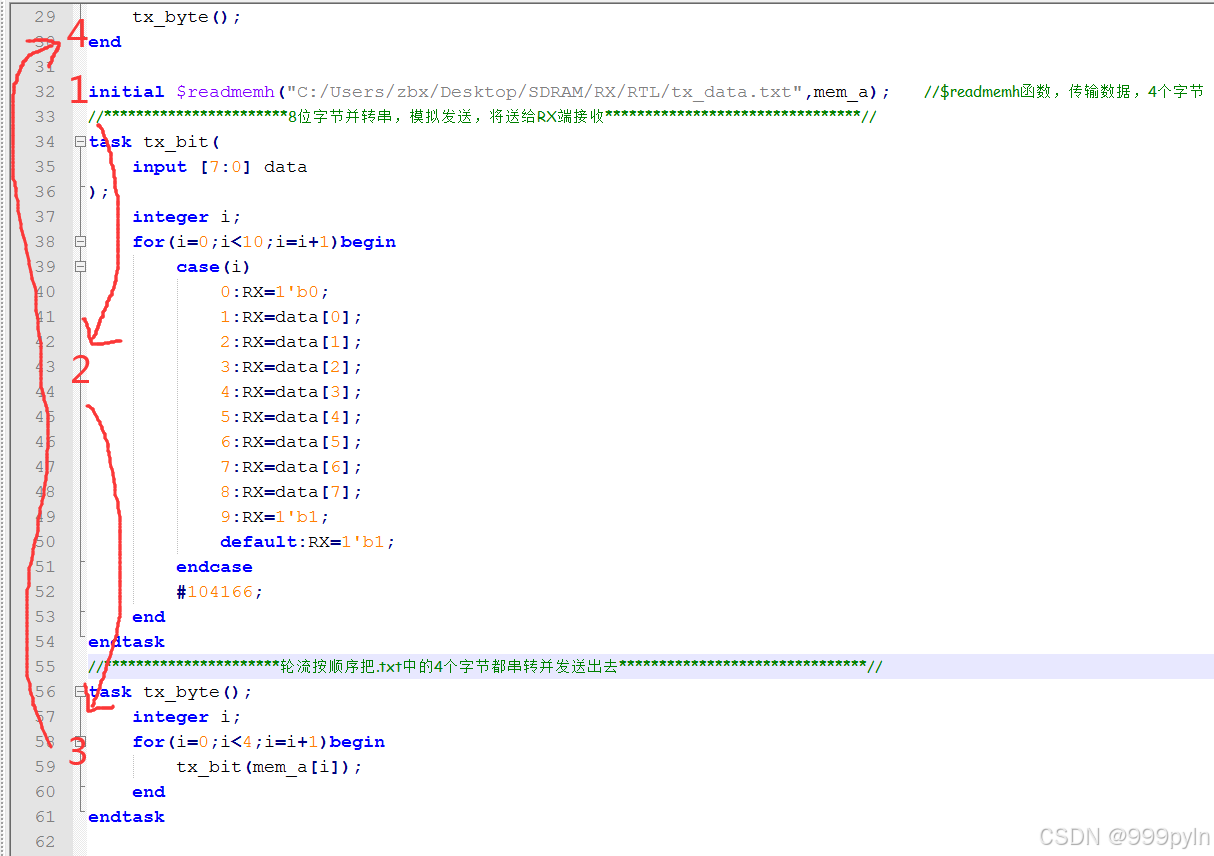

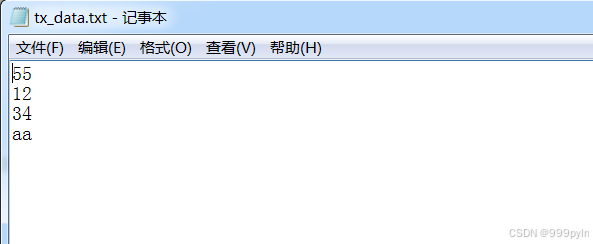

另外.FPGA读.txt,并串行输出模仿串行通信总线时: