数字电路基础——逻辑门

逻辑门是数字电子技术中的基本构建块。这些组件用于对1和0进行操作,可以将它们组合起来创建其他构建块,并设计出如锁存器、触发器、加法器、移位寄存器等电路。

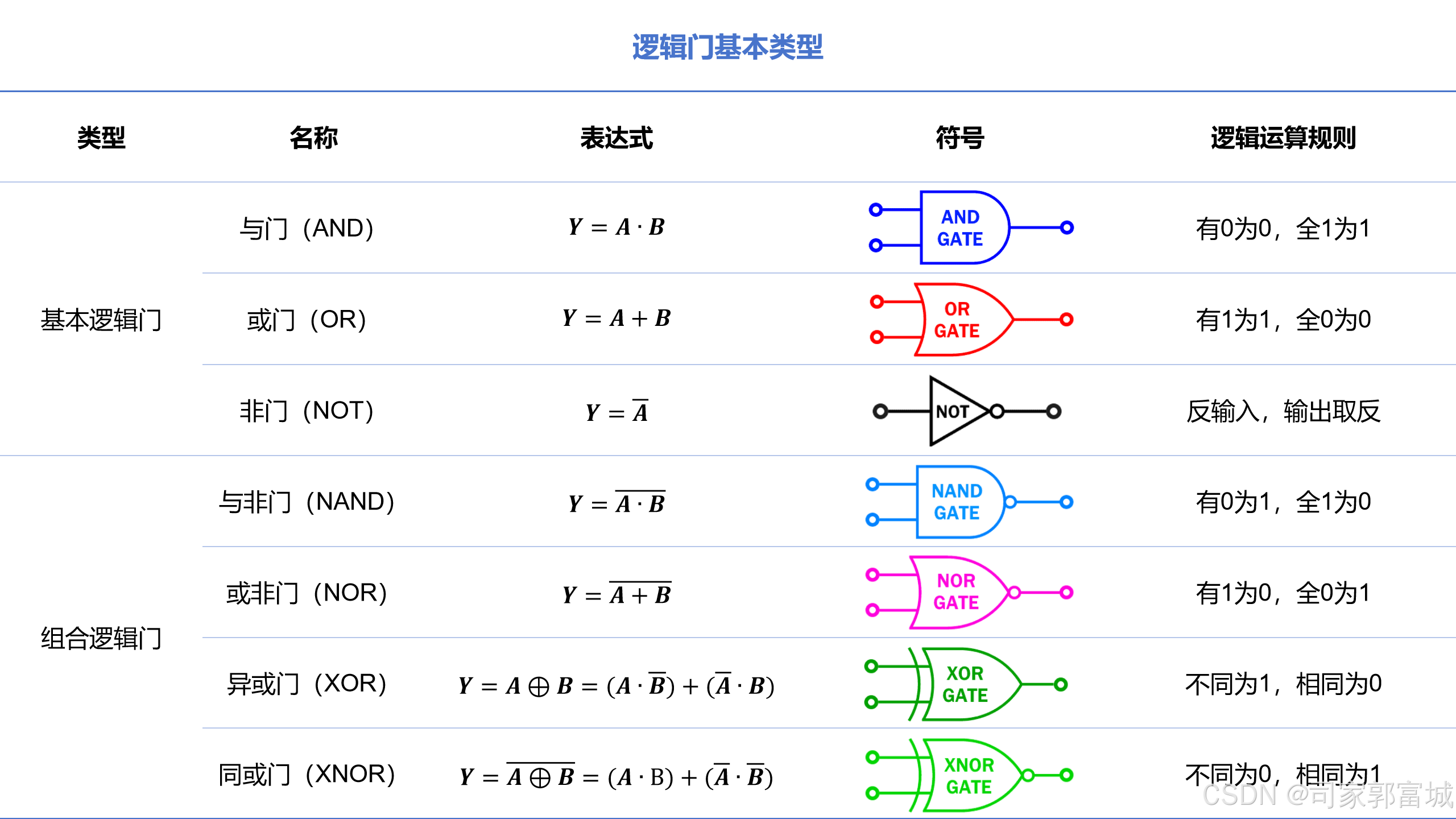

七种主要的逻辑门类型:

一、基本逻辑门

1.1 与门(AND gate)

1.1.1 逻辑运算规则

与门有多个输入端和一个输出端,只有当所有输入都为高电平(逻辑“1”)时,输出才为高电平(逻辑“1”);只要有一个输入为低电平(逻辑“0”),则输出就为低电平(逻辑“0”)。

1.1.2 逻辑符号及真值表

![]()

1.1.3 实现方式

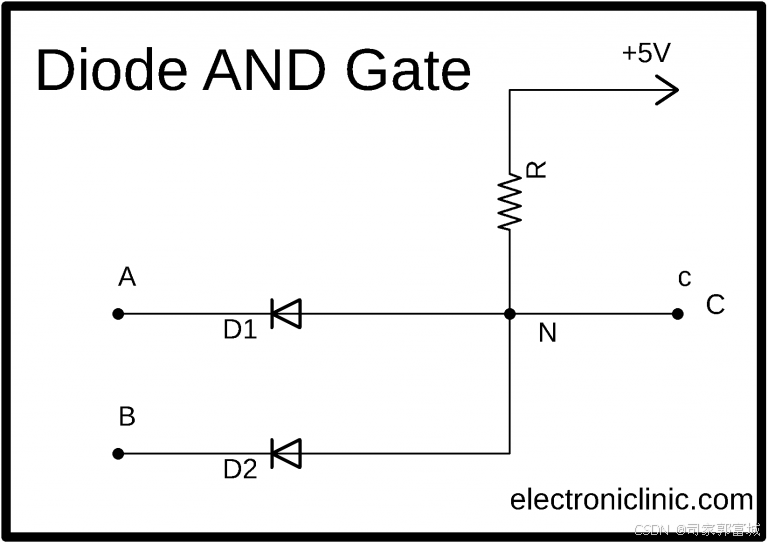

二极管与门

当输入A和B都为低电平时,两个二极管都正向偏置并导通,输出C端电压为低电平。如果输入A和B任意一个为低电平,相应的二极管正向偏置,在输出C处我们得到的仍然是低电平。

如果输入A和B都为高电平,两个二极管都反向偏置,输出C端电压为高电平。

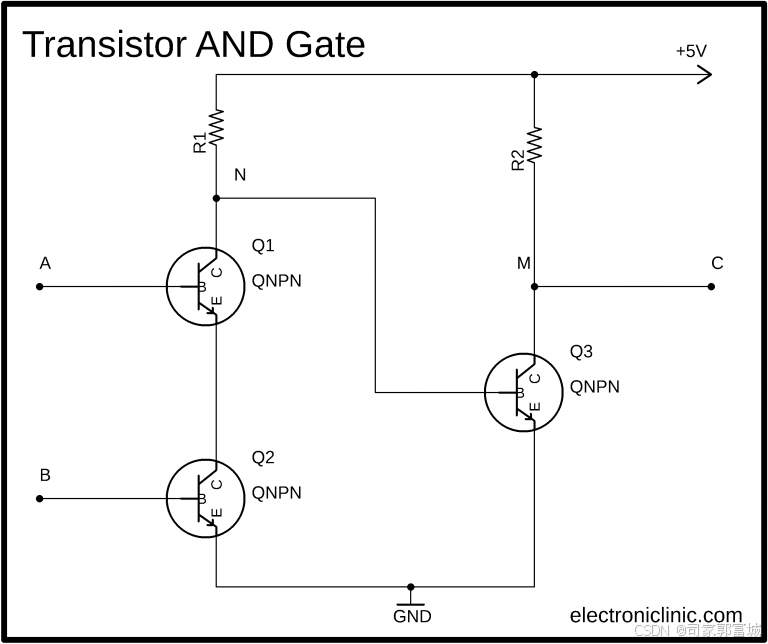

三极管与门

如果输入A和B都为低电平时,这样点N被拉到5V,晶体管Q3被导通,输出端C的电压为0V。如果输入A和B中的任何一个为低电平,输出端C的电压仍为0V。(不考虑三极管压降)

如果输入A和B都为高电平,即晶体管Q1和Q2都导通,点N处电压为0V,晶体管Q3关断,此时输出端C的电压为5V。(不考虑三极管压降)

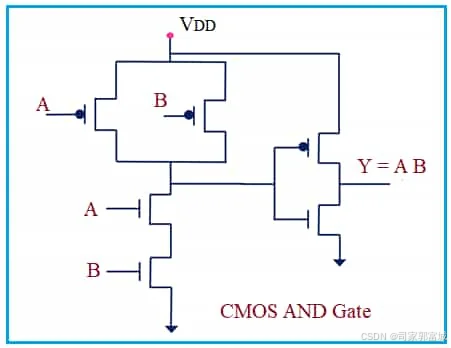

CMOS与门

如果输入A和B中的任何一个为低电平,PMOS晶体管导通,VDD被接到右侧CMOS反相器输入。此时PMOS截止,NMOS导通,Y输出被连接GND。

当所有输入都为高电平时,NMOS晶体管导通,GND被接到右侧CMOS反相器输入。此时PMOS导通,NMOS截至,Y输出被连接到VDD。

1.2 或门(OR gate)

1.2.1 逻辑运算规则

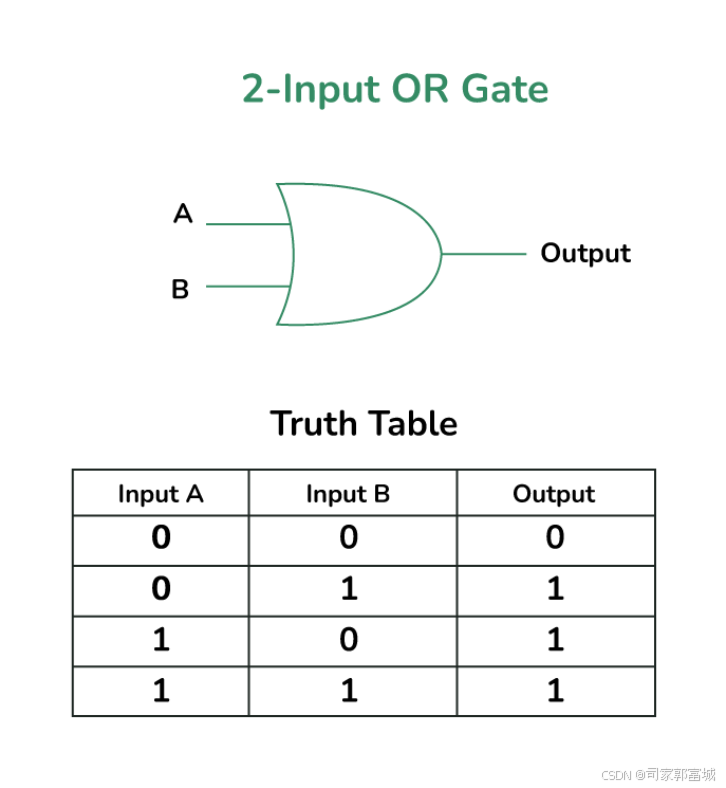

或门有多个输入端和一个输出端。只要输入中有一个为高电平时(逻辑“1”),输出就为高电平(逻辑“1”);只有当所有的输入全为低电平(逻辑“0”)时,输出才为低电平(逻辑“0”)。

1.2.2 逻辑符号及真值表

1.2.3 实现方式

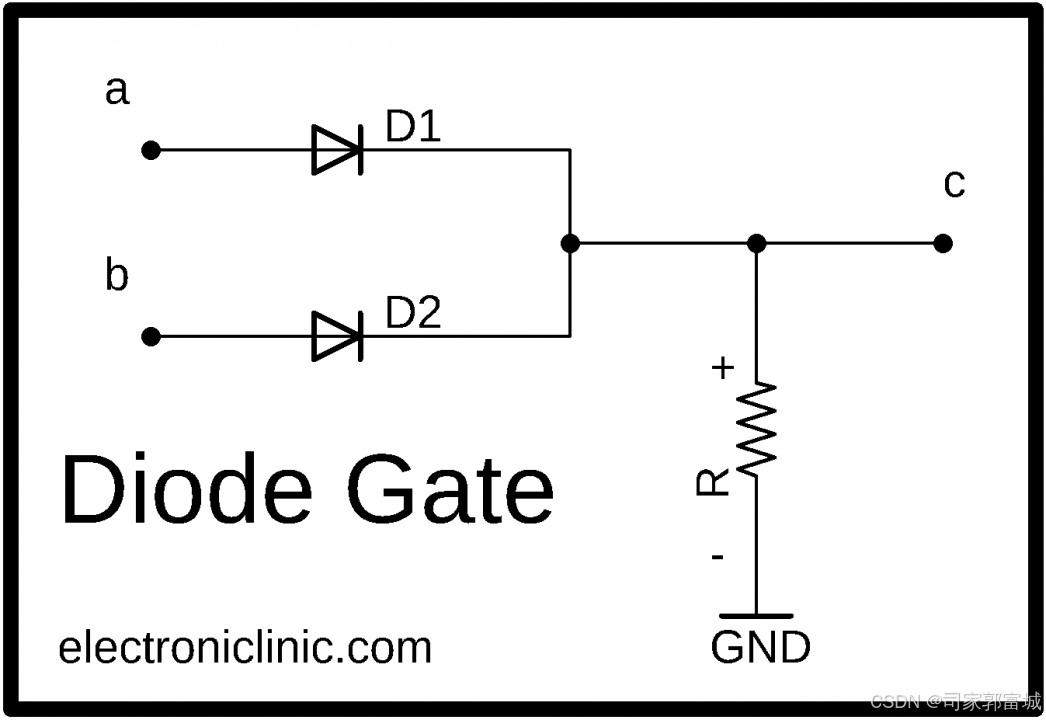

二极管或门

如果输入A和B都为高电平,二极管正向偏置并开始导通,输出C端电压为高电平。如果输入A和B中的任何一个为高电平,相应的二极管正向偏置,输出C端电压仍为高电平。

如果输入A和B都为高电平,二极管反向偏置,输出C端电压为低电平。

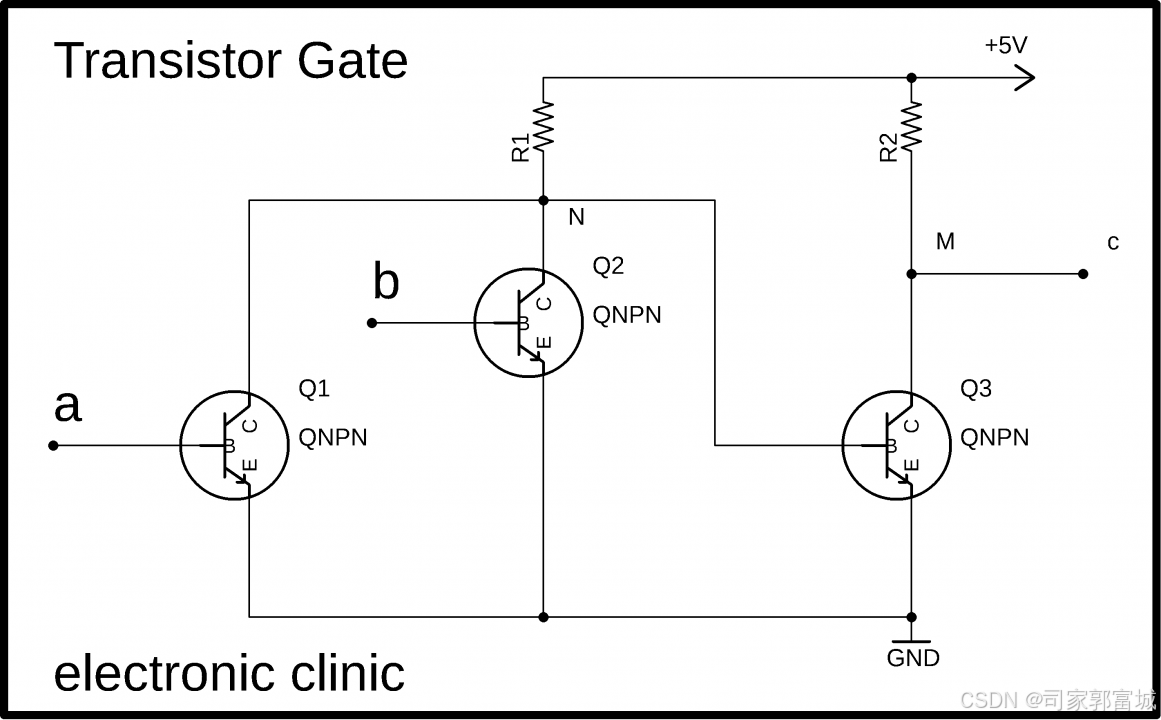

三极管或门

如果输入A和B都为高电平,晶体管Q1、Q2导通,晶体管Q3截止,输出C端电压为高电平。如果输入A和B中的任何一个为高电平,都会使晶体管Q3截止,输出C端电压仍为高电平。

如果输入A和B都为低电平,晶体管Q1和Q2处于截止状态,晶体管Q3导通,输出C端电压为低电平。

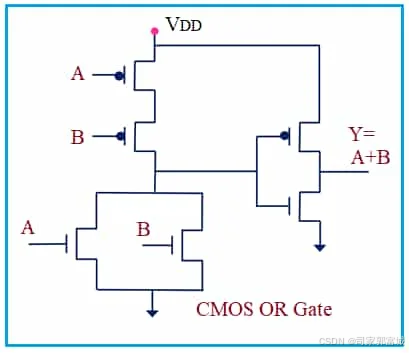

CMOS或门

如果输入A和B都为高电平,NMOS导通,PMOS截止,反相器的输入端为低电平。反相器的输入端的低电平将会导通PMOS,从而输出高电平。如