【FPGA】三八译码器——仿真验证

一、创建源文件

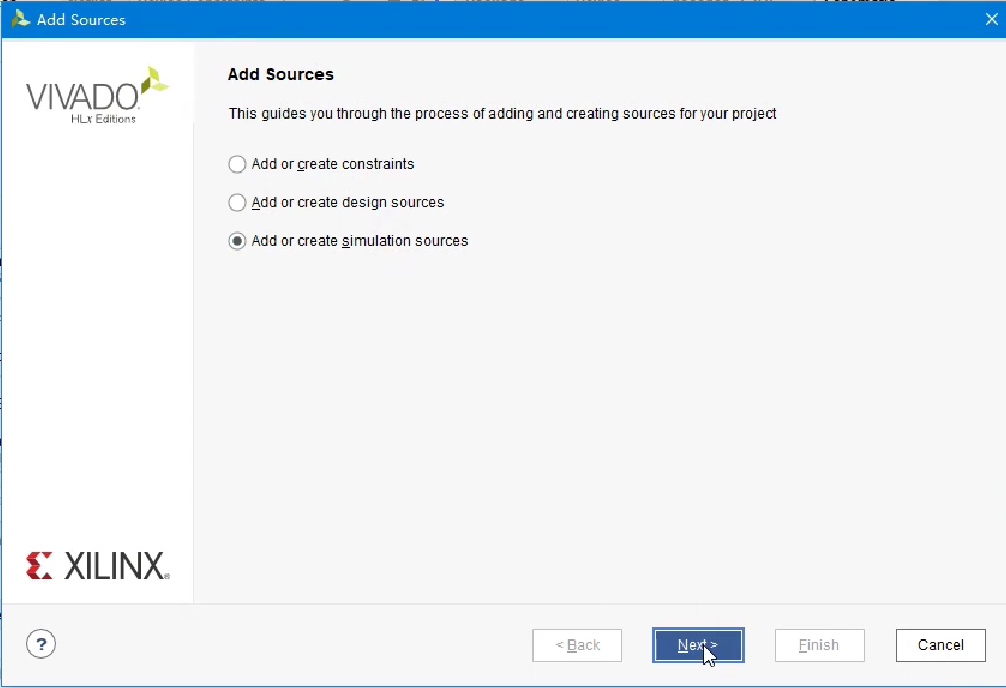

先创建一个仿真设计源文件

点击组合键Alt+A

选择第三个,点击Next

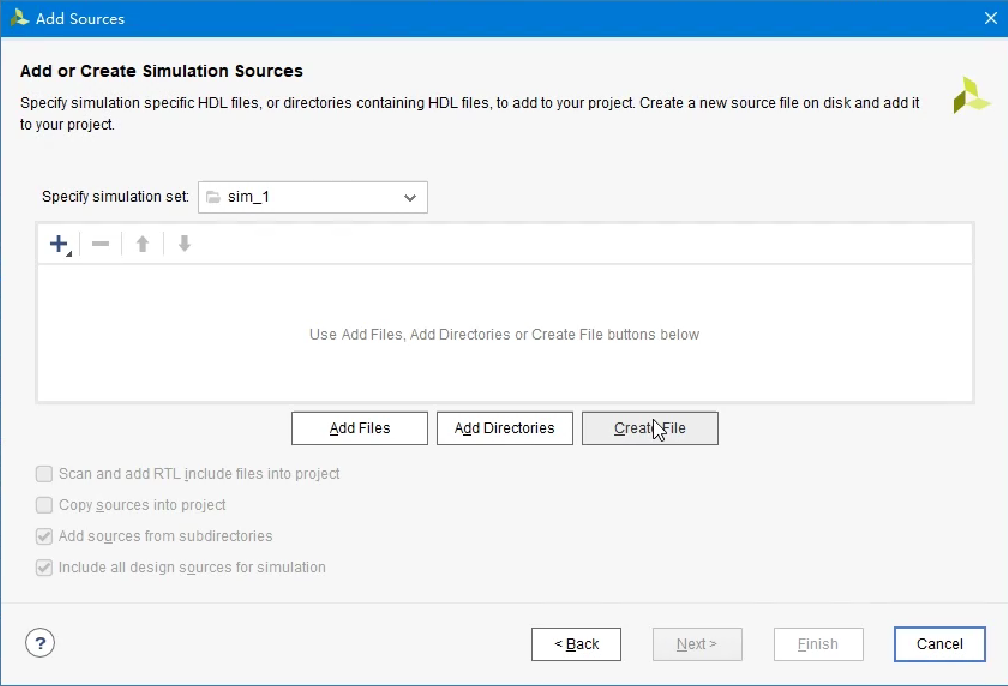

点击Create File

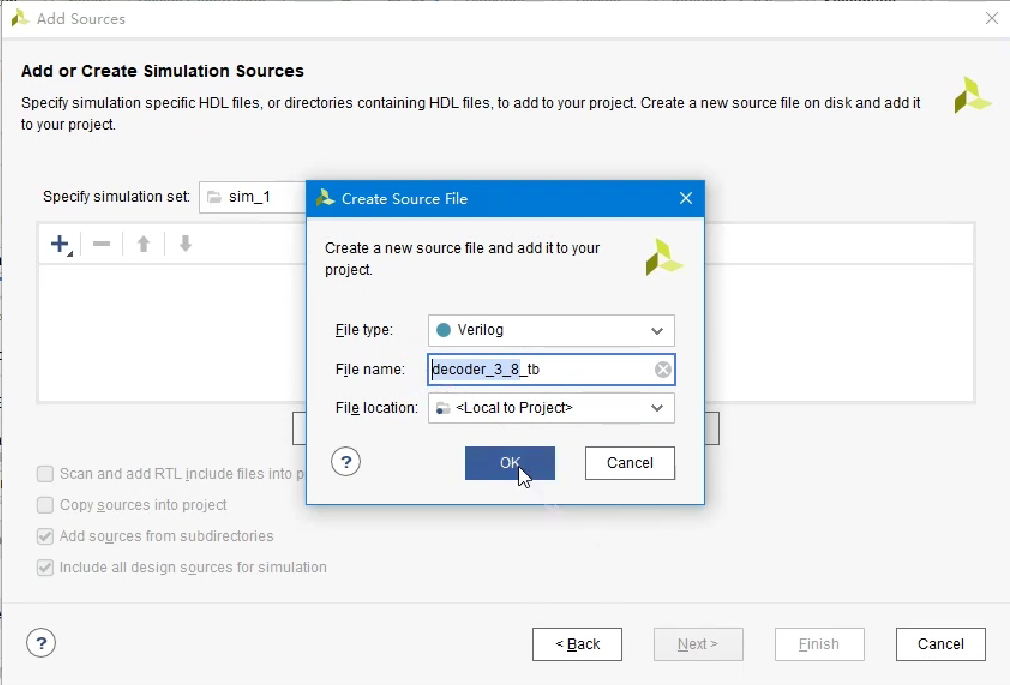

输入文件名称,点击OK,点击Finish

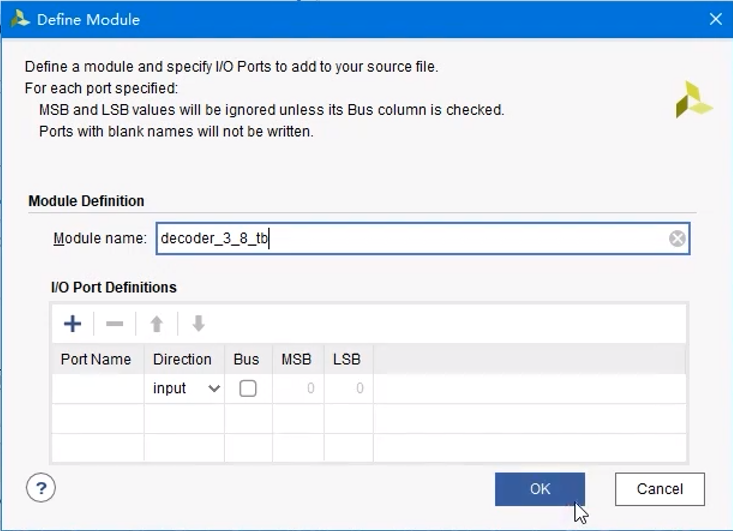

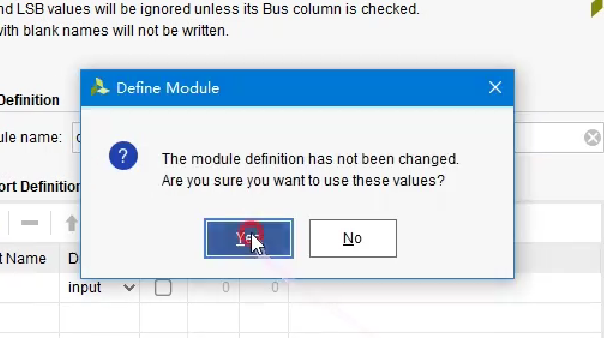

添加端口的界面仍选择OK,再点击Yes

二、程序编写

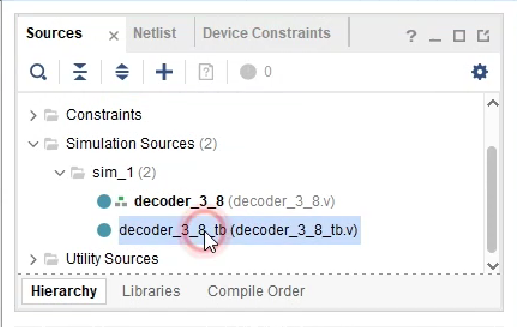

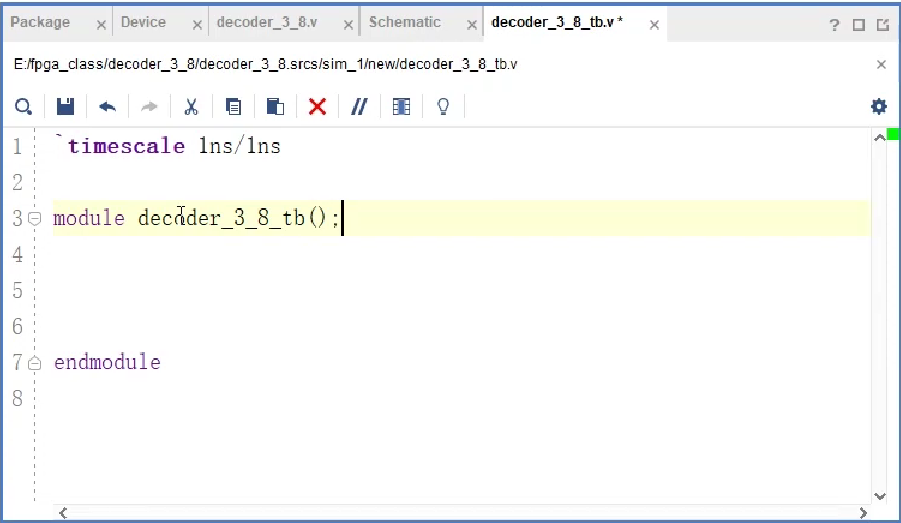

在Sources中找到刚才新建的文件,双击打开并删除其中的所有内容

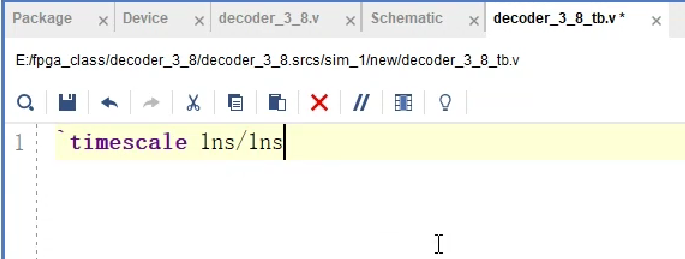

先书写仿真的时间单位语句

仿真时间步进单位/时间精度

声明Verilog模块

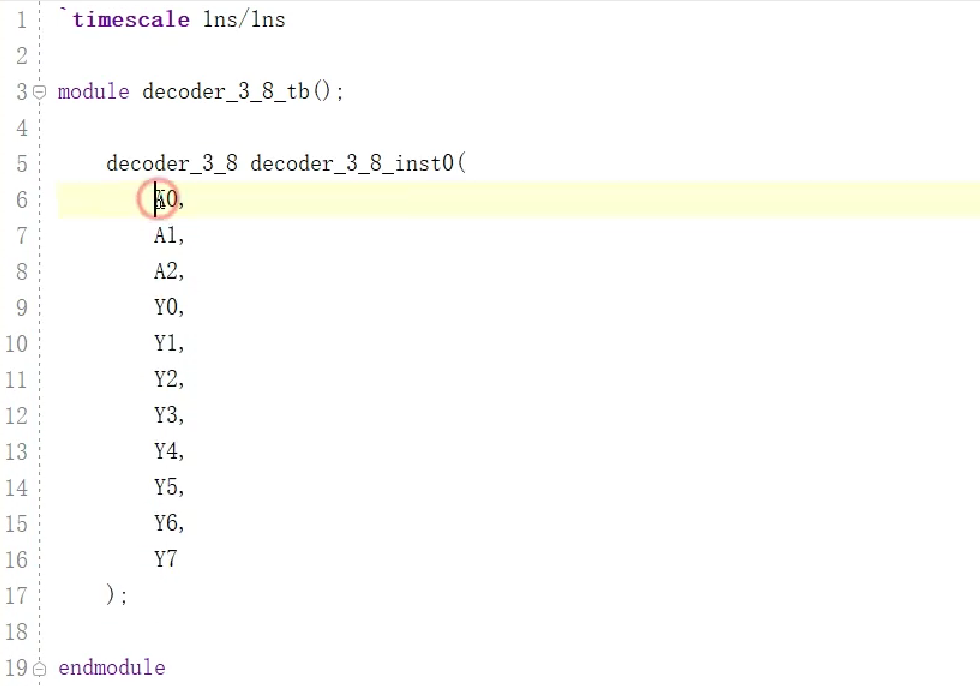

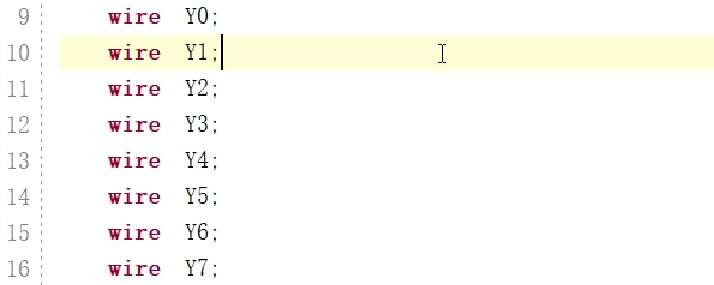

将被测试模块放到测试平台上,该过程称为例化

复制decoder_3_8模块的名称和端口列表,并添加标签

加.和()为例化做准备

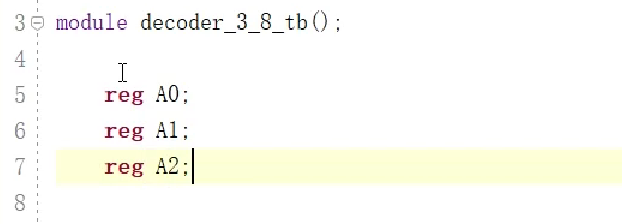

接下来进行连线,这里定义test bench中的激励信号名称和被测试模块的三个输入端口保持一致,都需要定义成reg型

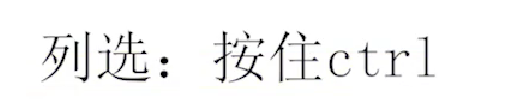

被测试的八个输出端口,需要连接到test bench中的八个wire型的信号上,方便仿真软件检测并显示值

同样定义和被测试模块的八个输出端口名称一样的八个信号

此时test bench中的激励信号和观测信号已经定义完毕

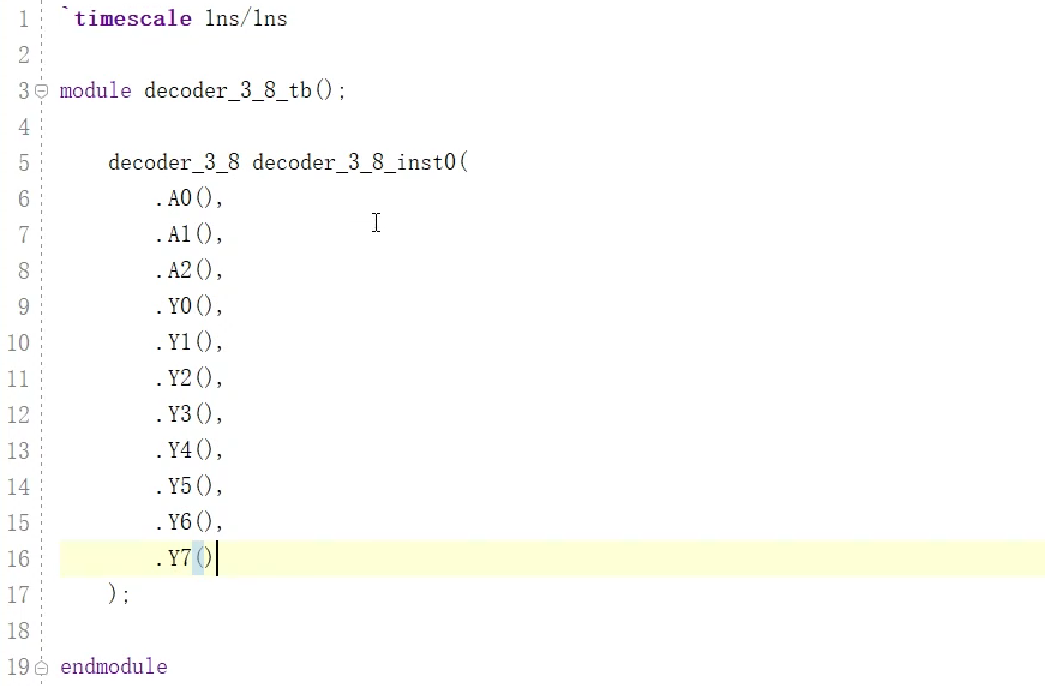

接下来需要将这些信号和被测试模块连接到一起,写到对应信号的括号内即可

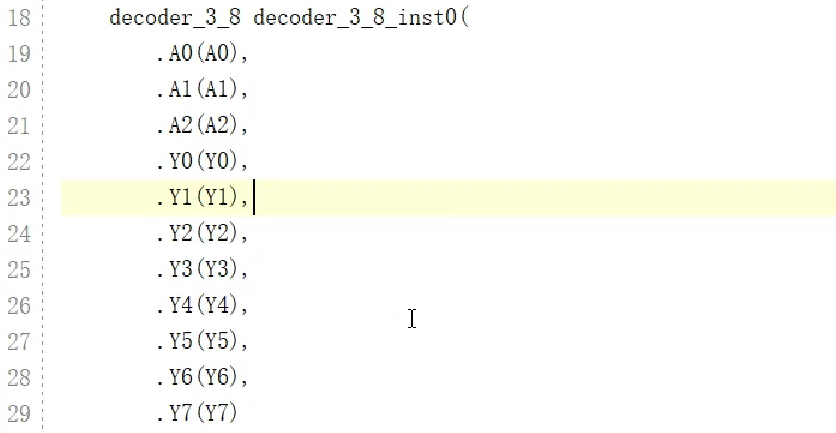

产生激励,让端口接收变化的信号,观察八个输出端口的输出情况

三个输入端口对应八种组合状态

分别产生每一种状态,观察Y0到Y7的输出电平

$ stop;是一个停止语句,避免仿真在所需要的内容产生之后仍不停的运行

Ctrl+S保存所写内容

使用test bench文件在仿真软件中进行仿真

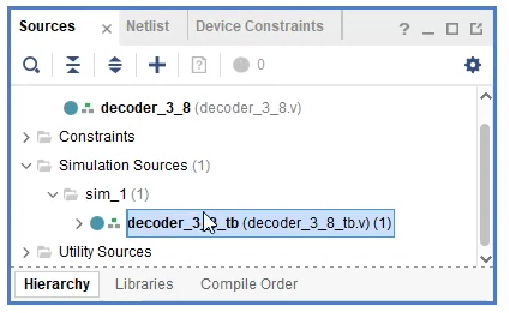

要确保品字形符号在仿真文件之前

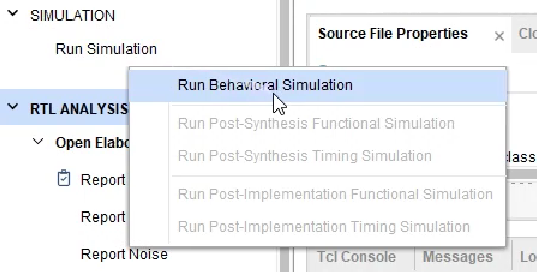

选择图中所示选项即可

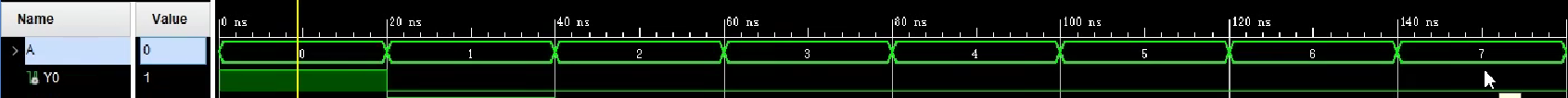

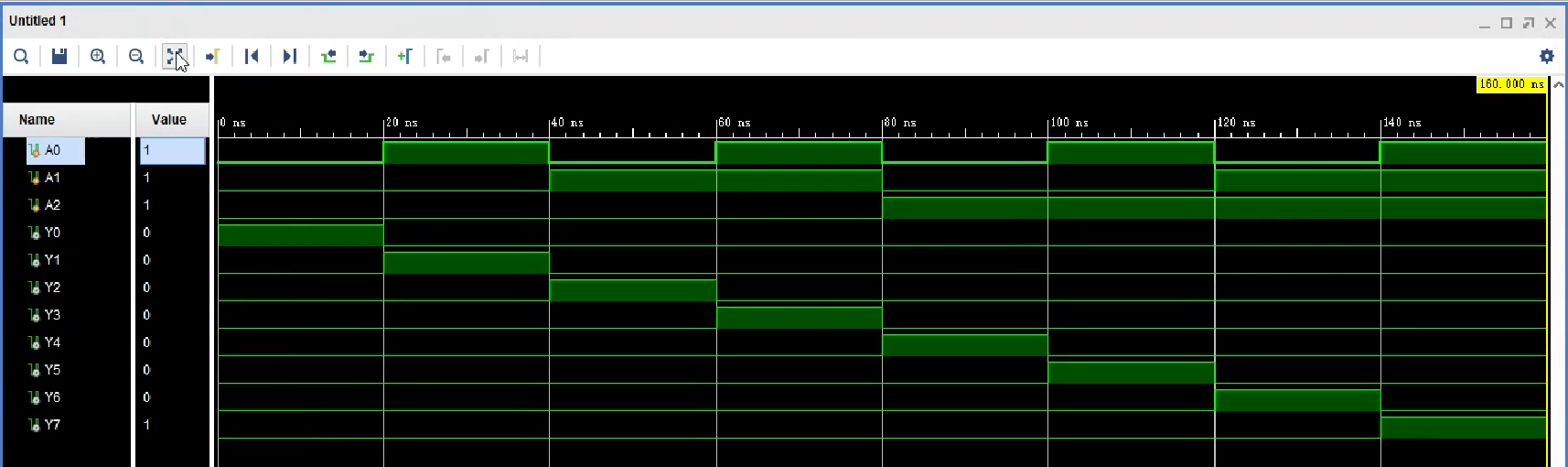

打开Untitled 1,并点击预览全局

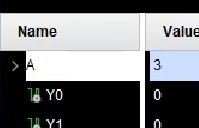

将三个数字组合到一起形成一个三位数以十进制的形式显示的方法:

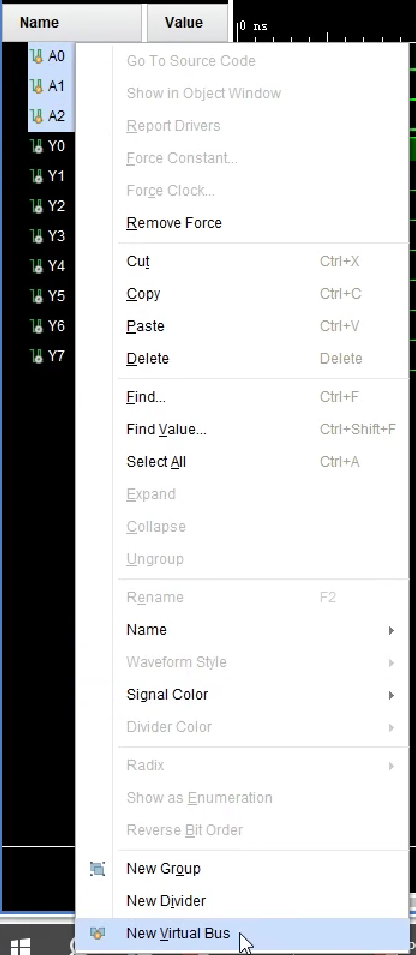

按住Ctrl键,选中索要组合到一起的三个信号,点击New Virtual Bus(新虚拟总线)

在图示位置起一个名字,回车

就可以达到上述效果