实验三:3-8线译码器设计

一、实验目的

1. 掌握译码器的设计方法。

2.掌握隧道的使用方法

二、实验环境

Logisim 2.16

三、实验内容

- 译码器实验

74HC138:输入引脚A,B,C.控制引脚线:G1,G2A_L,G2B_L,电路工作时,G1=1,G2A_L=G2B_L=0,这三条控制线通过一个门电路构成译码器的使能引脚线EN。

如果输出高电平有效,一般情况下EN=1;如果输出低电平有效,EN=0.

设计译码电路前,需要列出译码器的真值表,求出输出与输入的最简与或逻辑表达式,再画图。译码器输出高有效或低有效,自行决定。

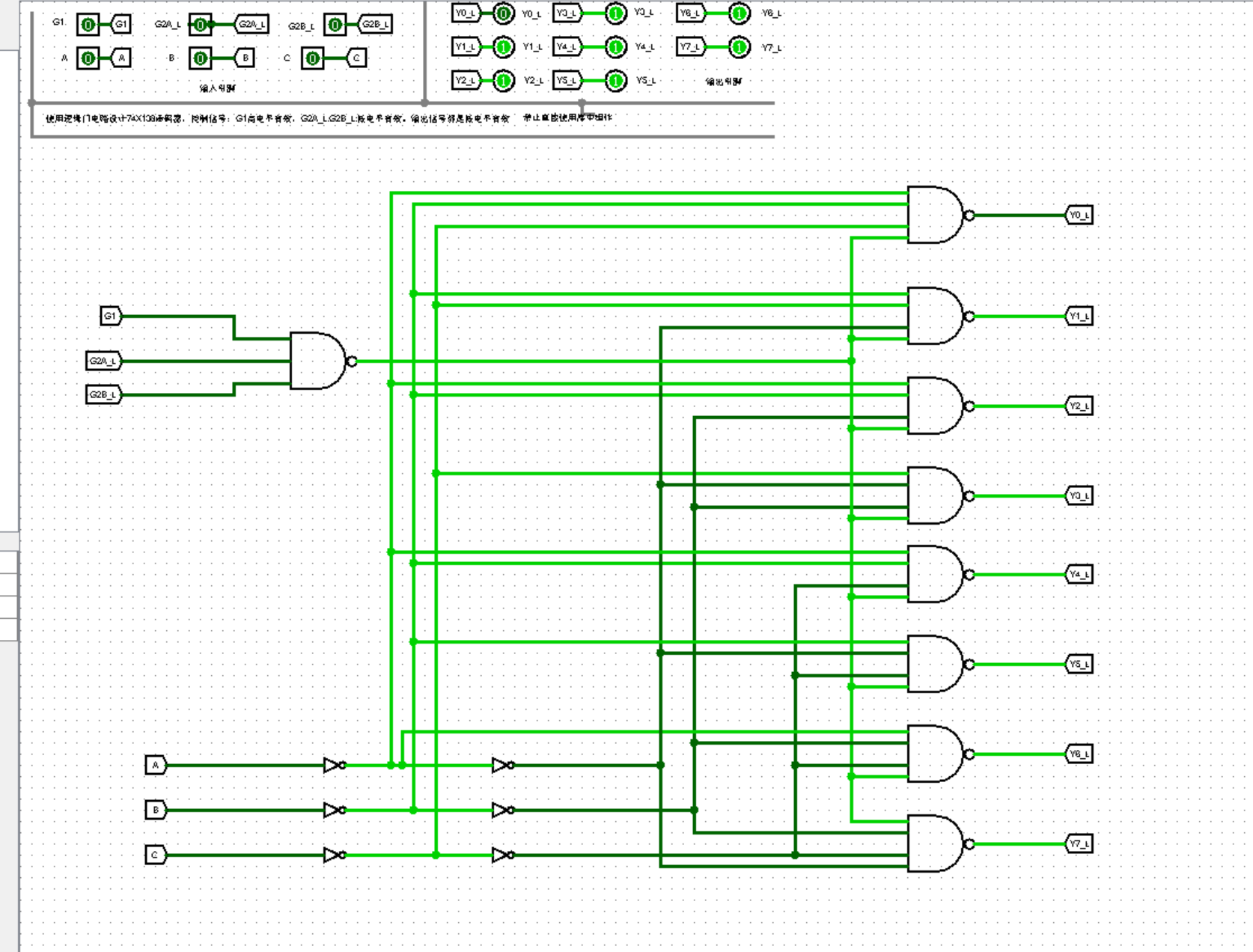

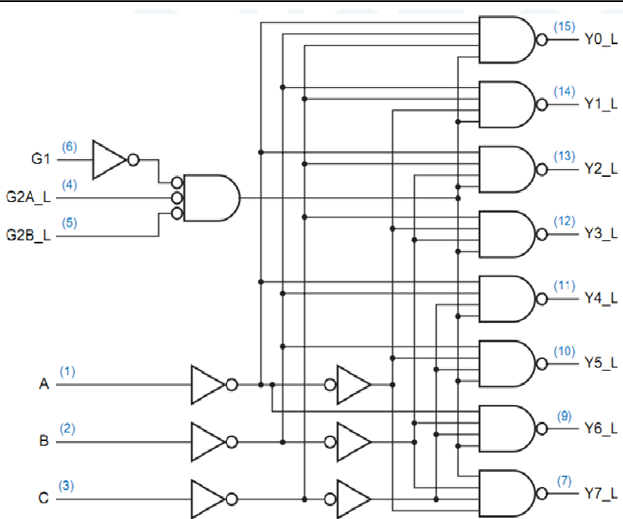

图1是 3-8 译码器芯片 74HC138 的电路原理参考图,输出低电平有效,设计一个由反相逻辑门电路构成的 3-8 译码器,并对电路进行仿真测试,以验证电路的功能。

图 1 3-8 译码器 74X138 原理图

实验步骤参考如下:

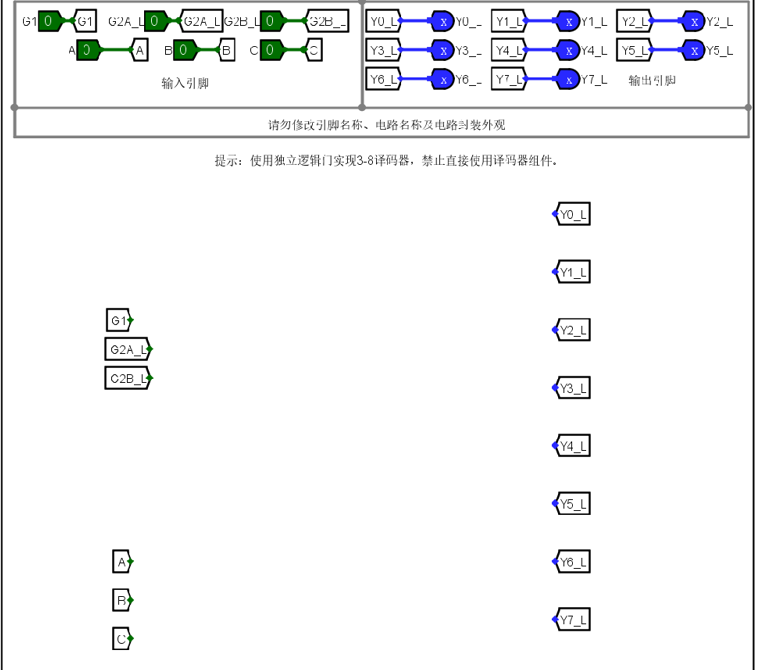

1) 根据图 1 所示布局图添加逻辑门。打开 Logisim,选择 8 个 4 输入与非门、7 个非门、1 个与门、7 个输入引脚、8 个输出引脚,并将上述元件布局到 Logisim 的工作区中适当位置。可通过以下方式设置输入端口数:以与非门为例,选择某个与非门,在属性窗口的输入端口数输入框中设置数字 4。

图 2 3-8 译码器布局图

- 添加连线。将输入引脚、逻辑门的输入端、输出端、输出引脚等通过连接线相连。

3) 添加标识符。选中输入/输出引脚,在属性表中添加引脚标识符;选中逻辑门,在属性表中添加逻辑门标识符;点击快捷工具栏中的文本工具,在电路空白处添加电路的描述文字。标识符、注释文字的字体、大小、颜色和位置等均可在属性表中修改。

4) 仿真测试。进入仿真状态,改变输入引脚赋值,记录输出引脚值,填写表 2.1 所示的译码器功能表以验证实验结果。保存电路,文件名为 *.circ。

0表 2.1 74X138 功能表(真值表)

| 输入 | 输出 | ||||||||||||

| G1 | G2A_L | G2B_L | A | B | C | Y0_L | Y1_L | Y2_L | Y3_L | Y4_L | Y5_L | Y6_L | Y7_L |

| X | 1 | X | X | X | X | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| X | X | 1 | X | X | X | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0 | X | X | X | X | X | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

当控制信号线G1=1,

当控制信号线G1=1,G2A_L=0,G2B_L=0时,译码器工作(Y(0-7)_L:低电平有效)

11:接电源(+nV)。

00:接地(GND)