Marin说PCB之SI----做信号完整性仿真时需要注意的地方--03

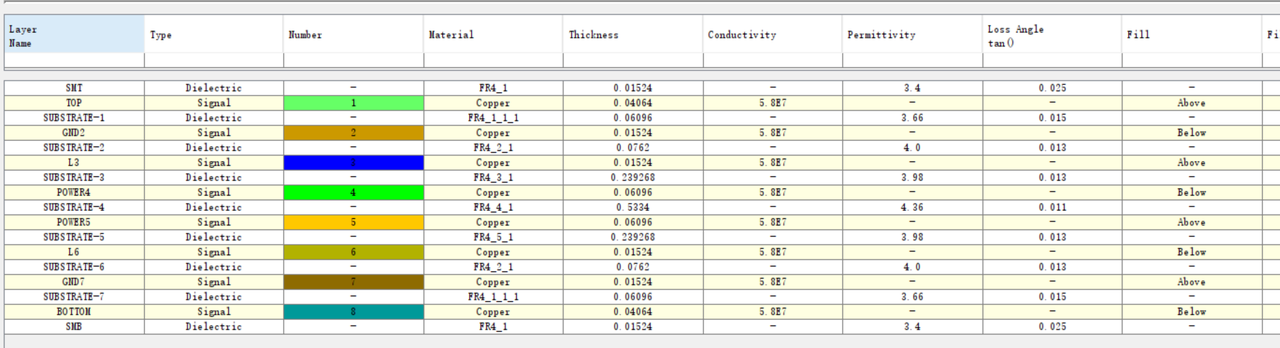

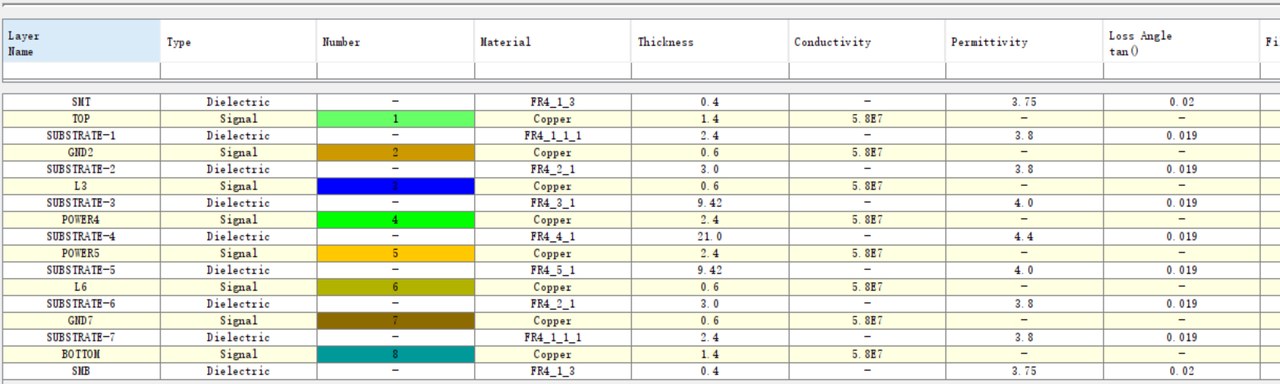

一,首先我们先去对比一下层叠信息:

(之前的Stackup)

(最新的Stackup )

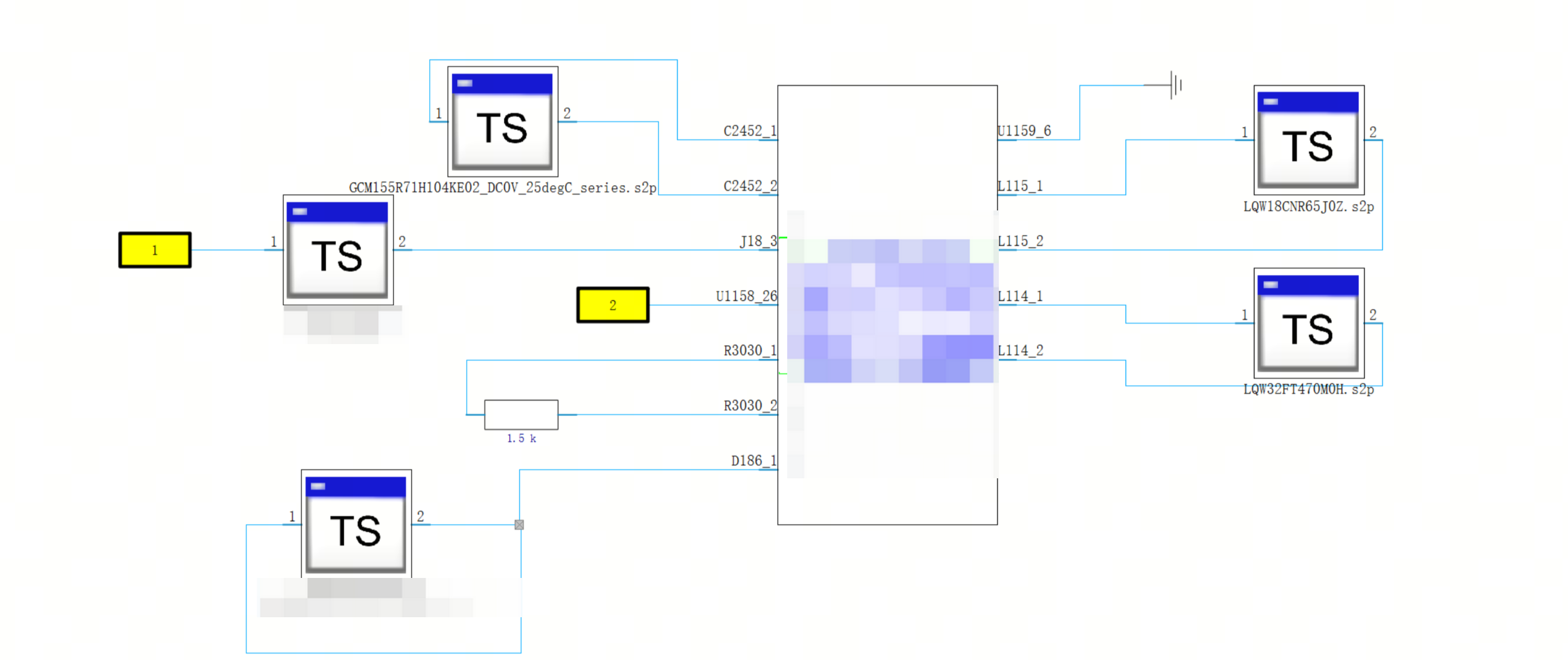

二,导入数据到仿真软件中去观察其S参数的性能:

A,找到一个 GMSL2网络RX0_96712_FAKRA_1,搭建好仿真原理图,如下所示:

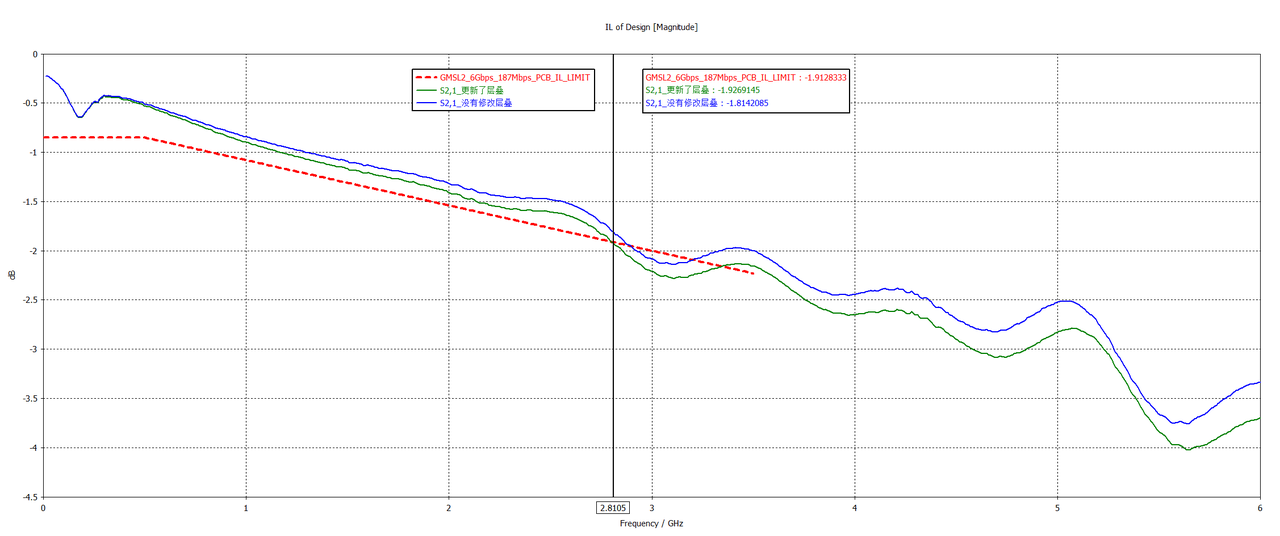

B,IL的结果如下所示:

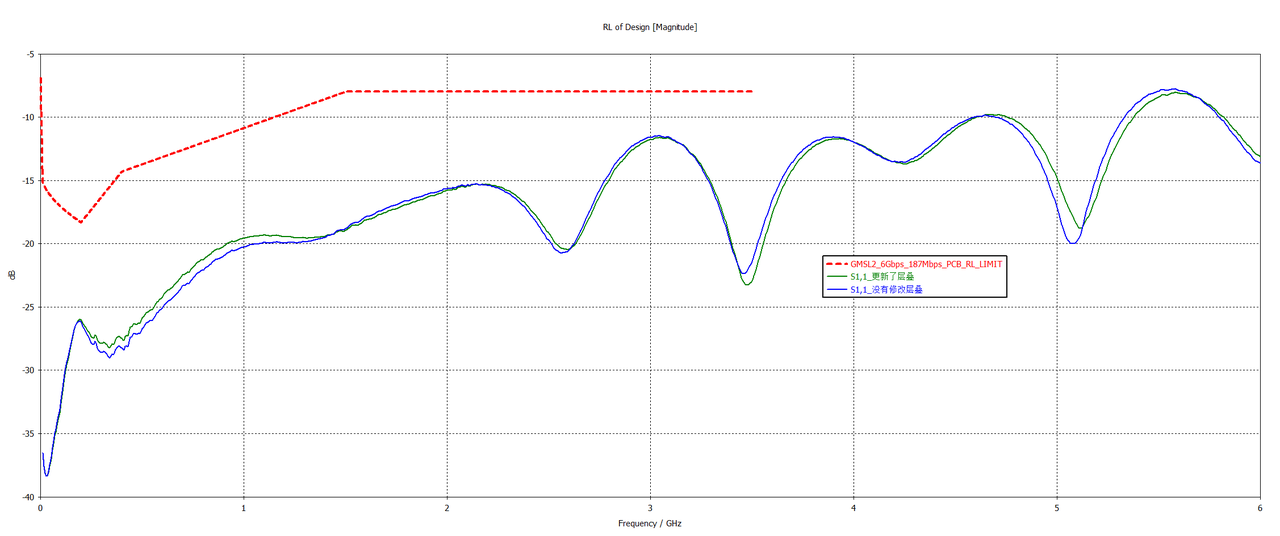

C,RL的结果如下所示:

仿真结果分析:DF值其实主要影响的是信号的IL的数值,尤其是对高频段影响还是挺多的,原因是较高的损耗角正切会增加介电损耗,从而衰减高频信号。

三,正常来说制板厂将板材的Df和Dk值调大,会对我们的PCB设计产生直接的负面影响,

A,Df (损耗角正切) 增大:直接导致介电损耗增加。这是高速链路中插入损耗的主要来源之一。其结果可能是:

信号衰减加剧:导致眼图闭合,信号幅度降低。

传输距离缩短:可能使您的设计无法达到最远的传输距离。

比特误码率上升:系统稳定性下降。

B,Dk (介电常数) 增大:

影响阻抗控制:根据传输线模型,特性阻抗与Dk的平方根成反比。Dk增大,会导致实际阻抗低于设计值,引起阻抗不连续和反射。

信号速率降低:信号传播速度与Dk的平方根成反比。

时序可能偏移:对于并行总线,Dk的变化可能导致skew增加。

了,诸位道友们以上就是本期的所有内容了,我们下期文章不见不散。

--------声明:本文属于小编的原创文章,如需转载请注明来源!