泰州模板自助建站华为应用商店下载

一、 本章概括

在之前的章节已经详细介绍了DDR4的AXI协议,并实现了对DDR4简单的读写操作。这一章节来建立单通道的256位数据的读写,并放出工程框架,说明整体设计思路。

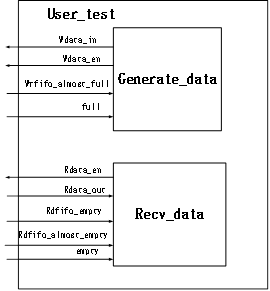

二、 工程框架

三、 设计思路

DDR内存通常用于大容量数据存储,但延迟较高,并且axi接口协议需要较多的接口。而fifo是先进先出的队列,用于缓冲数据。我们利用AXI接口的高带宽和DDR4的大容量,来实现一个高效的fifo系统,这样可以更方便使用DDR来读写数据。

(一)、首先要考虑时钟域的问题,如果用户接口和DDR4接口时钟不同,需要用到异步fifo来进行跨时钟域操作:

用两个fifo连接ddr:首先由generate_data模块产生数据,把数据存入fifo_1中,再通过wr_ddr_start(写ddr开始信号)控制ddr把fifo_1中的数据写进ddr。再通过rd_ddr_start(读ddr开始信号)控制ddr读取ddr中的数据写进fifo_2中,由recv_data模块接收数据。如果fifo_1不满的话,就可以写入数据。如果fifo_2不空的话,就可以读出数据。

(二)、对于DDR4与FIFO的数据交互:如果fifo_1不空并且ddr不满的话,就往ddr中写入fifo_1中的数据。如果fifo_2不满并且ddr不空的话,就从ddr中读出数据存到fifo_2中。

(三)、注意事项

在将fifo_1中的数据写入DDR4时,需要控制向DDR4写入的长度和地址,DDR4每次写突发最长可以写进256个数据,为了能更高效的使用DDR4,每次突发时,初始地址必须紧跟上一次突发后写入最后一个数据的地址。并且最终地址不能超过DDR4的总内存地址。

在将DDR4中的数据读出后写入fifo_2时,需要控制从DDR4读取的长度和地址,DDR4每次读突发最长可以读出256个数据,之前将数据写进DDR4时,前一次突发和后一次突发的地址是相连的,所以每次读突发时,初始地址必须紧跟上一次突发后读出最后一个数据的地址。并且最终地址不能超过DDR4的总内存地址。

四、 ddr3_axi_wr_ctrl模块实现ddr3写数据

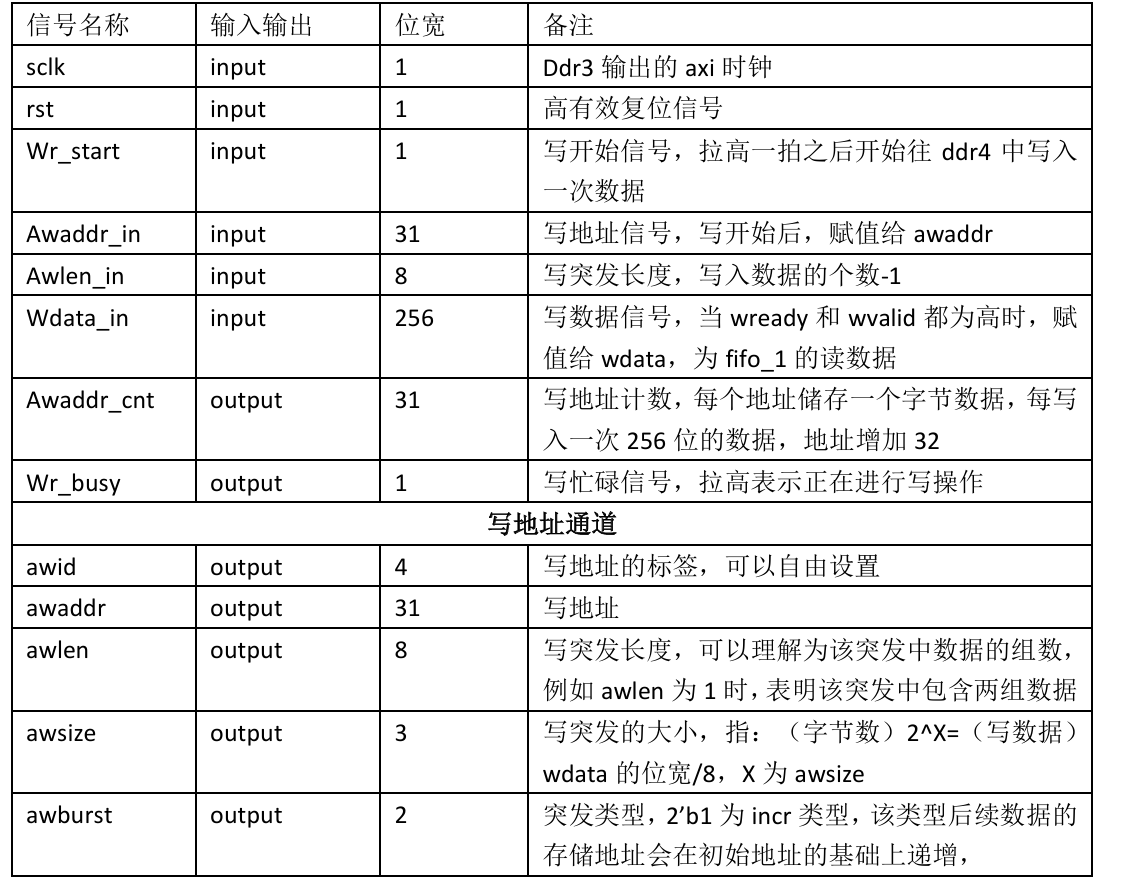

(1)、ddr3_axi_wr_ctrl模块接口列表:

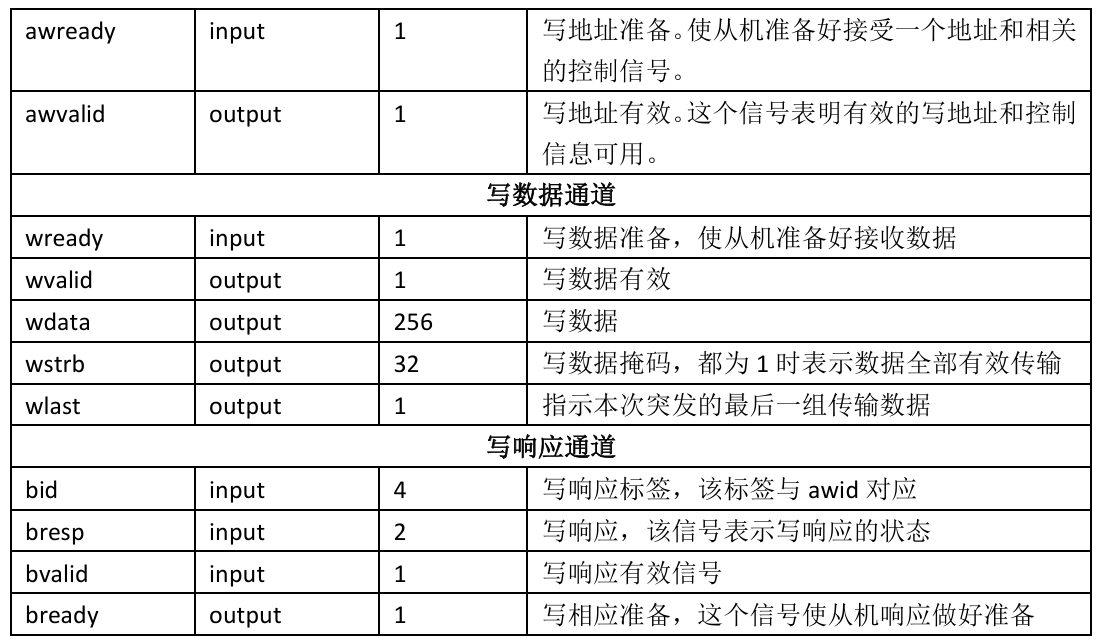

(2)、ddr3写模块关键时序:图53(黄色为输入信号,绿色为输出信号)

(3)、时序图解析:

写开始信号(wr_start)拉高后,状态跳转到发送地址(SEND_ADDR)状态,并且把写地址和写数据长度信号赋值给awaddr和awlen。在SEND_ADDR状态下拉高awvalid信号。

当awready信号和awvalid信号同时为高,说明写地址已经成功发送,这时拉低awvalid信号。跳转到发送数据状态(SEND_DATA)。

在SEND_DATA状态下拉高wvalid,这时写数据(wdata)在wvalid和wready同时为高时有效。每发送一次数据,地址计数(awaddr_cnt)+32。在发送最后一拍数据时拉高wlast信号,表明当前发送的是最后一拍数据。状态跳转到接收响应状态(RECV_BVALID)。

当bvalid信号为高时,表示已经成功写进数据,状态返回到ILDE。

写忙碌信号在写开始信号拉高之后拉高,接收到bvalid信号之后拉低。bvalid信号可以用作写结束信号。

五、 ddr3_axi_rd_ctrl模块实现ddr3读数据

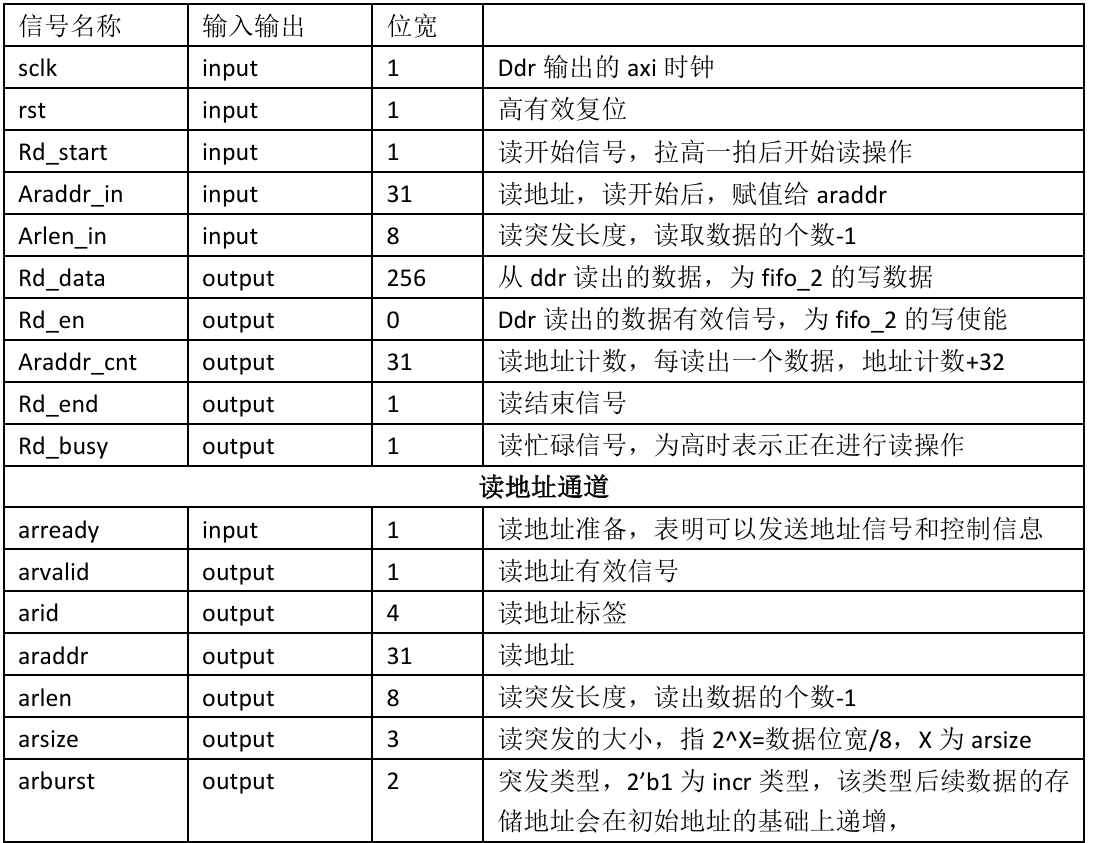

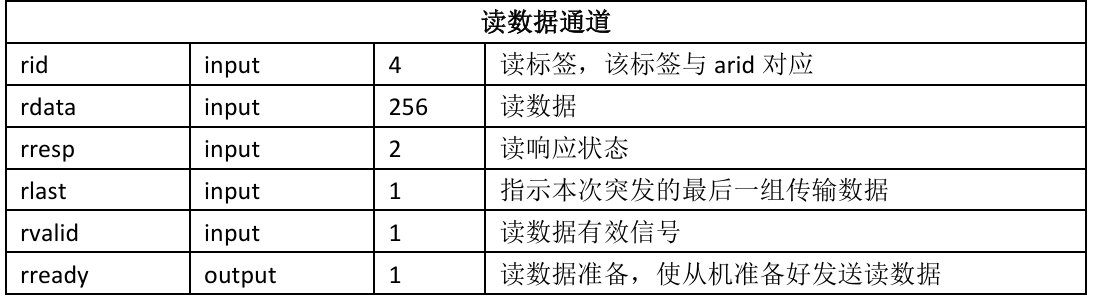

(1)、ddr3_axi_rd_ctrl模块接口列表:

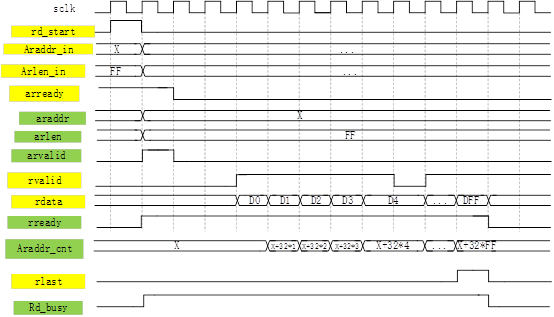

(2)、ddr4_axi_rd_ctrl模块关键时序:图54(黄色为输入信号,绿色为输出信号)

(3)、时序图解析:

当读开始信号拉高后,把读地址(araddr_in)和读数据长度(arlen_in)赋值给araddr和arlen,并且拉高arvalid信号、读数据准备信号(rready)和读忙碌(rd_busy),arvalid信号在arready为高时拉低。读数据准备信号(rready)和读忙碌(rd_busy)在rlast拉高后拉低。

每读出一个数据,读地址计数(araddr_cnt)+32。读出的数据做为fifo_2的写数据。

六、 本章总结

本章节概括了整体设计思路,并给出了读写DDR4内存的接口列表和重点时序图。对于对DDR4的读写的开始、长度、地址等控制信号,由仲裁模块(arbit)和数据交互模块(data_in_out)给出。我们在下一章节详细说明。

本文章由威三学社出品

对课程感兴趣可以私信联系