【读书笔记·VLSI电路设计方法解密】问题56:一种设计的门数是多少

“门数”(gate count)这一术语用于衡量数字设计的规模。在数字设计的网表中,包含许多电路元件或基本单元(叶单元)。这些电路元件可能是来自ASIC库的标准单元、存储器或特殊的宏单元。在ASIC库中,不同的单元具有不同的物理尺寸。存储器和宏单元也有其独特的物理尺寸。网表的规模,或者说设计的规模,是其所有组成元件尺寸的总和。为了方便描述数字设计的规模,库单元、存储器单元和宏单元的物理尺寸会被归一化到一个基础单元,通常是一个具有最小1倍驱动能力的两输入NAND门(这里称为NAND2)。因此,任何网表的规模都是通过参考这个基础单元的尺寸来衡量的。门数是对网表中包含的等效基础单元数量的估计。例如,如果一个设计被称为“10万门设计”,其物理尺寸相当于10万个NAND2单元的尺寸。

不要将门数与元件数量混淆。在前面的例子中,设计中实际元件的数量不一定是10万,因为不同单元的尺寸不同。此外,该设计的最终实际布局尺寸也不能简单地通过将NAND2的尺寸乘以10万倍来确定。这是因为还需要额外的空间用于电源网络、I/O总线、时钟树和布线通道。换句话说,门数只是一个估计值,用于方便地比较不同设计的相对规模。

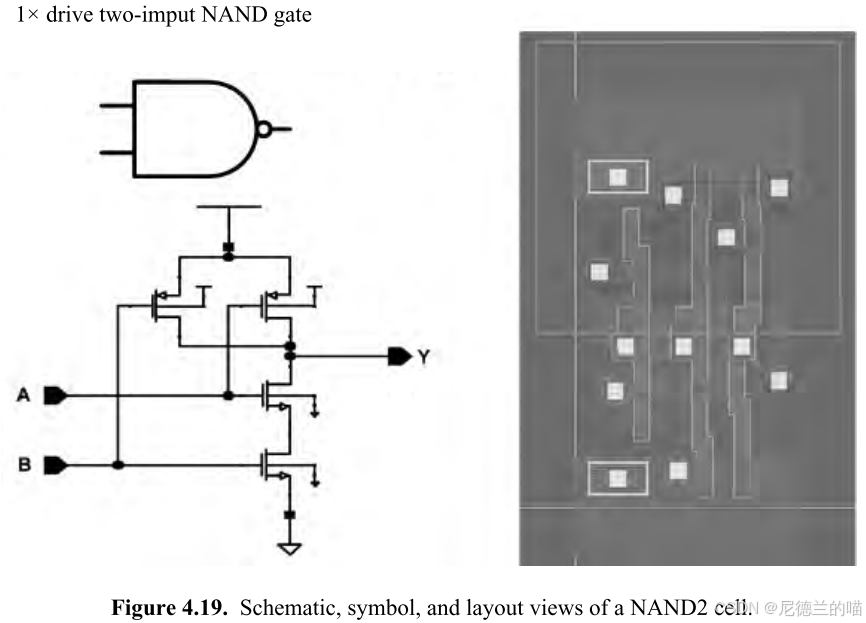

图4.19展示了来自ASIC库的NAND2单元的电路图、符号和布局视图。