STM32HAL 快速入门(十七):UART 硬件结构 —— 从寄存器到数据收发流程

前言

大家好,这里是 Hello_Embed。上一篇我们理解了 UART 协议的底层逻辑(数据格式、波特率等),本篇将深入 STM32F103 芯片的 UART 硬件结构 —— 解析核心寄存器(如控制寄存器、状态寄存器)的作用,以及数据 “发送” 和 “接收” 的硬件流程,同时介绍如何通过中断替代查询方式,提升通信效率。这些硬件细节是下一篇 UART 编程的基础,务必理清每个环节的逻辑。

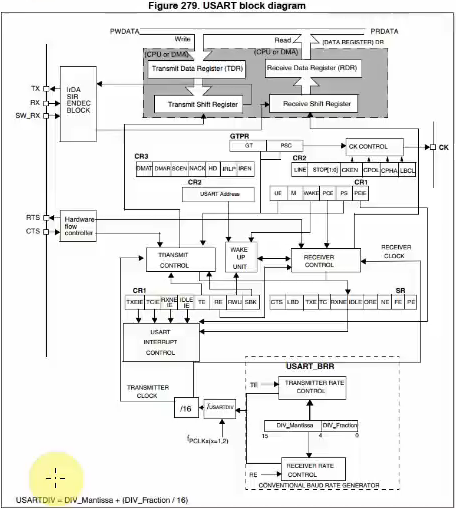

一、UART 硬件整体框架

STM32F103 的 UART(实际为 USART,通用同步异步收发器,兼容 UART 功能)硬件结构可概括为 “控制模块 + 数据缓冲模块 + 移位传输模块”,核心是通过寄存器配置和状态判断,实现数据的串行收发。整体硬件示意图如下:

接下来我们按 “配置→发送→接收→中断控制” 的顺序,拆解每个模块的作用。

二、UART 硬件配置:核心控制寄存器

要让 UART 工作,首先需通过控制寄存器配置通信参数(如使能 USART、数据位长度、校验位等),核心寄存器为CR1、CR2、CR3。

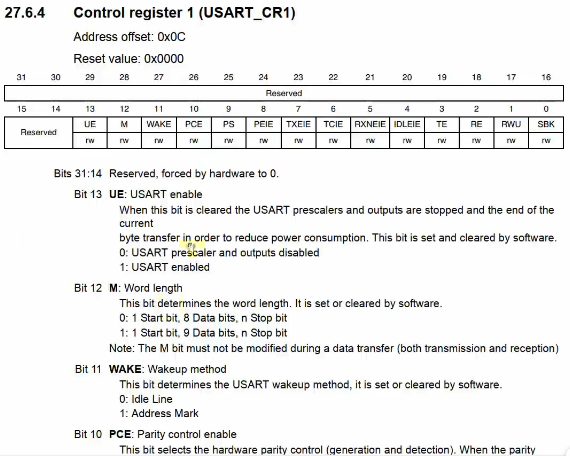

1. 主控制寄存器 CR1

CR1 寄存器是 UART 配置的核心,关键位功能如下:

- Bit13(UE):USART 使能位 —— 写 1 时开启 UART 功能,写 0 时关闭;

- Bit12(M):数据位长度选择 ——0 表示 8 位数据,1 表示 9 位数据(常用 8 位);

- Bit10(PCE):校验位使能位 ——0 关闭校验,1 开启校验;

- Bit9(PS):校验类型选择 ——0 表示偶校验,1 表示奇校验;

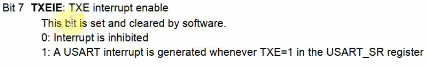

- Bit7(TXEIE):发送数据寄存器空中断使能 ——1 时,当 TDR(发送数据寄存器)为空,触发中断;

- Bit5(RXNEIE):接收数据寄存器非空中断使能 ——1 时,当 RDR(接收数据寄存器)有数据,触发中断。

2. 辅助控制寄存器 CR2、CR3

- CR2:主要配置停止位长度 —— 可选择 1 位、1.5 位或 2 位停止位(Bit13~Bit12 控制);

- CR3:配置硬件流控(如 RTS/CTS)—— 若无需流控,默认配置为 0 即可。

三、数据发送流程:从寄存器到 TX 引脚

UART 发送数据的硬件路径为:CPU 写入数据→TDR 寄存器→移位寄存器→TX 引脚串行发送,需通过状态寄存器判断发送进度。

1. 发送流程细节

- 写入数据到 TDR:CPU 通过指针操作将数据写入 TDR 寄存器,示例代码(直接操作寄存器):

unsigned int *p = (unsigned int *)0x40013804; // TDR寄存器地址(以USART1为例)

*p = 0x78; // 将数据0x78写入TDR

- TDR 到移位寄存器:硬件自动将 TDR 中的数据转移到 “发送移位寄存器”;

- 移位发送到 TX 引脚:移位寄存器将并行数据(如 8 位)按 “起始位→数据位→校验位→停止位” 的顺序,逐位通过 TX 引脚串行发送出去。

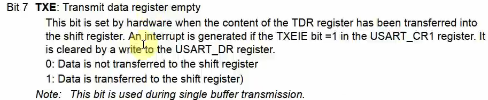

2. 发送状态判断:状态寄存器 SR

发送过程中,需通过USART_SR(状态寄存器) 判断是否可继续发送数据,关键位:

- Bit7(TXE):发送数据寄存器空 ——1 表示 TDR 中的数据已转移到移位寄存器,TDR 为空,可写入下一个数据;

- Bit6(TC):发送完成 ——1 表示移位寄存器中的数据已全部通过 TX 引脚发送,整个发送过程完成。

注意:写数据时,需先判断 SR 的 Bit7(TXE)是否为 1,确保 TDR 为空后再写入,避免数据覆盖。

四、数据接收流程:从 RX 引脚到寄存器

UART 接收数据的硬件路径为:RX 引脚串行接收→接收移位寄存器→RDR 寄存器→CPU 读取数据,同样需通过状态寄存器判断接收状态。

1. 接收流程细节

- RX 引脚接收数据:外部设备(如电脑)通过 RX 引脚向 UART 发送串行数据;

- 移位寄存器串转并:“接收移位寄存器” 将串行数据(逐位接收)转换为并行数据(如 8 位);

- 转移到 RDR 寄存器:硬件自动将并行数据转移到 RDR 寄存器,等待 CPU 读取;

- CPU 读取 RDR 数据:CPU 通过指针操作读取 RDR 中的数据,示例代码:

unsigned int *p = (unsigned int *)0x40013804; // RDR与TDR地址相同,读操作时访问RDR

uint8_t val = *p; // 读取RDR中的数据到val

2. 接收状态判断:状态寄存器 SR

接收过程中,关键状态位为SR 的 Bit5(RXNE):

- Bit5(RXNE):接收数据寄存器非空 ——1 表示 RDR 中有新数据,CPU 可读取;0 表示 RDR 为空,无数据可读。

注意:读数据时,需先判断 SR 的 Bit5(RXNE)是否为 1,确保有数据后再读取,避免读取无效值。

3. 读写操作的特殊点

TDR 和 RDR 共享同一个地址(如 USART1 的 TDR/RDR 地址为 0x40013804):

- 写操作:访问该地址时,操作的是 TDR 寄存器(发送数据);

- 读操作:访问该地址时,操作的是 RDR 寄存器(接收数据)—— 硬件自动区分读写方向。

四、中断控制:替代查询,提升效率

前面提到的 “判断 SR 寄存器状态” 属于 “查询方式”——CPU 需不断轮询状态位,占用资源。而中断方式可让硬件主动通知 CPU,大幅提升效率。

1. 常用发送中断:TXE 中断

- 使能:配置 CR1 的 Bit7(TXEIE)为 1;

- 触发条件:当 TDR 中的数据转移到移位寄存器(SR 的 Bit7(TXE)为 1)时,触发中断;

- 作用:中断触发后,CPU 可在中断服务函数中写入下一个数据,无需轮询 TXE 位

2. 常用接收中断:RXNE 中断

- 使能:配置 CR1 的 Bit5(RXNEIE)为 1;

- 触发条件:当 RDR 中有新数据(SR 的 Bit5(RXNE)为 1)时,触发中断;

- 作用:中断触发后,CPU 可在中断服务函数中读取 RDR 数据,无需轮询 RXNE 位。

3. 其他中断:发送完成中断(TC)

- 触发条件:当移位寄存器的数据全部发送完成(SR 的 Bit6(TC)为 1)时,触发中断;

- 适用场景:需确认数据完全发送(如发送完后关闭外设)的场景。

总结

UART 硬件的核心是 “寄存器配置 + 状态判断 + 数据转移”:

- 配置靠 CR1/CR2/CR3,决定通信参数;

- 发送靠 TDR→移位寄存器→TX,状态靠 SR 的 TXE/TC 判断;

- 接收靠 RX→移位寄存器→RDR,状态靠 SR 的 RXNE 判断;

- 中断(TXEIE/RXNEIE)可替代查询,提升 CPU 效率。

结尾

本文拆解了 STM32 UART 的硬件结构和数据收发流程,明确了核心寄存器的作用和状态判断逻辑。下一篇笔记,我们将基于这些硬件知识,通过 CubeMX 配置 UART实现 “串口发送字符串” 和 “串口接收数据” 的实战编程。

Hello_Embed 继续带你从硬件原理到实战编程,逐步掌握 UART 通信,敬请期待~