STM32学习记录--Day4

今天了解了一下SPI总线:

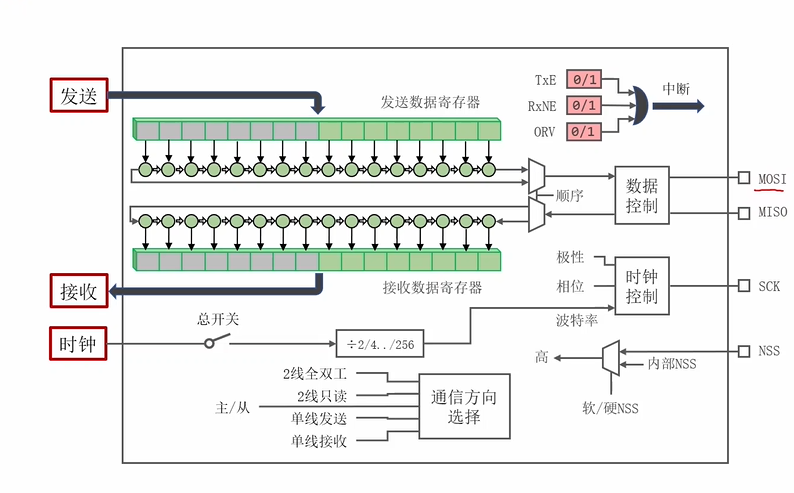

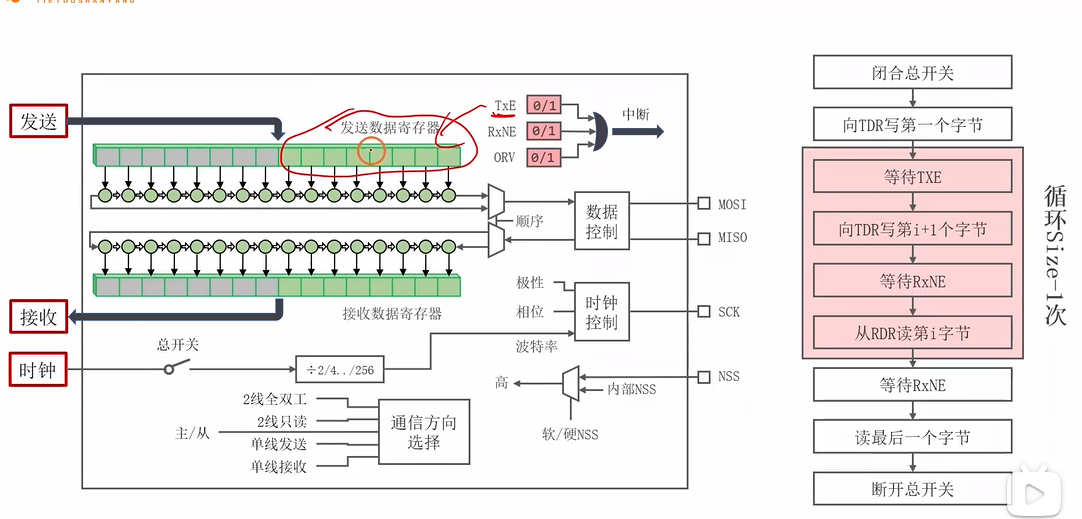

1.SPI内部结构

🔌 SPI 四大核心引脚功能详解

1. MOSI (Master Output Slave Input)

- 功能:主机输出数据线

- 工作流程:

- 主机内部发送数据寄存器 (

TxDR) 的数据 → 移位寄存器 → 数据控制单元 → 通过MOSI引脚输出至从机。

- 主机内部发送数据寄存器 (

- 关键控制:

- 数据控制单元受 “顺序” 设置(MSB/LSB优先)和 “极性/相位” 配置(时钟边沿采样)影响。

- 用户代码关联:

// 用户代码中MOSI配置(PB5) GPIO_InitStruct.GPIO_Pin = GPIO_Pin_5; GPIO_InitStruct.GPIO_Mode = GPIO_Mode_AF_PP; // 复用推挽输出

2. MISO (Master Input Slave Output)

- 功能:主机输入数据线

- 工作流程:

- 从机返回的数据 → 通过MISO引脚 → 接收数据寄存器 (

RxDR)。

- 从机返回的数据 → 通过MISO引脚 → 接收数据寄存器 (

- 状态监测:

-

RxNE(Receive Not Empty) 标志:当RxDR收到新数据时置1,触发中断或供CPU读取。

-

- 用户代码关联:

// 用户代码中MISO配置(PB4) GPIO_InitStruct.GPIO_Pin = GPIO_Pin_4; GPIO_InitStruct.GPIO_Mode = GPIO_Mode_IPU; // 输入上拉

3. SCK (Serial Clock)

- 功能:主机输出的同步时钟

- 控制单元:

- 时钟控制模块 生成SCK信号,受以下参数控制:

- 波特率:时钟频率(由PCLK分频)。

- 极性 (CPOL):

CPOL=0:空闲时SCK为低电平CPOL=1:空闲时SCK为高电平

- 相位 (CPHA):

CPHA=0:数据在时钟第一个边沿采样CPHA=1:数据在时钟第二个边沿采样

- 时钟控制模块 生成SCK信号,受以下参数控制:

- 用户代码关联:

SPI_InitStruct.SPI_CPOL = SPI_CPOL_Low; // CPOL=0 SPI_InitStruct.SPI_CPHA = SPI_CPHA_1Edge; // CPHA=0

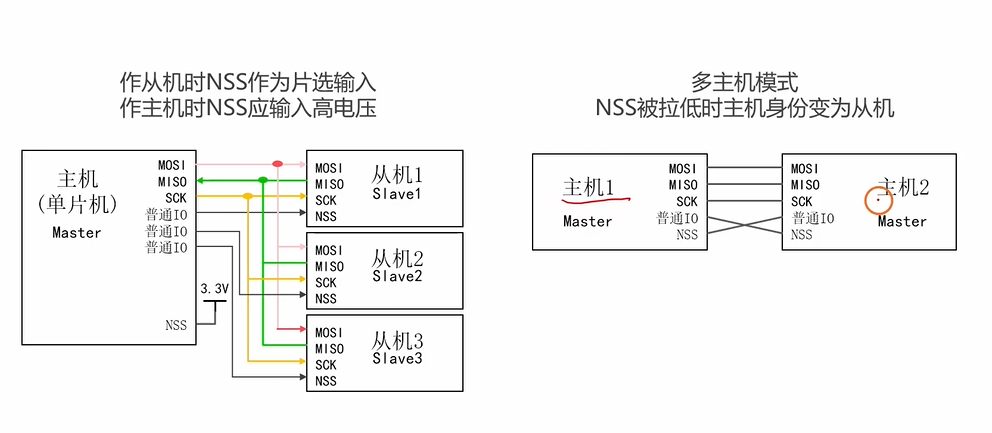

4. NSS (Slave Select)

- 功能:从机片选信号(低电平有效)

- 工作模式:

- 硬件模式:

- 由SPI控制器自动控制(图示中 “内部NSS”)。

- 软件模式:

- 用户通过GPIO手动控制(图示中 “软/硬NSS” 选择)。

- 硬件模式:

- 关键场景:

- 传输开始前:拉低NSS选中从机。

- 传输结束后:拉高NSS释放从机。

- 用户代码关联:

// 用户代码中使用PA0模拟NSS(软件控制) GPIO_WriteBit(GPIOA, GPIO_Pin_0, Bit_RESET); // 选中从机(W25Q64) SPI_Cmd(SPI1, ENABLE); // 启动SPI传输

⚙️ 辅助功能模块关联引脚

中断系统:

-

TxE(Transmit Empty):发送寄存器空 → 可写入新数据。 -

RxNE(Receive Not Empty):接收寄存器非空 → 可读取数据。 -

OVR(Overrun):数据覆盖错误 → 需清除标志。

// 用户代码中轮询标志位 while(SPI_I2S_GetFlagStatus(SPIx, SPI_I2S_FLAG_TXE) == RESET); // 等待TxE-

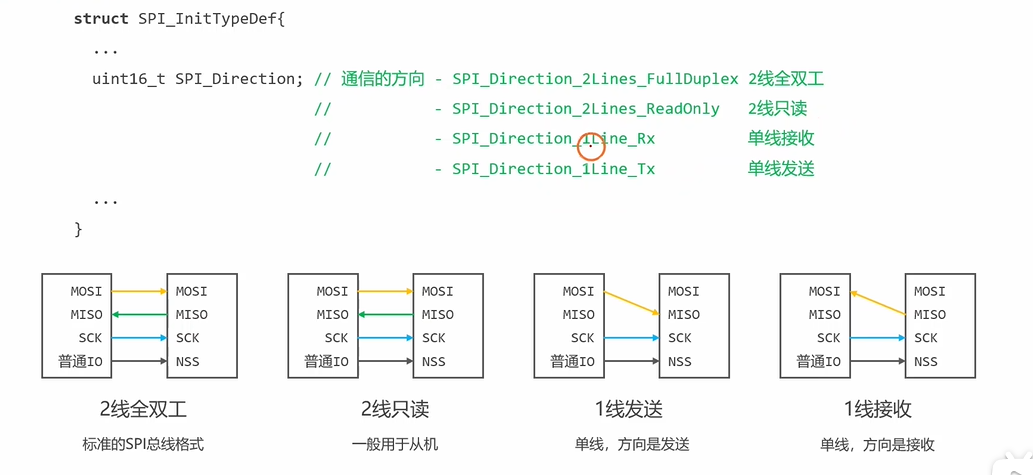

通信方向选择:

- 支持多模式(图中红框区域):

- 2线全双工:同时使用MOSI和MISO(标准SPI)。

- 2线只收:仅用MISO(从机到主机)。

- 单线模式:半双工通信(共用单数据线)。

SPI_InitStruct.SPI_Direction = SPI_Direction_2Lines_FullDuplex;- 支持多模式(图中红框区域):

主从控制:

- 主/从模式:决定SCK由谁生成(主机:SCK输出;从机:SCK输入)。

SPI_InitStruct.SPI_Mode = SPI_Mode_Master; // 主机模式

📝 引脚功能总结表

| 引脚 | 方向 | 核心功能 | 关键关联模块 |

|---|---|---|---|

| MOSI | 主机→从机 | 主机输出数据 | 发送数据寄存器 → 数据控制单元 |

| MISO | 从机→主机 | 主机输入数据 | 接收数据寄存器 → RxNE中断 |

| SCK | 主机→从机 | 提供同步时钟 | 时钟控制(CPOL/CPHA) |

| NSS | 主机→从机 | 从机选择控制(低有效) | 软/硬NSS选择 → 内部控制逻辑 |

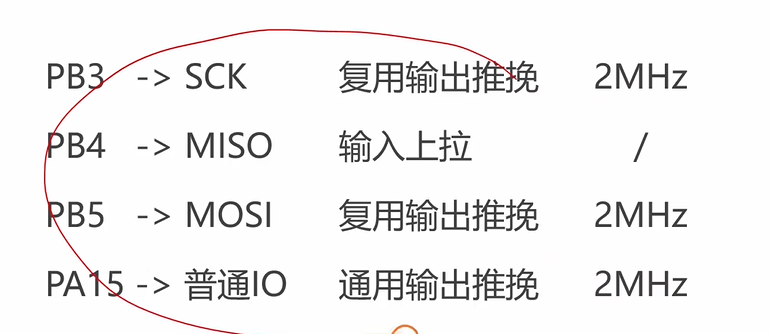

💡 深入理解引脚配置

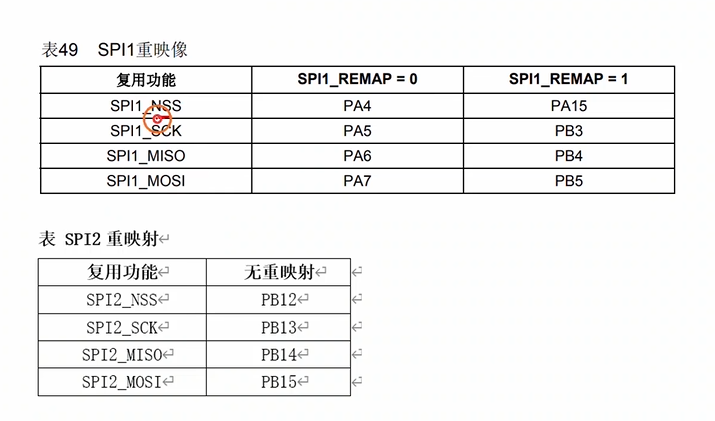

此处用的PA15上电后默认功能不是普通IO,所以可以改用其它IO口,或重映射。

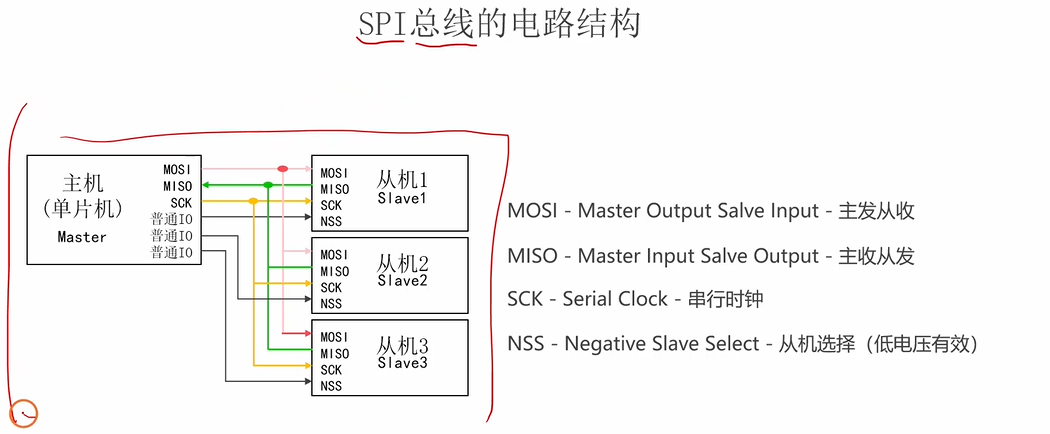

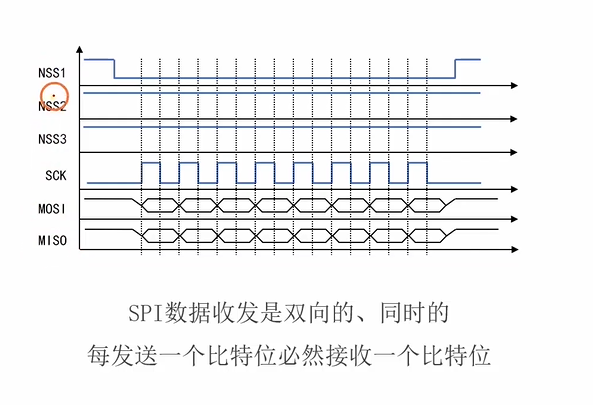

2.SPI总线电路结构

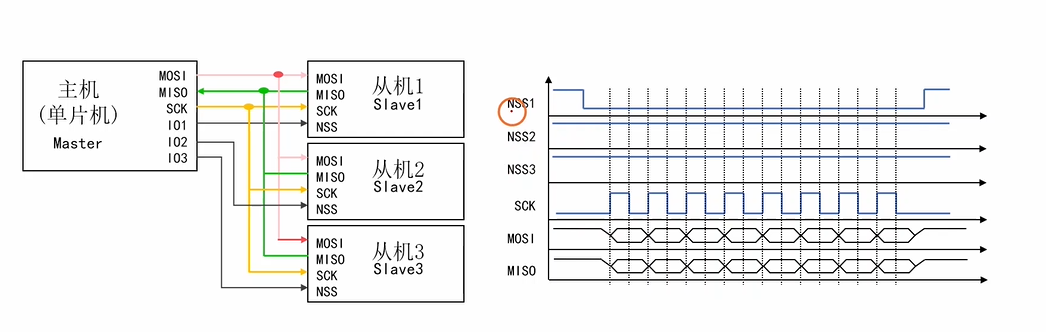

3.SPI总线通信流程

3.1收发流程

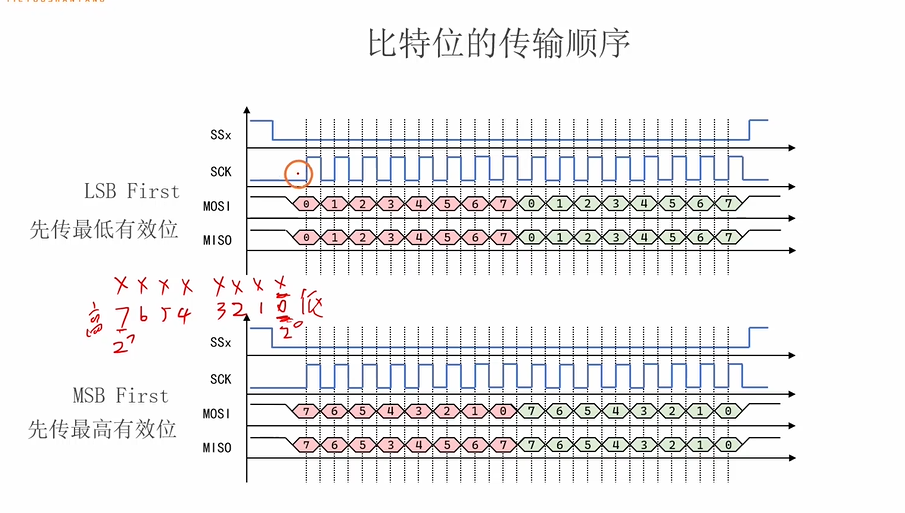

数据传输顺序有两种:

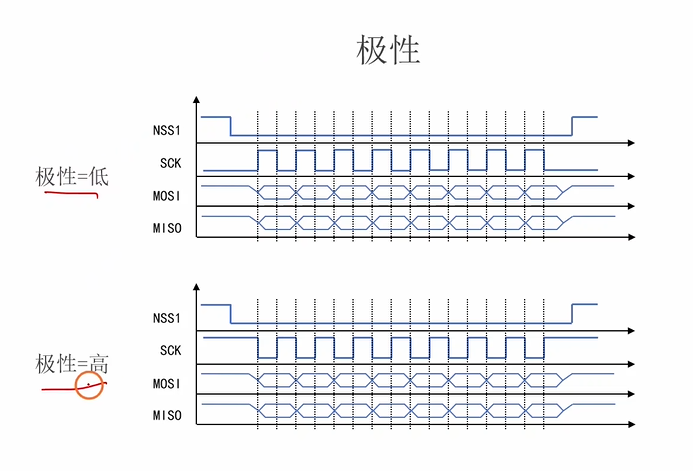

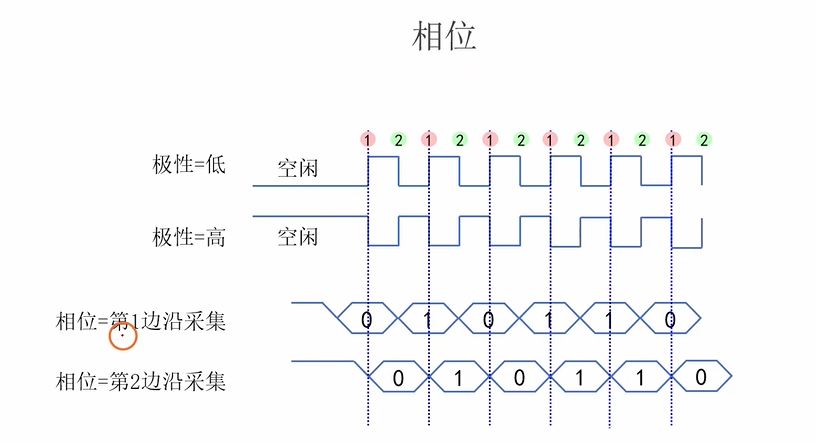

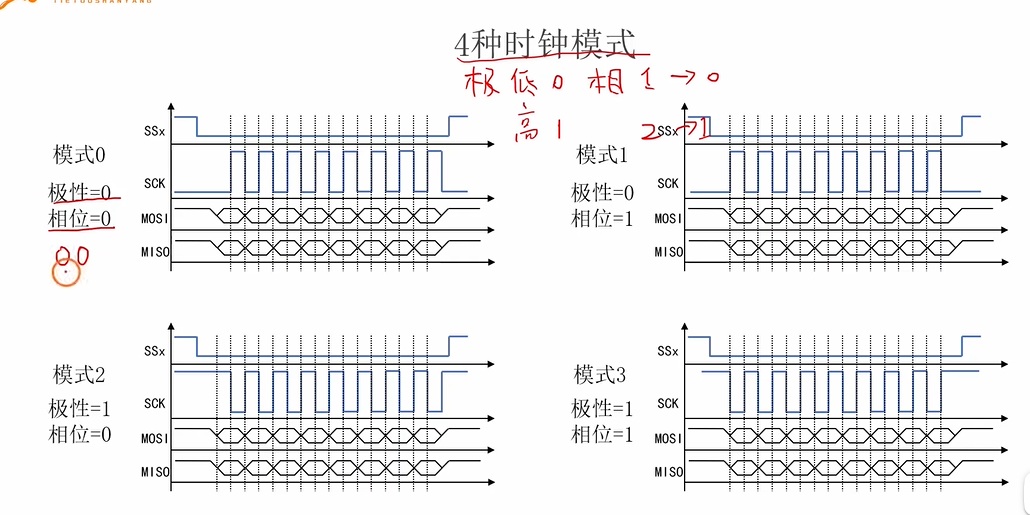

3.2时钟模式

极性与相位:

当SCK开始与结束的电平为低时,极性为低;当SCK开始与结束的电平为高时,极性为高

- 相位=第1边沿采集(CPHA=0):数据在SCK的第一个边沿(即CPOL变化的第一个边沿)被采样。

- 相位=第2边沿采集(CPHA=1):数据在SCK的第二个边沿(即CPOL变化的第二个边沿)被采样。

3.3通信方向