<RT1176系列12>DMAMUX入门级应用和DMAMUX MAP表

1、概述

之前在<RT1176系列5>LPUART入门级应用和基础API解析-CSDN博客文章中简要讲述如何引用DMA进行配置,这里继续这篇文章进行一些关于DMA源的配置点。

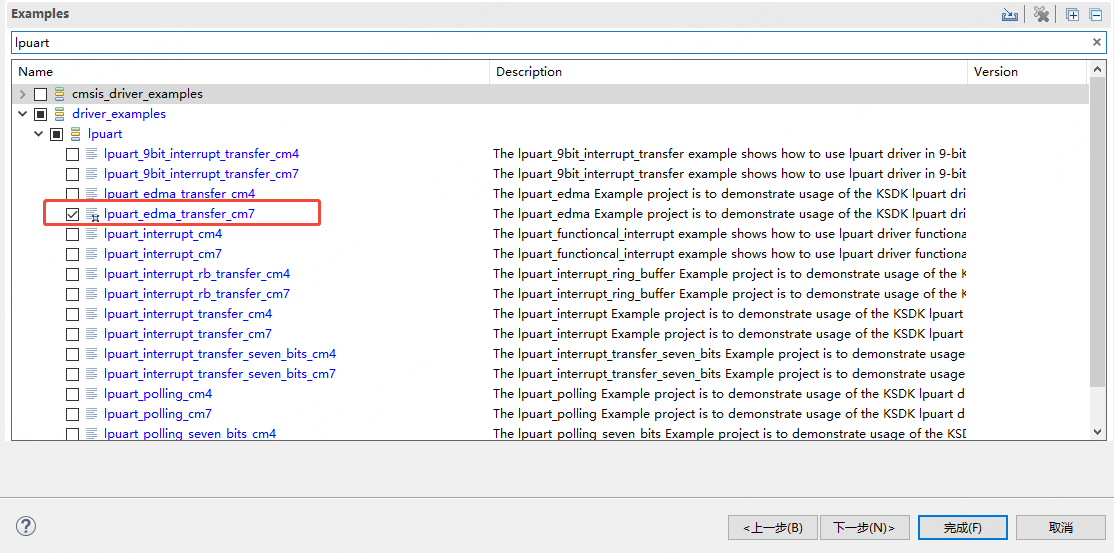

2、SDK工程参考

3、DMA TX/RX源的配置

配置 LPUART 发送通道 - 将 DMA 通道LPUART_TX_DMA_CHANNEL分配给 LPUART 的发送请求源LPUART_TX_DMA_REQUES。

配置 LPUART 接收通道 - 将 DMA 通道LPUART_RX_DMA_CHANNEL分配给 LPUART 的接收请求源LPUART_RX_DMA_REQUEST。

#define LPUART_TX_DMA_REQUEST 8U

#define LPUART_RX_DMA_REQUEST 9U/* Set channel for LPUART */

DMAMUX_SetSource(EXAMPLE_LPUART_DMAMUX_BASEADDR, LPUART_TX_DMA_CHANNEL, LPUART_TX_DMA_REQUEST);

DMAMUX_SetSource(EXAMPLE_LPUART_DMAMUX_BASEADDR, LPUART_RX_DMA_CHANNEL, LPUART_RX_DMA_REQUEST);具体实现:

根据 DMAMUX_CHCFG 寄存器宽度,

清除原 SOURCE 位 (& ~DMAMUX_CHCFG_SOURCE_MASK),并设置新 SOURCE 值 (|DMAMUX_CHCFG_SOURCE(source)),写入寄存器。

#define DMAMUX_CHCFG_SOURCE(x) (((uint32_t)(((uint32_t)(x)) << DMAMUX_CHCFG_SOURCE_SHIFT)) & DMAMUX_CHCFG_SOURCE_MASK)static inline void DMAMUX_SetSource(DMAMUX_Type *base, uint32_t channel, int32_t source)

{

assert(channel < (uint32_t)FSL_FEATURE_DMAMUX_MODULE_CHANNEL);#if defined FSL_FEATURE_DMAMUX_CHCFG_REGISTER_WIDTH && (FSL_FEATURE_DMAMUX_CHCFG_REGISTER_WIDTH == 32U)

base->CHCFG[channel] = ((base->CHCFG[channel] & ~DMAMUX_CHCFG_SOURCE_MASK) | DMAMUX_CHCFG_SOURCE(source));

#else

base->CHCFG[channel] = (uint8_t)((base->CHCFG[channel] & ~DMAMUX_CHCFG_SOURCE_MASK) | DMAMUX_CHCFG_SOURCE(source));

#endif

}4、MAP表

关于具体source(slot编号)的查询,需要对应到芯片手册中的DMAMUX MAP表,具体如下:

| Channel | Module | Gate | Description |

|---|---|---|---|

| 0 | Reserved | - | Reserved |

| 1 | FLEXIO1 | OR | FlexIO1 shifter2 DMA Request OR FlexIO1 shifter2 Async DMA Request OR FlexIO1 shifter3 DMA Request OR FlexIO1 shifter3 Async DMA Request OR FlexIO1 timer2 DMA Request OR FlexIO1 timer2 Async DMA Request OR FlexIO1 timer3 DMA Request OR FlexIO1 timer3 Async DMA Request |

| 2 | FLEXIO1 | OR | FlexIO1 shifter4 DMA Request OR FlexIO1 shifter4 Async DMA Request OR FlexIO1 shifter5 DMA Request OR FlexIO1 shifter5 Async DMA Request OR FlexIO1 timer4 DMA Request OR FlexIO1 timer4 Async DMA Request OR FlexIO1 timer5 DMA Request OR FlexIO1 timer5 Async DMA Request |

| 3 | FLEXIO1 | OR | FlexIO1 shifter6 DMA Request OR FlexIO1 shifter6 Async DMA Request OR FlexIO1 shifter7 DMA Request OR FlexIO1 shifter7 Async DMA Request OR FlexIO1 timer6 DMA Request OR FlexIO1 timer6 Async DMA Request OR FlexIO1 timer7 DMA Request OR FlexIO1 timer7 Async DMA Request |

| 4 | FLEXIO2 | OR | FlexIO2 shifter0 DMA Request FlexIO2 shifter0 Async DMA Request FlexIO2 shifter1 DMA Request FlexIO2 shifter1 Async DMA Request FlexIO2 timer0 DMA Request FlexIO2 timer0 Async DMA Request FlexIO2 timer1 DMA Request FlexIO2 timer1 Async DMA Request |

| 5 | FLEXIO2 | OR | FlexIO2 shifter2 DMA Request FlexIO2 shifter2 Async DMA Request FlexIO2 shifter3 DMA Request FlexIO2 shifter3 Async DMA Request FlexIO2 timer2 DMA Request FlexIO2 timer2 Async DMA Request FlexIO2 timer3 DMA Request FlexIO2 timer3 Async DMA Request |

| 6 | FLEXIO2 | OR | FlexIO2 shifter4 DMA Request FlexIO2 shifter4 Async DMA Request FlexIO2 shifter5 DMA Request FlexIO2 shifter5 Async DMA Request FlexIO2 timer4 DMA Request FlexIO2 timer4 Async DMA Request FlexIO2 timer5 DMA Request FlexIO2 timer5 Async DMA Request |

| 7 | FLEXIO2 | OR | FlexIO2 shifter6 DMA Request FlexIO2 shifter6 Async DMA Request FlexIO2 shifter7 DMA Request FlexIO2 shifter7 Async DMA Request FlexIO2 timer6 DMA Request FlexIO2 timer6 Async DMA Request FlexIO2 timer7 DMA Request FlexIO2 timer7 Async DMA Request |

| 8 | LPUART1 | OR | UART1 Tx FIFO DMA Request UART1 Tx FIFO Async DMA Request |

| 9 | LPUART1 | OR | UART1 Rx FIFO DMA Request UART1 Rx FIFO Async DMA Request |

| 10 | LPUART2 | OR | UART2 Tx FIFO DMA Request UART2 Tx FIFO Async DMA Request |

| 11 | LPUART2 | OR | UART2 Rx FIFO DMA Request UART2 Rx FIFO Async DMA Request |

| 12 | LPUART3 | OR | UART3 Tx FIFO Async DMA Request UART3 Tx FIFO DMA Request |

| 13 | LPUART3 | OR | UART3 Rx FIFO DMA Request UART3 Rx FIFO Async DMA Request |

| 14 | LPUART4 | OR | UART4 Tx FIFO DMA Request UART4 Tx FIFO Async DMA Request |

| 15 | LPUART4 | OR | UART4 Rx FIFO DMA Request UART4 Rx FIFO Async DMA Request |

| 16 | LPUART5 | OR | UART5 Tx FIFO DMA Request UART5 Tx FIFO Async DMA Request |

| 17 | LPUART5 | OR | UART5 Rx FIFO DMA Request UART5 Rx FIFO Async DMA Request |

| 18 | LPUART6 | OR | UART6 Tx FIFO DMA Request UART6 Tx FIFO Async DMA Request |

| 19 | LPUART6 | OR | UART6 Rx FIFO DMA Request UART6 Rx FIFO Async DMA Request |

| 20 | LPUART7 | OR | UART7 Tx FIFO DMA Request UART7 Tx FIFO Async DMA Request |

| 21 | LPUART7 | OR | UART7 Rx FIFO DMA Request UART7 Rx FIFO Async DMA Request |

| 22 | LPUART8 | OR | UART8 Tx FIFO DMA Request UART8 Tx FIFO Async DMA Request |

| 23 | LPUART8 | OR | UART8 Rx FIFO DMA Request UART8 Rx FIFO Async DMA Request |

| 24 | LPUART9 | OR | UART9 Tx FIFO DMA Request UART9 Tx FIFO Async DMA Request |

| 25 | LPUART9 | OR | UART9 Rx FIFO DMA Request UART9 Rx FIFO Async DMA Request |

| 26 | LPUART10 | OR | UART10 Tx FIFO DMA Request UART10 Tx FIFO Async DMA Request |

| 27 | LPUART10 | OR | UART10 Rx FIFO DMA Request UART10 Rx FIFO Async DMA Request |

| 28 | LPUART11 | OR | UART11 Tx FIFO DMA Request UART11 Tx FIFO Async DMA Request |

| 29 | LPUART11 | OR | UART11 Rx FIFO DMA Request UART11 Rx FIFO Async DMA Request |

| 30 | LPUART12 | OR | UART12 Tx FIFO DMA Request UART12 Tx FIFO Async DMA Request |

| 31 | LPUART12 | OR | UART12 Tx FIFO Async DMA Request UART12 Rx FIFO DMA Request UART12 Rx FIFO Async DMA Request |

| 32 | CSI | - | CSI Write DMA Request |

| 33 | PXP | - | PXP DMA Event |

| 34 | eLCDIF | - | eLCDIF DMA Event |

| 35 | LCDIFv2 | - | LCDIFv2 DMA Event |

| 36 | LPSPI1 | OR | LPSPI1 Rx FIFO DMA Request LPSPI1 Rx FIFO Async DMA Request |

| 37 | LPSPI1 | OR | LPSPI1 Tx FIFO DMA Request LPSPI1 Tx FIFO Async DMA Request |

| 38 | LPSPI2 | OR | LPSPI2 Rx FIFO DMA Request LPSPI2 Rx FIFO Async DMA Request |

| 39 | LPSPI2 | OR | LPSPI2 Tx FIFO DMA Request LPSPI2 Tx FIFO Async DMA Request |

| 40 | LPSPI3 | OR | LPSPI3 Rx FIFO DMA Request LPSPI3 Rx FIFO Async DMA Request |

| 41 | LPSPI3 | OR | LPSPI3 Tx FIFO DMA Request LPSPI3 Tx FIFO Async DMA Request |

| 42 | LPSPI4 | OR | LPSPI4 Rx FIFO DMA Request LPSPI4 Rx FIFO Async DMA Request |

| 43 | LPSPI4 | OR | LPSPI4 Tx FIFO DMA Request LPSPI4 Tx FIFO Async DMA Request |

| 44 | LPSPI5 | OR | LPSPI5 Rx FIFO DMA Request LPSPI5 Rx FIFO Async DMA Request |

| 45 | LPSPI5 | OR | LPSPI5 Tx FIFO DMA Request LPSPI5 Tx FIFO Async DMA Request |

| 46 | LPSPI6 | OR | LPSPI6 Rx FIFO DMA Request LPSPI6 Rx FIFO Async DMA Request |

| 47 | LPSPI6 | OR | LPSPI6 Tx FIFO DMA Request LPSPI6 Tx FIFO Async DMA Request |

| 48 | LPI2C1 | OR | I2C1 Master Rx FIFO DMA Request I2C1 Master Rx FIFO Async DMA Request I2C1 Slave Rx FIFO DMA Request I2C1 Slave Rx FIFO Async DMA Request I2C1 Master Tx FIFO DMA Request I2C1 Master Tx FIFO Async DMA Request I2C1 Slave Tx FIFO DMA Request I2C1 Slave Tx FIFO Async DMA Request |

| 49 | LPI2C2 | OR | I2C2 Master Rx FIFO DMA Request I2C2 Master Rx FIFO Async DMA Request I2C2 Slave Rx FIFO DMA Request I2C2 Slave Rx FIFO Async DMA Request I2C2 Master Tx FIFO DMA Request I2C2 Master Tx FIFO Async DMA Request I2C2 Slave Tx FIFO DMA Request I2C2 Slave Tx FIFO Async DMA Request |

| 50 | LPI2C3 | OR | I2C3 Master Rx FIFO DMA Request I2C3 Master Rx FIFO Async DMA Request I2C3 Slave Rx FIFO DMA Request I2C3 Slave Rx FIFO Async DMA Request I2C3 Master Tx FIFO DMA Request I2C3 Master Tx FIFO Async DMA Request I2C3 Slave Tx FIFO DMA Request I2C3 Slave Tx FIFO Async DMA Request |

| 51 | LPI2C4 | OR | I2C4 Master Rx FIFO DMA Request I2C4 Master Rx FIFO Async DMA Request I2C4 Slave Rx FIFO DMA Request I2C4 Slave Rx FIFO Async DMA Request I2C4 Master Tx FIFO DMA Request I2C4 Master Tx FIFO Async DMA Request I2C4 Slave Tx FIFO DMA Request I2C4 Slave Tx FIFO Async DMA Request |

| 52 | LPI2C5 | OR | I2C5 Master Rx FIFO DMA Request I2C5 Master Rx FIFO Async DMA Request I2C5 Slave Rx FIFO DMA Request I2C5 Slave Rx FIFO Async DMA Request I2C5 Master Tx FIFO DMA Request I2C5 Master Tx FIFO Async DMA Request I2C5 Slave Tx FIFO DMA Request I2C5 Slave Tx FIFO Async DMA Request |

| 53 | LPI2C6 | OR | I2C6 Slave Rx FIFO Async DMA Request I2C6 Master Rx FIFO DMA Request I2C6 Master Rx FIFO Async DMA Request I2C6 Slave Rx FIFO DMA Request I2C6 Master Tx FIFO DMA Request I2C6 Master Tx FIFO Async DMA Request I2C6 Slave Tx FIFO DMA Request I2C6 Slave Tx FIFO Async DMA Request |

| 54 | SAI1 | - | SAI1 Rx FIFO DMA Request |

| 55 | SAI1 | - | SAI1 Tx FIFO DMA Request |

| 56 | SAI2 | - | SAI2 Rx FIFO DMA Request |

| 57 | SAI2 | - | SAI2 Tx FIFO DMA Request |

| 58 | SAI3 | - | SAI3 Rx FIFO DMA Request |

| 59 | SAI3 | - | SAI3 Tx FIFO DMA Request |

| 60 | SAI4 | - | SAI4 Rx FIFO DMA Request |

| 61 | SAI4 | - | SAI4 Tx FIFO DMA Request |

| 62 | SPDIF | - | SPDIF RX DMA Request |

| 63 | SPDIF | - | SPDIF TX DMA Request |

| 64 | ADC_ETC | OR | ADC_ETC eDMA Request |

| 65 | FI_FXIO1 | OR | FlexIO1 shifter0 Async DMA Request FlexIO1 shifter0 DMA Request FlexIO1 shifter1 Async DMA Request FlexIO1 shifter1 DMA Request FlexIO1 timer0 DMA Request FlexIO1 timer0 Async DMA Request FlexIO1 timer1 DMA Request FlexIO1 timer1 Async DMA Request |

| 66 | LPADC1 | - | ADC1 DMA Request |

| 67 | LPADC2 | - | ADC2 DMA Request |

| 68 | Reserved | - | Reserved |

| 69 | ACMP1 | - | ACMP1 DMA Request |

| 70 | ACMP2 | - | ACMP2 DMA Request |

| 71 | ACMP3 | - | ACMP3 DMA Request |

| 72 | ACMP4 | - | ACMP4 DMA Request |

| 73-76 | Reserved | - | Reserved |

| 77 | FLEXSPI1 | - | FlexSPI1 Rx FIFO DMA Request |

| 78 | FLEXSPI1 | - | FlexSPI1 Tx FIFO DMA Request |

| 79 | FLEXSPI2 | - | FlexSPI2 Rx FIFO DMA Request |

| 80 | FLEXSPI2 | - | FlexSPI2 Tx FIFO DMA Request |

| 81 | XBAR1 | - | XBAR1_OUT0 DMA request |

| 82 | XBAR1 | - | XBAR1_OUT1 DMA request |

| 83 | XBAR1 | - | XBAR1_OUT2 DMA request |

| 84 | XBAR1 | - | XBAR1_OUT3 DMA request |

| 85 | FLEXPWM1 | - | FlexPWM1 sub - module0 capture register read DMA request |

| 86 | FLEXPWM1 | - | FlexPWM1 sub - module1 capture register read DMA request |

| 87 | FLEXPWM1 | - | FlexPWM1 sub - module2 capture register read DMA request |

| 88 | FLEXPWM1 | - | FlexPWM1 sub - module3 capture register read DMA request |

| 89 | FLEXPWM1 | - | FlexPWM1 sub - module0 value registers write DMA request |

| 90 | FLEXPWM1 | - | FlexPWM1 sub - module1 value registers write DMA request |

| 91 | FLEXPWM1 | - | FlexPWM1 sub - module2 value registers write DMA request |

| 92 | FLEXPWM1 | - | FlexPWM1 sub - module3 value registers write DMA request |

| 93 | FLEXPWM2 | - | FlexPWM2 sub - module0 capture register read DMA request |

| 94 | FLEXPWM2 | - | FlexPWM2 sub - module1 capture register read DMA request |

| 95 | FLEXPWM2 | - | FlexPWM2 sub - module2 capture register read DMA request |

| 96 | FLEXPWM2 | - | FlexPWM2 sub - module3 capture register read DMA request |

| 97 | FLEXPWM2 | - | FlexPWM2 sub - module0 value registers write DMA request |

| 98 | FLEXPWM2 | - | FlexPWM2 sub - module1 value registers write DMA request |

| 99 | FLEXPWM2 | - | FlexPWM2 sub - module2 value registers write DMA request |

| 100 | FLEXPWM2 | - | FlexPWM2 sub - module3 value registers write DMA request |

| 101 | FLEXPWM3 | - | FlexPWM3 sub - module0 capture register read DMA request |

| 102 | FLEXPWM3 | - | FlexPWM3 sub - module1 capture register read DMA request |

| 103 | FLEXPWM3 | - | FlexPWM3 sub - module2 capture register read DMA request |

| 104 | FLEXPWM3 | - | FlexPWM3 sub - module3 capture register read DMA request |

| 105 | FLEXPWM3 | - | FlexPWM3 sub - module0 value registers write DMA request |

| 106 | FLEXPWM3 | - | FlexPWM3 sub - module1 value registers write DMA request |

| 107 | FLEXPWM3 | - | FlexPWM3 sub - module2 value registers write DMA request |

| 108 | FLEXPWM3 | - | FlexPWM3 sub - module3 value registers write DMA request |

| 109 | FLEXPWM4 | - | FlexPWM4 sub - module0 capture register read DMA request |

| 110 | FLEXPWM4 | - | FlexPWM4 sub - module1 capture register read DMA request |

| 111 | FLEXPWM4 | - | FlexPWM4 sub - module2 capture register read DMA request |

| 112 | FLEXPWM4 | - | FlexPWM4 sub - module3 capture register read DMA request |

| 113 | FLEXPWM4 | - | FlexPWM4 sub - module0 value registers write DMA request |

| 114 | FLEXPWM4 | - | FlexPWM4 sub - module1 value registers write DMA request |

| 115 | FLEXPWM4 | - | FlexPWM4 sub - module2 value registers write DMA request |

| 116 | FLEXPWM4 | - | FlexPWM4 sub - module3 value registers write DMA request |

| 117 - 132 | Reserved | - | Reserved |

| 133 | QTIMER1 | - | QTIMER1 timer0 capture register read DMA request |

| 134 | QTIMER1 | - | QTIMER1 timer1 capture register read DMA request |

| 135 | QTIMER1 | - | QTIMER1 timer2 capture register read DMA request |

| 136 | QTIMER1 | - | QTIMER1 timer3 capture register read DMA request |

| 137 | QTIMER1 | OR | QTimer1 timer0 cmpld1 register write DMA request OR QTimer1 timer1 cmpld2 register write DMA request |

| 138 | QTIMER1 | OR | QTimer1 timer1 cmpld1 register write DMA request OR QTimer1 timer0 cmpld2 register write DMA request |

| 139 | QTIMER1 | OR | QTimer1 timer2 cmpld1 register write DMA request OR QTimer1 timer3 cmpld2 register write DMA request |

| 140 | QTIMER1 | OR | QTimer1 timer3 cmpld1 register write DMA request OR QTimer1 timer2 cmpld2 register write DMA request |

| 141 | QTIMER2 | - | QTIMER2 timer0 capture register read DMA request |

| 142 | QTIMER2 | - | QTIMER2 timer1 capture register read DMA request |

| 143 | QTIMER2 | - | QTIMER2 timer2 capture register read DMA request |

| 144 | QTIMER2 | - | QTIMER2 timer3 capture register read DMA request |

| 145 | QTIMER2 | OR | QTimer2 timer0 cmpld1 register write DMA request OR QTimer2 timer1 cmpld2 register write DMA request |

| 146 | QTIMER2 | OR | QTimer2 timer1 cmpld1 register write DMA request OR QTimer2 timer0 cmpld2 register write DMA request |

| 147 | QTIMER2 | OR | QTimer2 timer2 cmpld1 register write DMA request OR QTimer2 timer3 cmpld2 register write DMA request |

| 148 | QTIMER2 | OR | QTimer2 timer3 cmpld1 register write DMA request OR QTimer2 timer2 cmpld2 register write DMA request |

| 149 | QTIMER3 | - | QTIMER3 timer0 capture register read DMA request |

| 150 | QTIMER3 | - | QTIMER3 timer1 capture register read DMA request |

| 151 | QTIMER3 | - | QTIMER3 timer2 capture register read DMA request |

| 152 | QTIMER3 | - | QTIMER3 timer3 capture register read DMA request |

| 153 | QTIMER3 | OR | QTimer3 timer0 cmpld1 register write DMA request OR QTimer3 timer1 cmpld2 register write DMA request |

| 154 | QTIMER3 | OR | QTimer3 timer1 cmpld1 register write DMA request OR QTimer3 timer0 cmpld2 register write DMA request |

| 155 | QTIMER3 | OR | QTimer3 timer2 cmpld1 register write DMA request OR QTimer3 timer3 cmpld2 register write DMA request |

| 156 | QTIMER3 | OR | QTimer3 timer3 cmpld1 register write DMA request OR QTimer3 timer2 cmpld2 register write DMA request |

| 157 | QTIMER4 | - | QTIMER4 timer0 capture register read DMA request |

| 158 | QTIMER4 | - | QTIMER4 timer1 capture register read DMA request |

| 159 | QTIMER4 | - | QTIMER4 timer2 capture register read DMA request |

| 160 | QTIMER4 | - | QTIMER4 timer3 capture register read DMA request |

| 161 | QTIMER4 | OR | QTimer4 timer0 cmpld1 register write DMA request OR QTimer4 timer1 cmpld2 register write DMA request |

| 162 | QTIMER4 | OR | QTimer4 timer1 cmpld1 register write DMA request OR QTimer4 timer0 cmpld2 register write DMA request |

| 163 | QTIMER4 | OR | QTimer4 timer2 cmpld1 register write DMA request OR QTimer4 timer3 cmpld2 register write DMA request |

| 164 | QTIMER4 | OR | QTimer4 timer3 cmpld1 register write DMA request OR QTimer4 timer2 cmpld2 register write DMA request |

| 165 - 180 | Reserved | - | Reserved |

| 181 | PDM | OR | PDM DMA request OR PDM DMA async request |

| 182 | ENET | - | ENET Timer0 DMA Request |

| 183 | ENET | - | ENET Timer1 DMA Request |

| 184 | ENET_1G | - | ENET_1G Timer0 DMA Request |

| 185 | ENET_1G | - | ENET_1G Timer1 DMA Request |

| 186 | CAN1 | - | CAN1 DMA Request |

| 187 | CAN2 | - | CAN2 DMA Request |

| 188 | CAN3 | - | CAN3 DMA Request |

| 189 | DAC | - | DAC DMA Request |

| 190 | Reserved | - | Reserved |

| 191 | ASRC | - | ASRC pair A input DMA request |

| 192 | ASRC | - | ASRC pair B input DMA request |

| 193 | ASRC | - | ASRC pair C input DMA request |

| 194 | ASRC | - | ASRC pair A output DMA request |

| 195 | ASRC | - | ASRC pair B output DMA request |

| 196 | ASRC | - | ASRC pair C output DMA request |

| 197 | EMVSIM1 | - | EMVSIM1 TX DMA Request |

| 198 | EMVSIM1 | - | EMVSIM1 RX DMA Request |

| 199 | EMVSIM2 | - | EMVSIM2 TX DMA Request |

| 200 | EMVSIM2 | - | EMVSIM2 RX DMA Request |

| 201 | ENET_QOS | - | ENET_QOS PPS0 output DMA Request |

| 202 | ENET_QOS | - | ENET_QOS PPS1 output DMA Request |

| 203 - 207 | Reserved | - | Reserved |