【硬件-笔试面试题】硬件/电子工程师,笔试面试题-38,(知识点:晶体管放大电路频率特性,下限截止频率)

目录

1、题目

2、解答

步骤一:明确下限频率的计算公式

步骤二:分析影响下限频率的因素

步骤三:结合题目分析

3、相关知识点

一、频率特性的概念

二、下限频率和上限频率

三、下限频率的计算公式及影响因素

四、提高放大电路低频特性的方法

题目汇总版--链接:

【硬件-笔试面试题】硬件/电子工程师,笔试面试题汇总版,持续更新学习,加油!!!-CSDN博客

【硬件-笔试面试题】硬件/电子工程师,笔试面试题-38,(知识点:晶体管放大电路频率特性,下限截止频率)

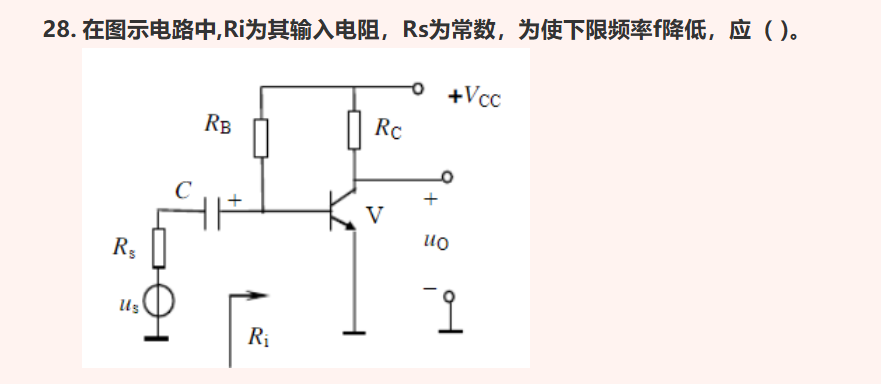

1、题目

2、解答

本题可根据晶体管放大电路下限频率的计算公式,分析影响下限频率的因素。

步骤一:明确下限频率的计算公式

晶体管放大电路的下限频率fL主要由输入回路的耦合电容C和输入电阻Ri、信号源内阻Rs决定,其计算公式为fL=2π(Rs+Ri)C1。

步骤二:分析影响下限频率的因素

从公式fL=2π(Rs+Ri)C1可以看出,下限频率fL与(Rs+Ri)和C有关:

- 当(Rs+Ri)增大时,fL降低;

- 当C增大时,fL降低。

步骤三:结合题目分析

题目中要求使下限频率fL降低,根据上述分析,可以通过增大耦合电容C或者增大输入电阻Ri(因为Rs为常数)来实现。

综上,为使下限频率f降低,应增大耦合电容C或增大输入电阻Ri。

3、相关知识点

本题主要考查晶体管放大电路的频率特性,涉及到下限频率的概念、计算公式以及影响因素等相关知识。以下是详细的知识点讲解:

一、频率特性的概念

晶体管放大电路的频率特性是指放大电路的增益(或放大倍数)随频率变化的特性。

由于电路中存在耦合电容、旁路电容、晶体管的极间电容等电抗元件,放大电路对不同频率的信号具有不同的放大能力。频率特性包括幅频特性和相频特性,幅频特性表示增益的幅值随频率变化的关系,相频特性表示增益的相位随频率变化的关系。

二、下限频率和上限频率

- 下限频率\(f_L\):当信号频率降低时,耦合电容和旁路电容的容抗增大,导致放大电路的增益下降。通常将增益下降到中频段增益的\(\frac{1}{\sqrt{2}}\)(约\(0.707\)倍)时的频率称为下限频率,用\(f_L\)表示。

- 上限频率\(f_H\):当信号频率升高时,晶体管的极间电容和分布电容的容抗减小,导致放大电路的增益下降。通常将增益下降到中频段增益的\(\frac{1}{\sqrt{2}}\)(约\(0.707\)倍)时的频率称为上限频率,用\(f_H\)表示。

- 通频带BW:通频带是指放大电路的增益下降到中频段增益的\(\frac{1}{\sqrt{2}}\)时的频率范围,即\(BW = f_H - f_L\)。通频带越宽,放大电路对不同频率信号的适应能力越强。

三、下限频率的计算公式及影响因素

- 计算公式:晶体管放大电路的下限频率\(f_L\)主要由输入回路的耦合电容C和输入电阻\(R_i\)、信号源内阻\(R_s\)决定,其计算公式为\(f_L=\frac{1}{2\pi(R_s + R_i)C}\)。

- 影响因素:

- 耦合电容C:耦合电容C越大,容抗越小,对低频信号的阻碍作用越小,下限频率\(f_L\)越低。

- 输入电阻\(R_i\):输入电阻\(R_i\)越大,\((R_s + R_i)\)越大,下限频率\(f_L\)越低。

- 信号源内阻\(R_s\):信号源内阻\(R_s\)越大,\((R_s + R_i)\)越大,下限频率\(f_L\)越低。

四、提高放大电路低频特性的方法

为了降低下限频率\(f_L\),提高放大电路对低频信号的放大能力,可以采取以下措施:

- 增大耦合电容C:增大耦合电容的容量,减小其对低频信号的容抗,使更多的低频信号能够通过耦合电容传输到放大电路的输入端。

- 提高输入电阻\(R_i\):通过改变放大电路的结构(如采用射极输出器等),提高放大电路的输入电阻,减小\((R_s + R_i)\)的值,从而降低下限频率\(f_L\)。

- 减小信号源内阻\(R_s\):在实际应用中,信号源内阻\(R_s\)通常是固定的,难以改变。但在设计放大电路时,可以考虑选择内阻较小的信号源。

通过对这些知识点的理解和应用,可以准确分析晶体管放大电路的频率特性,解决类似的电路分析和设计问题。

题目汇总--链接:

【硬件-笔试面试题】硬件/电子工程师,笔试面试题汇总版,持续更新学习,加油!!!-CSDN博客