AXI接口学习

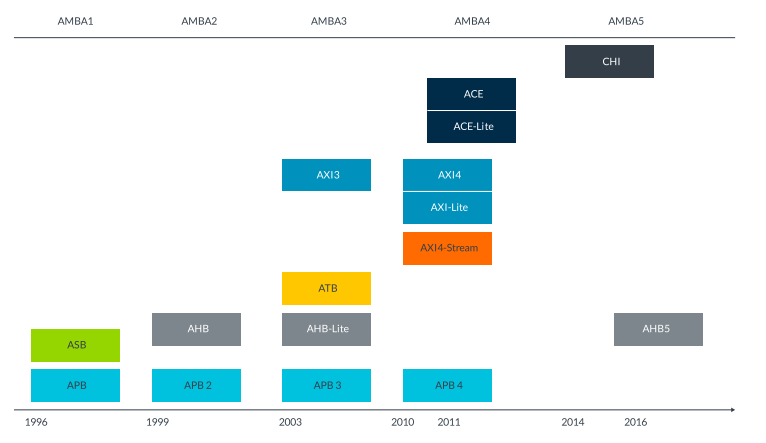

amba总线的发展

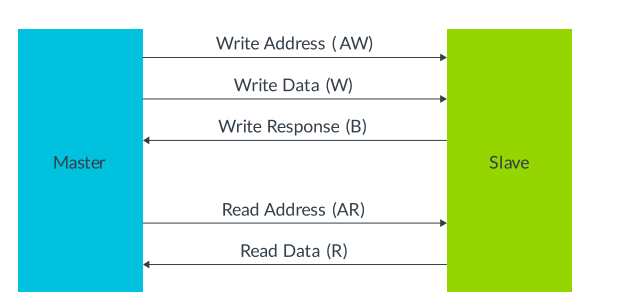

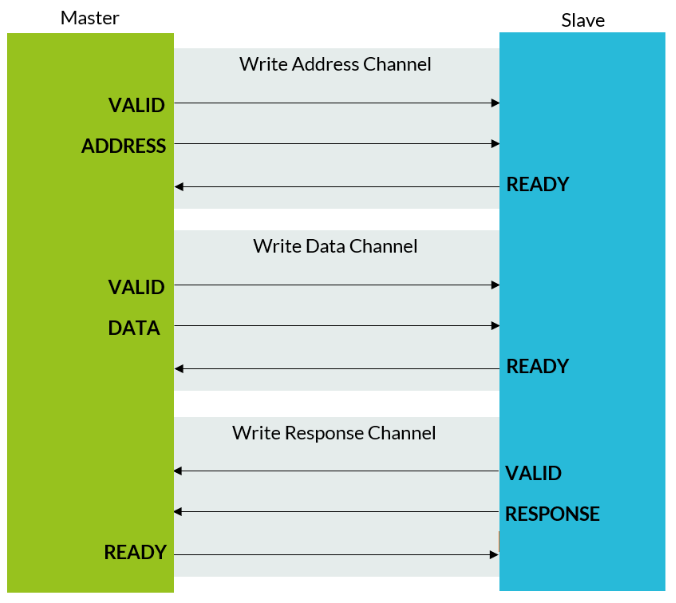

axi协议是两个接口之间的点对点的协议,主要是有5个通道。

主机在写地址(AW)通道上发送地址,并在写数据(W)通道上将数据传输到从机。

从机将接收到的数据写入指定地址空间。从机完成写操作,它将在写响应(B)通道上向主机发送信号。

主机在读地址(AR)通道上发送它想要读取的地址。

从机通过读取数据(R)通道将数据从请求的地址发送到主机。

从机还可以在读数据(R)通道上返回错误消息。例如,如果地址无效,或数据损坏,或访问没有正确的安全权限,则会发生错误。

每个通道都是单向的,因此需要一个单独的写响应通道将响应传递回主机。然而,不需要读响应通道,因为读响应作为读数据通道的一部分被传递。

使用单独的地址和数据通道进行读写传输有助于最大限度地提高接口带宽。在读取和写入通道的群组之间不存在时序关系。这意味着读取序列可以与写入序列同时发生。这五个通道中的每一个都包含若干信号,并且每个通道中的所有这些信号具有如下前缀:

axi协议的主要特点

1.独立的读写通道

2.多个数据项

3.地址和数据之间没有严格的时序关系

4.支持非对齐数据传输

5.无序事务完成

6.基于起始店址的突发事务。

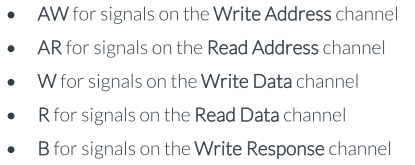

传输是一次信息交换,包括一次VALID和READY握手。下图显示了一个传输:

一个事务是一个完整的突发传输,包含一个地址传输、一个或多个数据传输,以及一个响应传输(对于写序列)。下图显示了一个事务:

读写握手必须遵守以下规则:

在断言VALID之前,源不能等待READY被断言。发送放不能等待READY信号发送方必须无条件先(或同时)表明数据有效性(VALID),而接收方可以自由决定何时准备好(READY)。这种设计确保了协议的确定性和无死锁,同时支持高性能的并行数据传输。理解这一点对正确实现AXI接口至关重要。

目的地可以在断言READY之前等待VALID被断言。axi协议赋予接收方对READY信号的完全控制权:

这些规则意味着READY可以在VALID之前或之后断言,甚至可以同时断言。

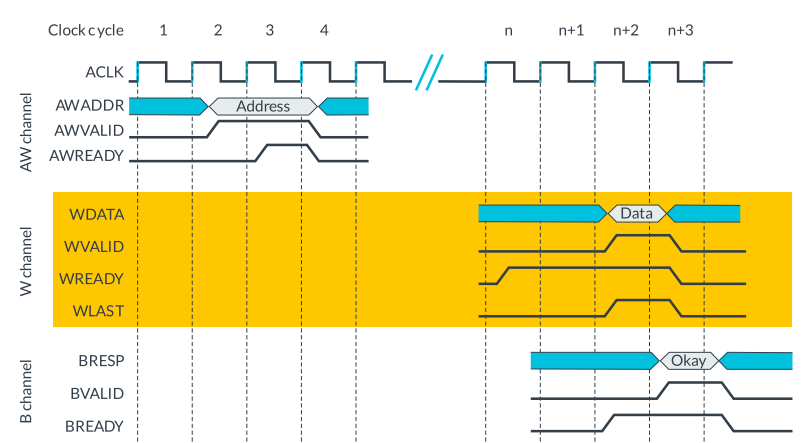

主机将地址置于AWADDR上,并在时钟周期2中置位AWVALID。2.从机在时钟周期3中置位AWREADY,以指示其接收地址值的能力。3.握手在时钟周期4的上升沿完成。

数据传输具有以下事件序列:1.从机在时钟周期n内等待WREADY设为高电平的数据。2.主机将数据放在WDATA总线上,并在时钟周期n+2中置位WVALID。3.握手在时钟周期n+3的上升沿完成。

写入响应具有以下事件序列:1.主程序断言BREADY。2.从设备驱动BRESP以指示写事务的成功或失败,并断言BVALID。握手在时钟周期n+3的上升沿完成。、

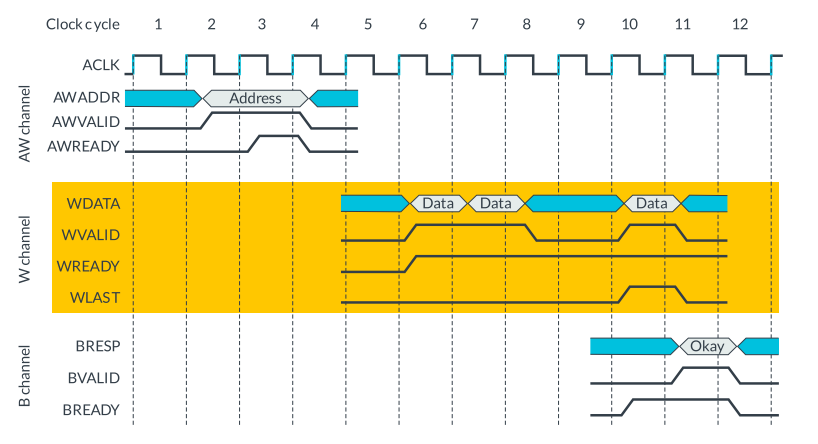

多个数据项

在这种情况下,AW通道表示三次传输的序列,在W通道上,我们看到三次数据传输。主机将WLAST驱动为高电平,以指示最终的WDATA。这意味着从设备可以对数据传输进行计数,也可以只监视WLAST。一旦接收到所有WDATA传输,从机在B通道上给出单个BRESP值。单个BRESP覆盖整个突发。如果从设备确定任何传输包含错误,则它必须等到整个突发完成后才能通知主设备发生错误。

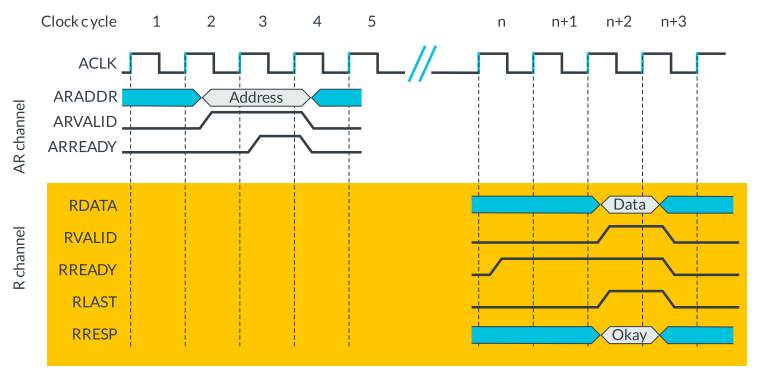

读取单个项

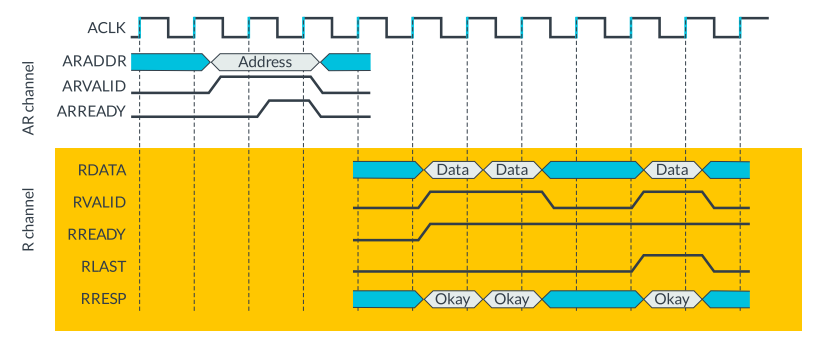

握手具有以下事件序列:1.在时钟周期2中,主机在ARADDR上向从机传送读取地址,并置位ARVALID。2.在时钟周期3中,从机置位ARREADY,以指示它已准备好接收地址值。握手在时钟周期4的上升沿完成。接下来,在Read(R)通道上,从机将数据传输到主机。下图显示了数据传输过程:

数据传输握手具有以下事件序列:1.在时钟周期n中,主机通过置位RREADY来指示其正在等待接收数据。2.从机在时钟周期n+2内检索数据并将其置于RDATA上。在这种情况下,因为这是单个数据事务,所以从机还将RLAST信号设置为高。与此同时,从机使用RRESP向主机指示读取事务的成功或失败,并置位RVALID。3.由于主机已置位RREADY,因此握手在时钟周期n+3的上升沿完成。

读取多个数据项

在本例中,我们在AR通道上传输单个地址,以传输多个数据项,以及相关的突发宽度和长度信息。这里,AR通道表示三次传输的序列,因此在R通道上,我们看到从机到主机的三次数据传输。在R通道上,从机将数据传输到主机。在本例中,主机正在等待数据,如RREADY设置为高电平所示。从机驱动有效的RDATA并为每次传输置位RVALID。读事务和写事务之间的一个区别是,对于读事务,对于事务中的每个传输都有RRESP响应。这是因为,在写事务中,从机必须在B通道上将响应作为单独的传输发送。在读事务中,从机使用相同的通道将数据发送回主机,并指示读操作的状态。如果在传输过程中个存在错误,必须将完成该完整的指示长度,不存在提前结束突发的情况。

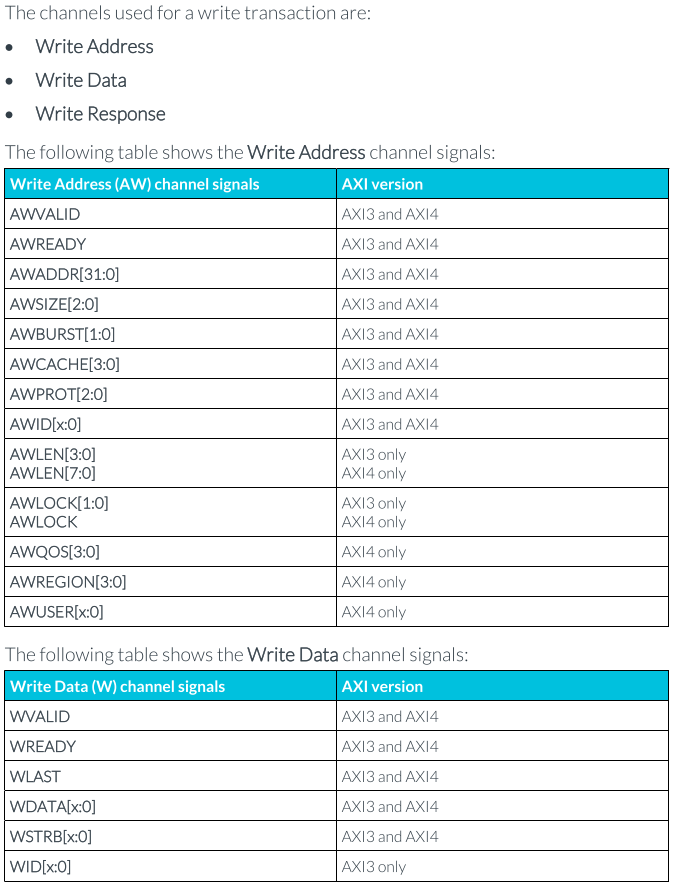

写通道信号

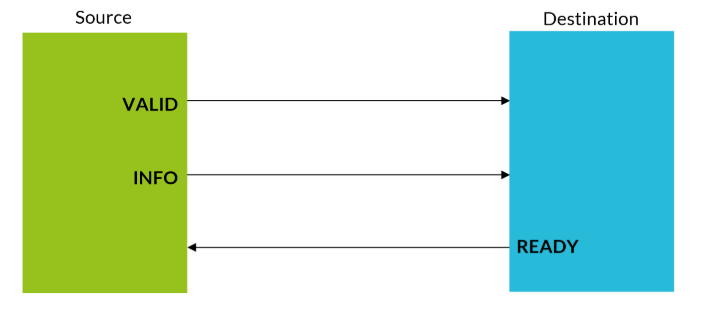

每个通道中的所有信号都具有相同的前缀:

AW表示写地址通道

W表示写数据通道

B表示写响应通道

对于写通道,AXI3协议和AXI4协议之间存在一些差异:

对于写地址通道,AXI4协议中AWLEN信号更宽。因此,AXI4能够产生比AXI3突发更长的。

AXI4将AWLOCK信号减少到单个位,以仅适应独占传输,因为不支持锁定传输。

AXI4将AWQOS信号添加到AW通道。该信号支持AXI4协议中的服务质量(QoS)概念。

AXI4将AWREGION信号添加到AW通道。该信号支持从区域,从区域允许来自单个物理从接口的多个逻辑接口。

AXI4从W通道中移除WID信号。这是因为不再允许写入数据重新排序。

AXI4将WUSER用户定义的信号添加到每个通道。

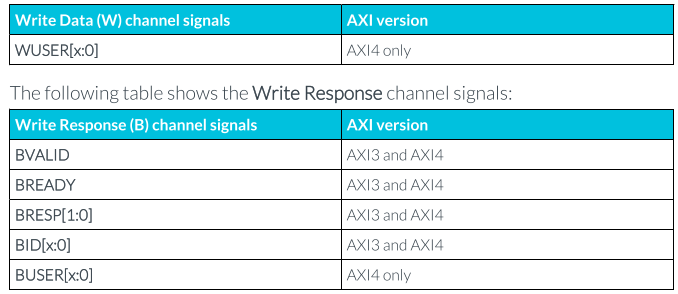

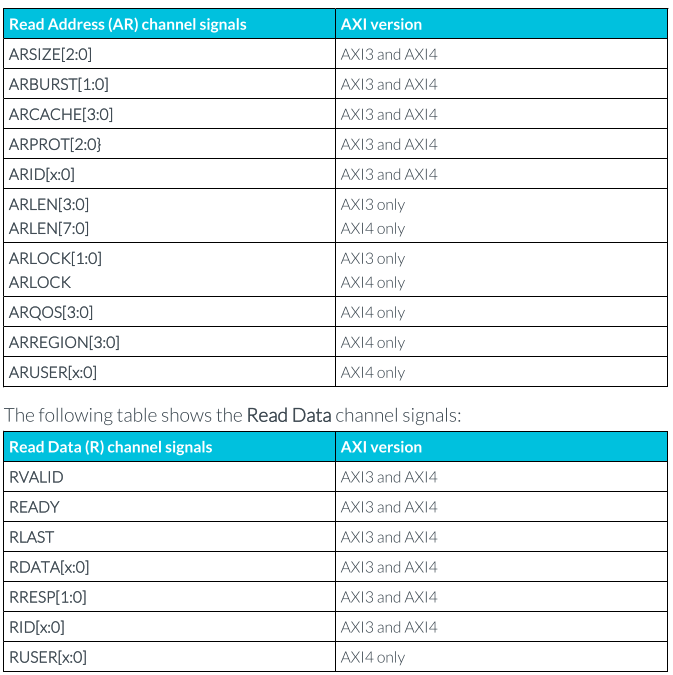

读通道信号

每个通道中的所有信号都有相同的前缀:

每个通道中的所有信号都有相同的前缀:

AR表示读地址通道

R表示读数据通道对于读通道

AXI3协议和AXI4协议之间存在一些差异:

对于AXI4协议,读地址长度信号ARLEN更宽。因此,AXI4能够生成比AXI3更长的读取突发。

AXI4将ARRECT信号减少到单个位,以仅适应独占传输,因为不支持锁定传输。

与写通道信号一样,服务质量和从区域的概念适用于读事务。它们在AR通道中使用ARQOS和ARREGION信号。

AXI4将用户定义的信号添加到两个读取通道。