实验六 时序逻辑电路设计实验(设计分析)

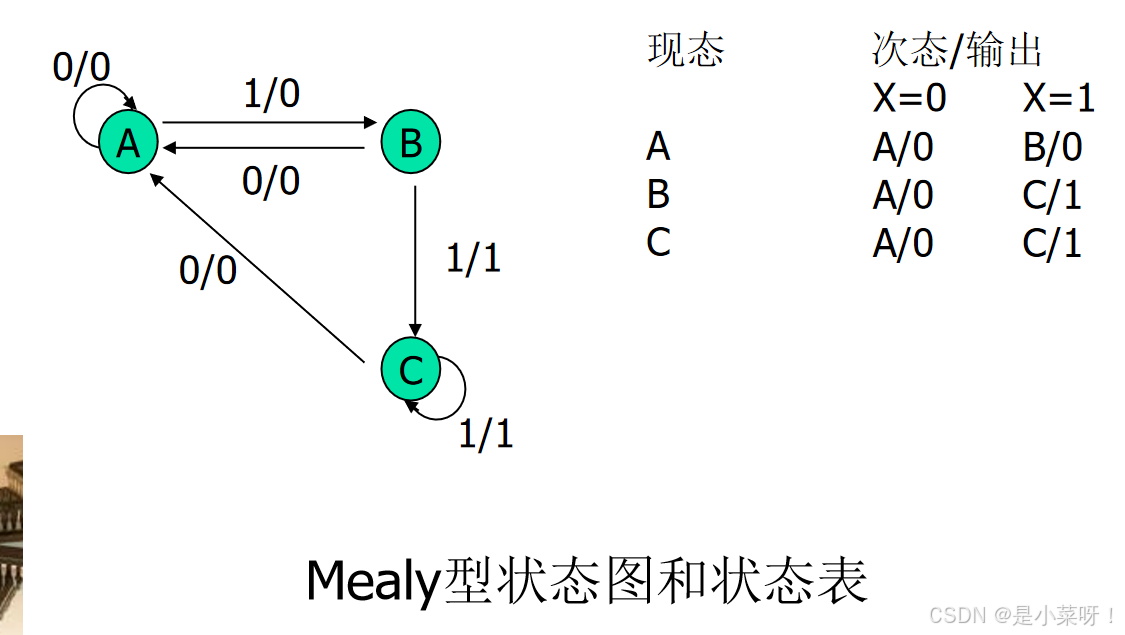

设计一个“11”序列检测电路:它有一个输入X,当接收到的序列为11,则在上述序列输入最后一个1的同时,电路输出Z=1,否则输出为0。

一、同步时序电路设计的一般步骤

第一步 根据逻辑要求,作出原始状态图和状态表。

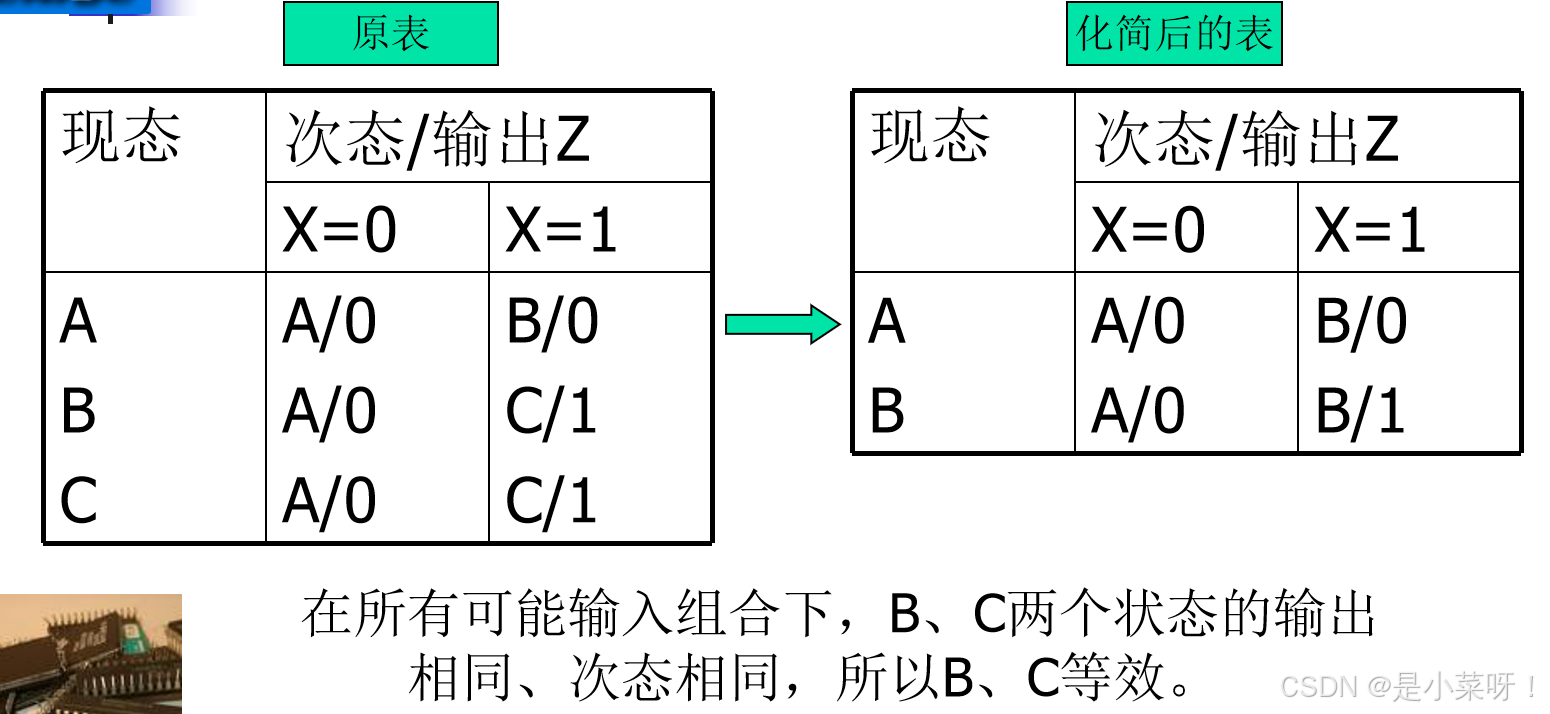

第二步 状态简化

第三步 状态编码

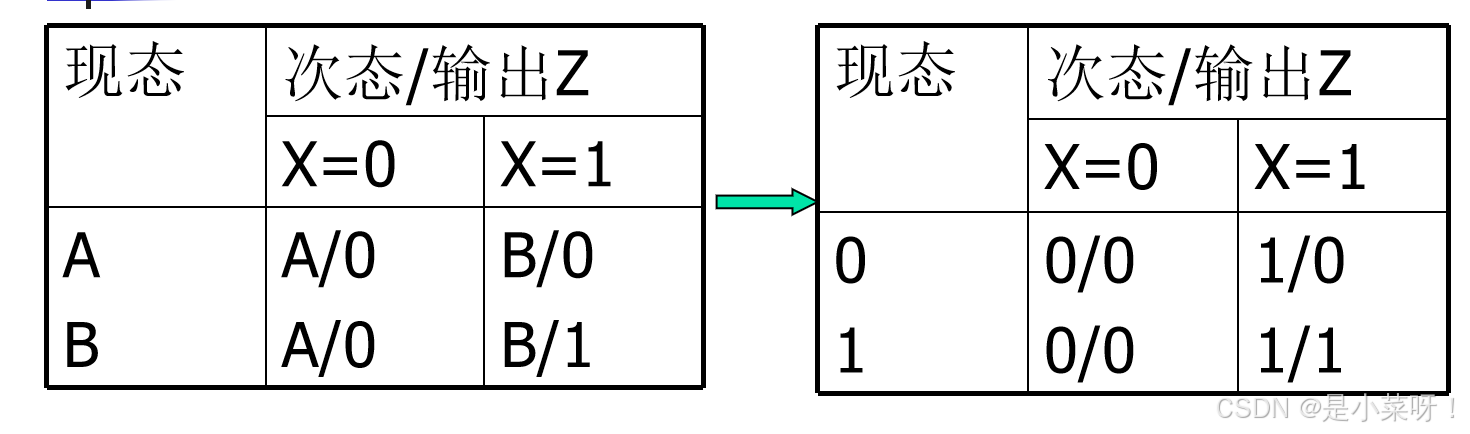

把状态中用字母和数字表示的状态用一组二进制代码来代替,这就叫做状态编码,或者叫做状态赋值,也称状态分配。 多个状态的相邻应遵守相关的规则 本实验由于只有两个状态,不考虑相邻分配 状态中出现次数最多的状态分配为逻辑0,这样A为0,B为1。

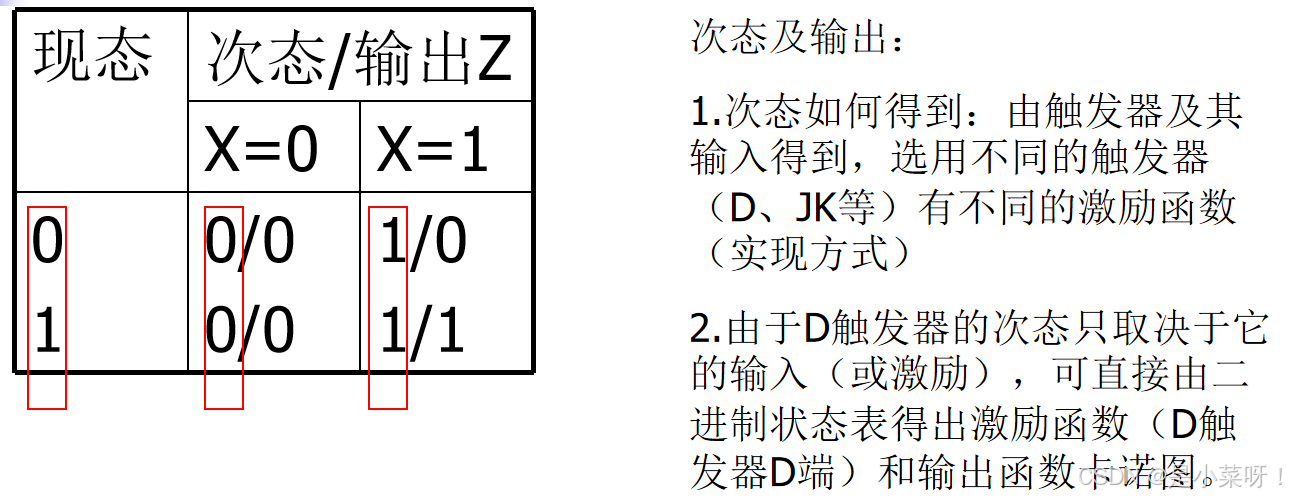

状态分配后的二进制状态表

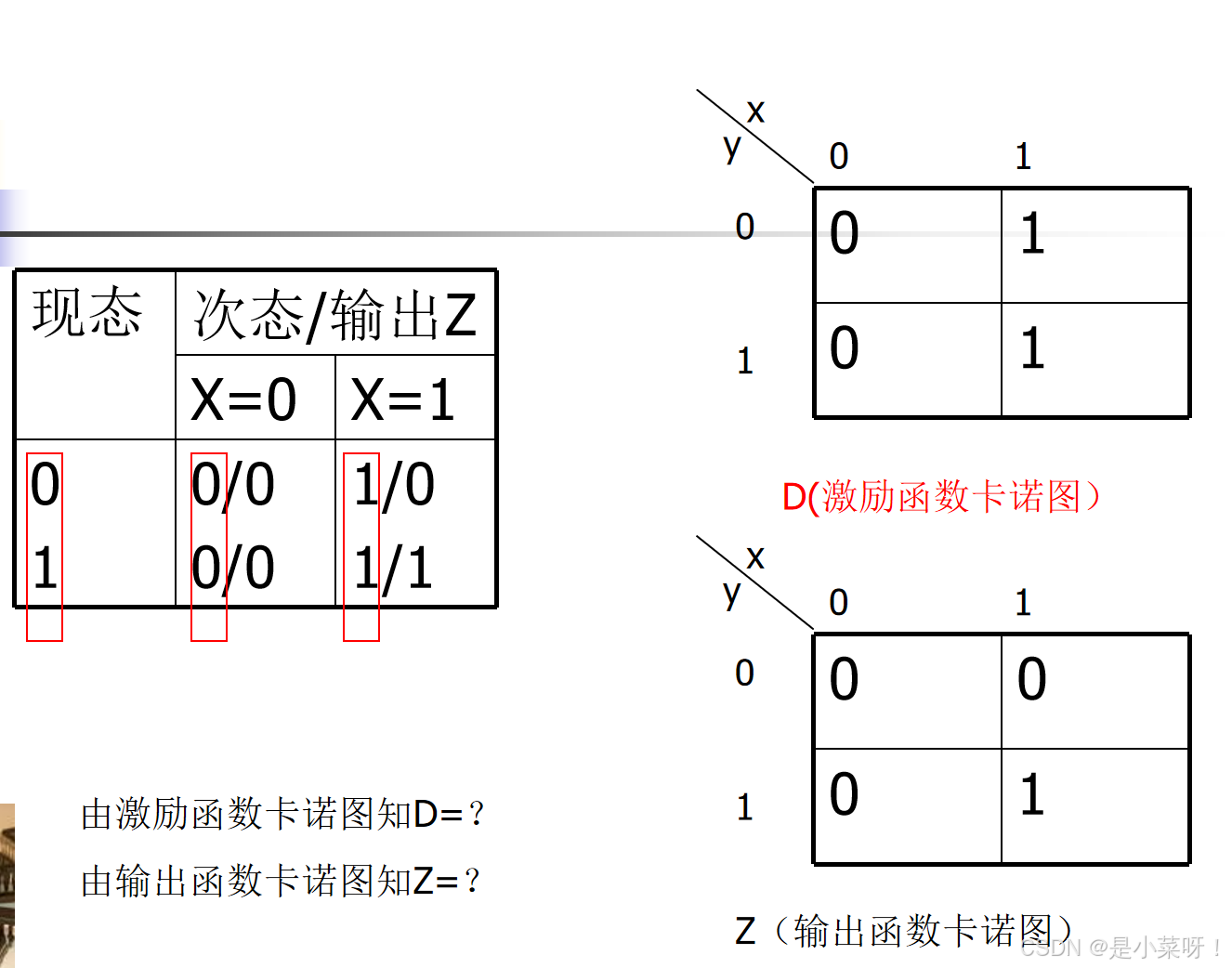

第四步 求出激励函数和输出函数表达式

由激励函数卡诺图知D=X

由输出函数卡诺图知Z=xy

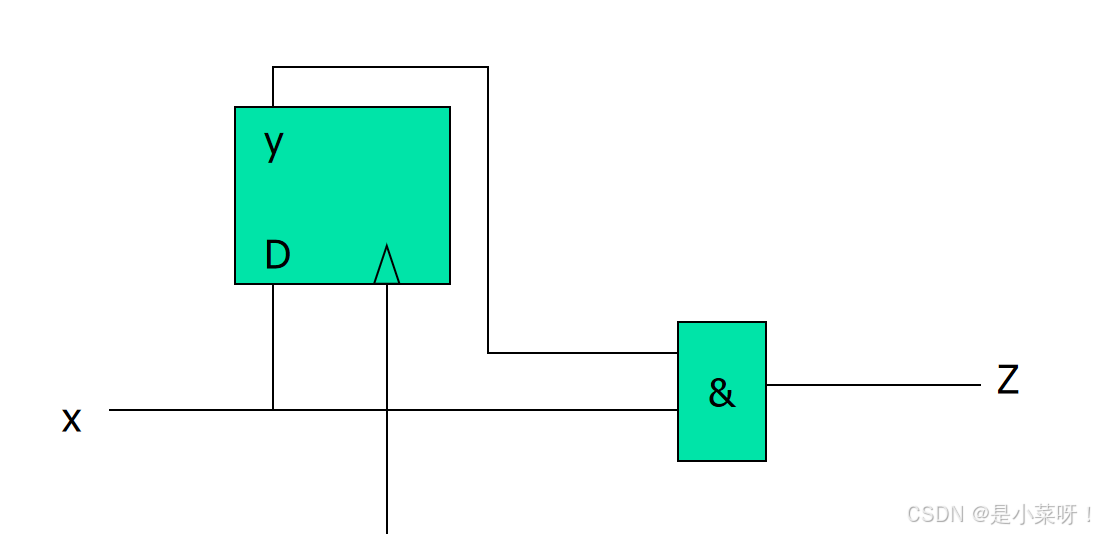

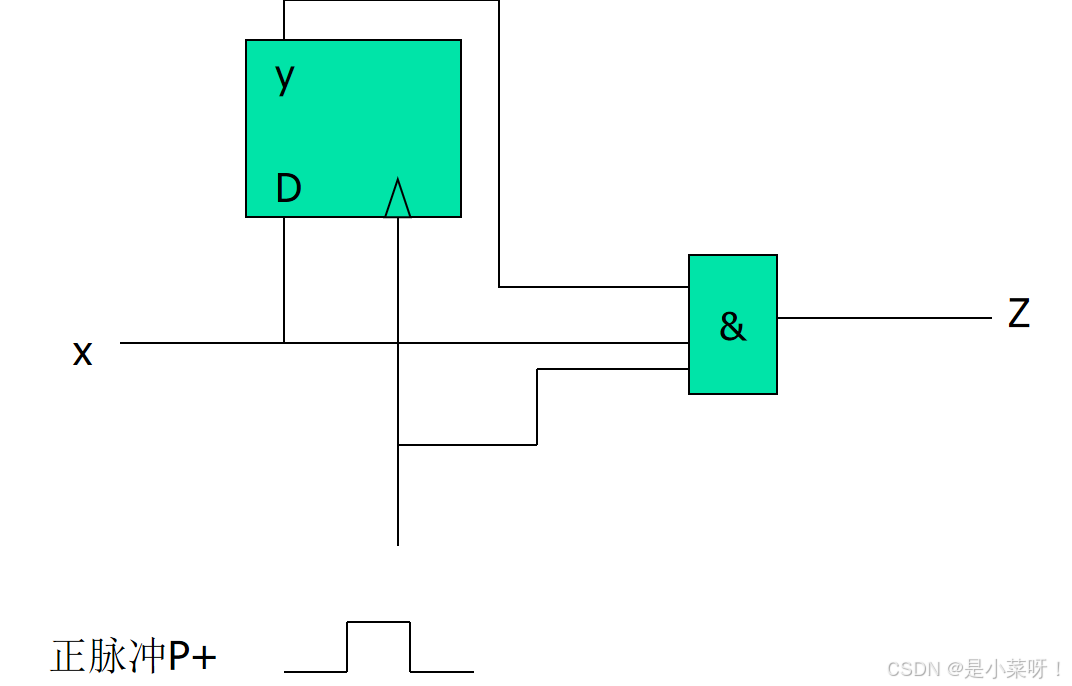

第五歩 画出逻辑电路图

方案(在与门输出端加时钟控制P+)?

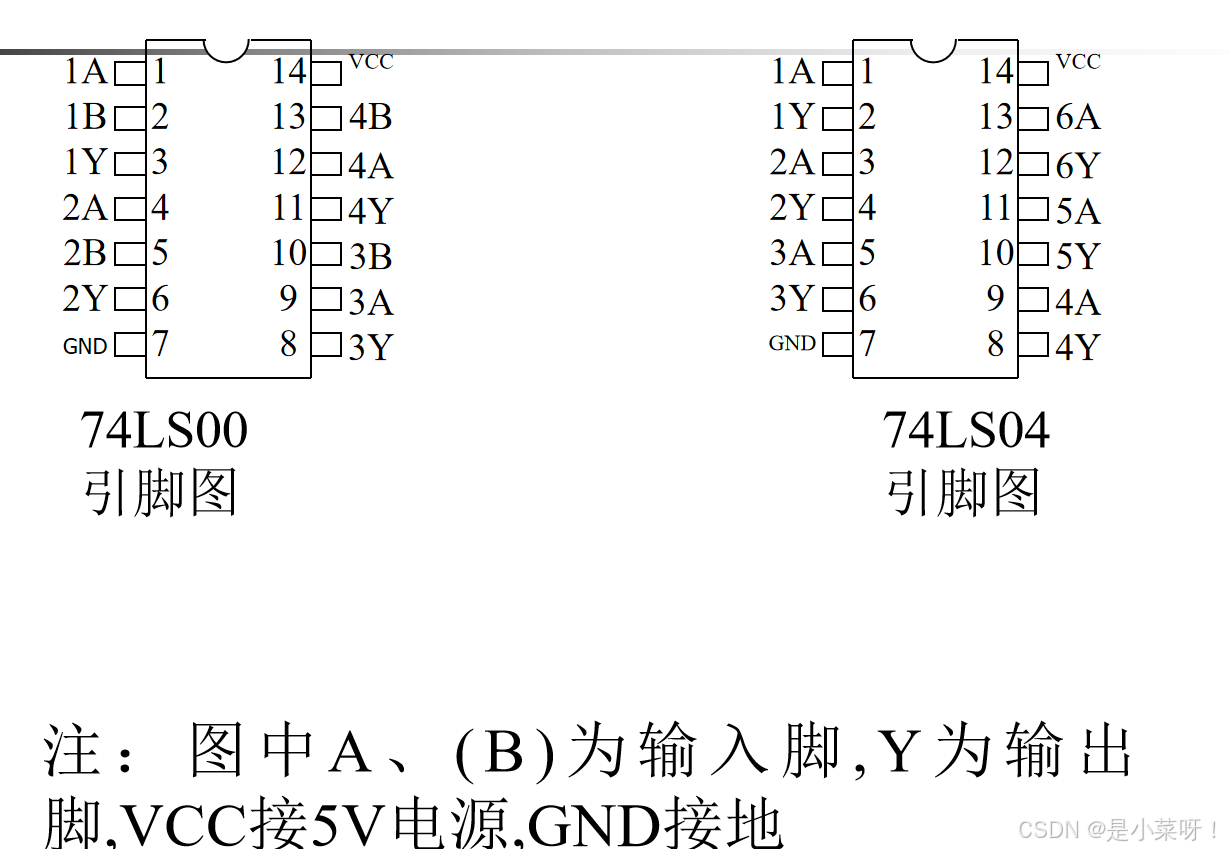

二、本实验提供以下芯片选择使用

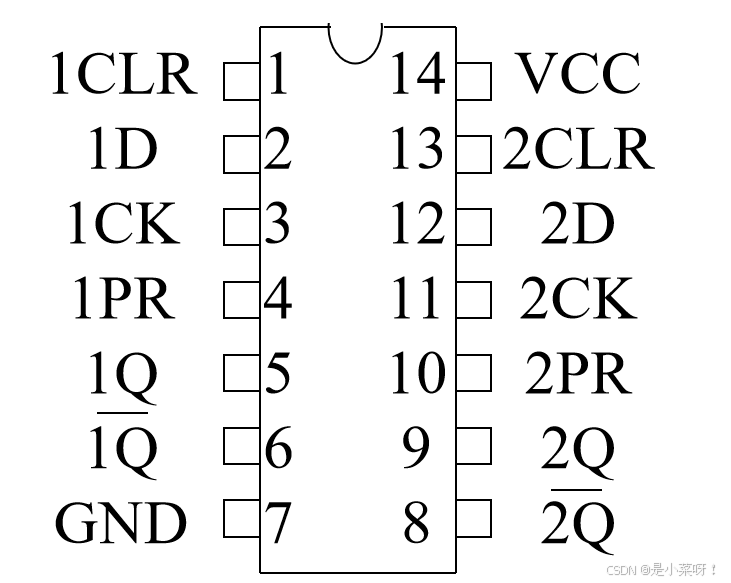

1.双D触发器74LS74引脚图

2.74LS00与74LS04