FPGA从零到一实现FOC(一)之PWM模块设计

一.简介

哈喽,大家好,从今天开始正式带领大家从零到一,在FPGA平台上实现FOC算法,整个算法的框架如下图所示,如果大家对算法的原理不是特别清楚的话,可以先去百度上学习一下,本教程着重介绍实现过程,弱化原理的介绍。那么本文将从PWM模块开始进入FOC算法中去。

配套硬件链接

二. PWM模块设计

我们知道有些驱动芯片是需要输入互补的PWM,例如FD6288,而有些驱动芯片则只需要输入PWM,芯片内部会自动将其转为互补的PWM进行工作,例如DRV8313和MP6540。单路FOC开发板使用的是MP6540,多路电机驱动板使用的是FD6288,因此设计的PWM模块需要兼容这两种模式。

1. 模块端口信号

模块端口信号如下所示,命名和工作模式借鉴了STM32定时器的工作方式。

module timer_top #(parameter DEFAULT_ARR = 16'd1500 , //5000parameter DEFAULT_CCR = 16'd750 , //2500parameter COUNT_MODE = "UP" , // UP DOWN CENTREparameter TRIG_ENABLE = "ENABLE" , // ENABLE DISABLEparameter PWM_OUT = "NONE" , // NONE P PNparameter PWM_OUT_MODE = "MODE1" , // MODE1 MODE2parameter PWM_DEATH_TIME = 3'd0 // 0 ~ 10 sys_clk

)(input sys_clk_i , input sys_rst_n_i ,input pwm_clk_200M_i ,input timer_wr_type_i ,input timer_write_en_i ,input[15:0] timer_write_data_i ,input timer_read_en_i ,output[15:0] timer_read_data_o ,output timer_trig_o ,output timer_pwm_o ,output reg timer_pwm_n_o

);

首先给大家介绍一下端口参数

- DEFAULT_ARR: 默认的定时器计数周期。

- DEFAULT_CCR: 默认的定时器比较输出值。

- COUNT_MODE: 定时器工作模式,分为向上计数、向下计数和中心计数三种模式,这是和STM32的三种模式保持一致。

- TRIG_ENABLE:中断输出是否使能,当计数器计数到CCR寄存器值的时候,是否输出一个中断信号。

- PWM_OUT: PWM输出,分为三种模式,其一是不输出,其二是只输出一路PWM,其三是输出互补两路PWM。

- PWM_OUT_MODEL: PWM输出的模式,也就是但计数器小于CCR的时候,是输出高电平,还是输出低电平。

- PWM_DEATH_TIME: 死区时间,最大为10个时钟周期,也就是50ns,加上芯片内部基本上都内置了死区补偿,这个时间是够用了的。

然后就是端口信号

-

sys_clk_i,sys_rst_n_i: 100Mhz系统时钟和系统复位

-

pwm_clk_200M_i: PWM输出的参考时钟,为200Mhz,这个时钟频率越高,PWM的分辨率也就越高。

-

timer_trig_o: 中断信号输出

-

timer_pwm_o,timer_pwm_n_o : PWM信号输出

-

其他:动态调整定时器的计数周期ARR和比较值CCR,从而可以调整PWM的频率和占空比,实际使用的过程中,只会调整占空比。

2. 设计细节

PWM模块设计原理比较简单,其中有两点需要注意一下,这两点中好了 ,设计起来就毫无压力~。

- 跨时钟同步: 定时器时钟频率为200Mhz,而系统时钟频率为100Mhz,模块只会涉及到中断信号的同步,定时器时钟域同步到系统时钟域下,快时钟域同步到慢时钟域下,也是同步场景中最为常见的一种,这里直接将脉冲信号作为使能信号,对另外一个信号进行取反,然后检查其边沿即可实现同步。

always@( posedge pwm_clk_200M_i or negedge sys_rst_n_i ) beginif( sys_rst_n_i == 1'b0 )timer_trig_pluse <= 1'b0;else if( TRIG_ENABLE == "ENABLE" && CNT == CCR_SHADOW )timer_trig_pluse <= ~timer_trig_pluse;elsetimer_trig_pluse <= timer_trig_pluse;

end

always@( posedge sys_clk_i or negedge sys_rst_n_i ) beginif( sys_rst_n_i == 1'b0 ) begintimer_trig_pluse_d0 <= 1'b0;timer_trig_pluse_d1 <= 1'b0;endelse begintimer_trig_pluse_d0 <= timer_trig_pluse;timer_trig_pluse_d1 <= timer_trig_pluse_d0;end

end

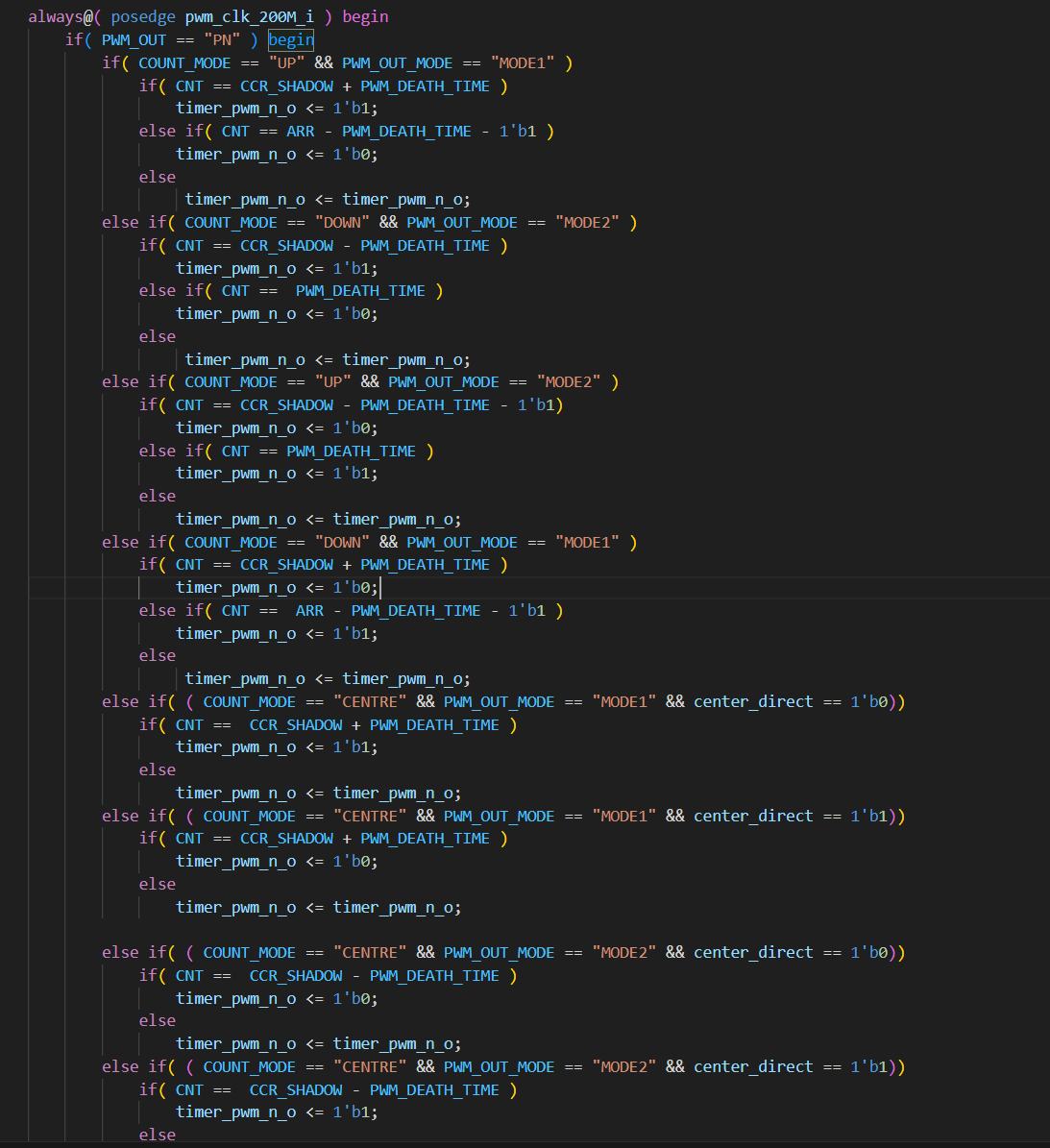

- 互补PWM输出死区控制:死区控制的目的是为了防止短时间内两路PWM输出同时为高的情况发生,从而导致上下臂同时导通,了解了这个之后,就只需要将互补PWM输出信号中,输出为高电平的那个信号提前拉低即可,在实现的过程中要结合配置的定时器模式进行输出,会涉及到多重判断的情况,如下图所示,大家可以通过多级判断,去优化这部分时序。

最后给大家展示一下仿真结果