5、ZYNQ PL 点灯--流水灯

目录

1、 概述

2 、硬件电路

3、 新建 VIVADO 工程

4、 添加工程文件

6、编写流水灯功能的Verilog代码

7 、添加管脚约束文件

8、 RTL 仿真

8.1 添加仿真测试源码

8.2 仿真结果

9、 编译并且产生 bit 文件

10、 下载程序

11、实验结果

编辑12、总结

1、 概述

本章课程以大家熟悉的流水灯为例子,详细讲解了 VIVADO 软件的使用,包括创建 FPGA 工程,编写 Verilog代码,添加管脚约束,最后编译,下载 bit 文件到开发板测试。对于初学 XILINX FPGA 的读者请注意,bit 文件断电后就丢失了。如果实现上电能够启动程序,需要把 BIT 文件打包成 bin 或者 MCS 文件才可以。如果打包,固化到FLASH。由于是基础课程,读者一定不要停留在实现了功能的目的,而是要真正掌握代代码的编写能力,写出优秀的代码。即便是功能实现了,但是不同的代码也代表了不同的水平,作为编程者一定要时刻要求自己写出高水平的代码。

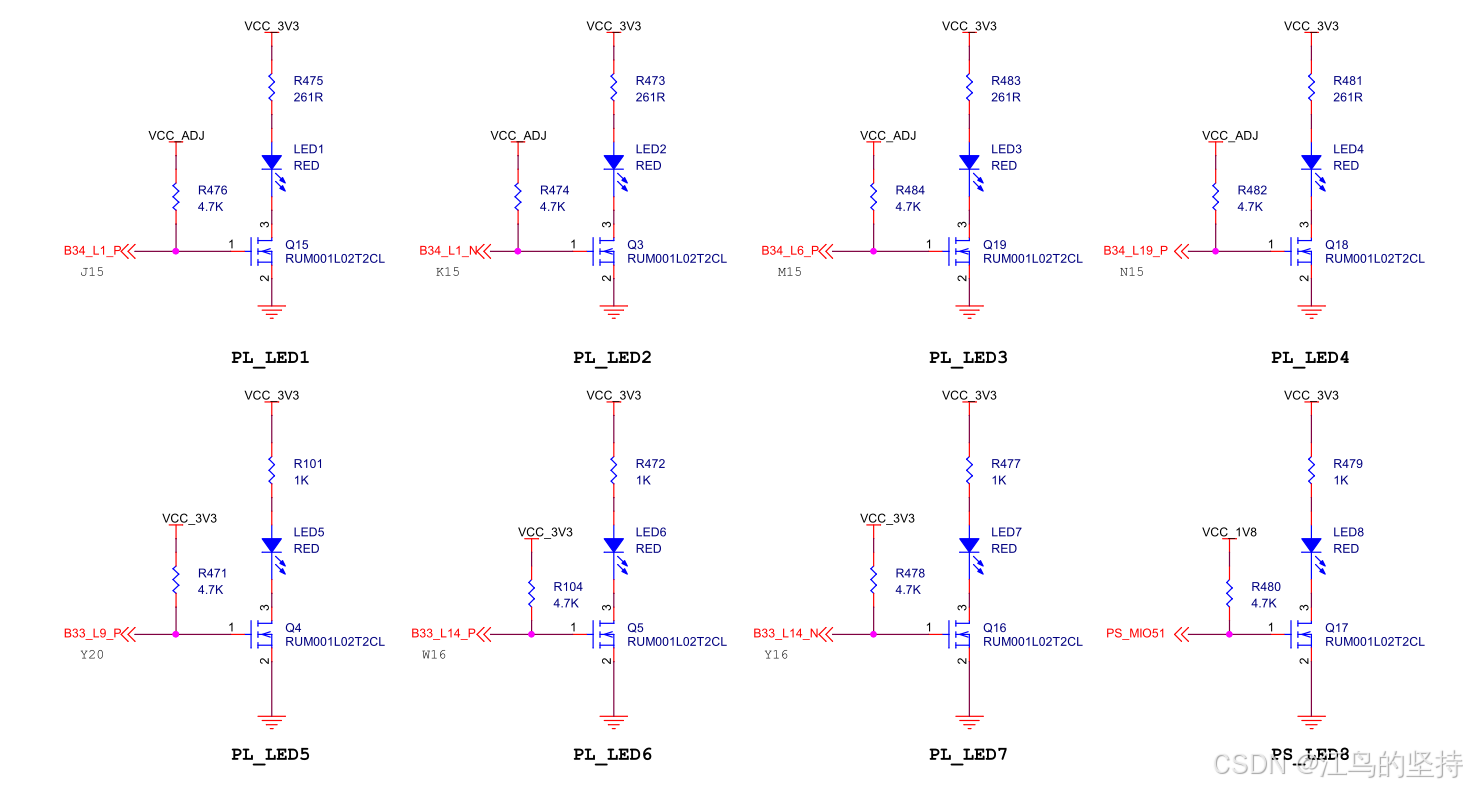

2 、硬件电路

上一节有提到,开发板使用的是米联客的Zynq 7020,开发板是由核心板和底板(扩展板)组成,LED是在底板上,中间由连接器把两个板子连接起来,所以引脚不是直接引到FPGA的引脚上。下面链接给出了完整的原理图,自行下载参考。

米联客Zynq7020核心板和底板原理图。

3、 新建 VIVADO 工程

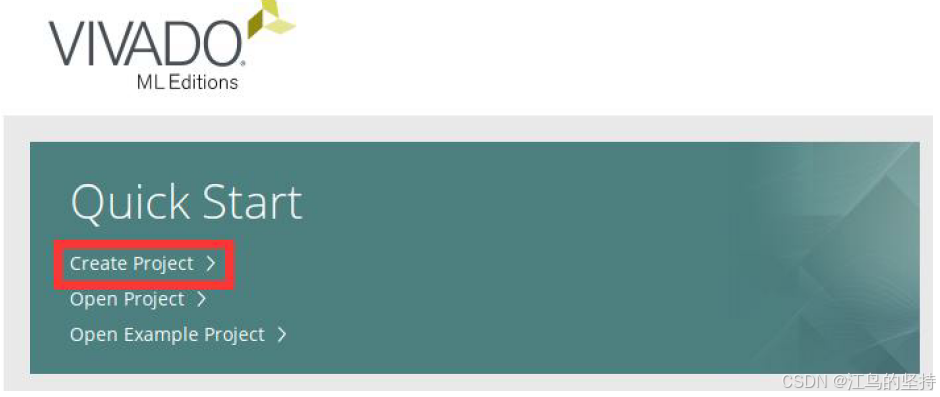

Step1:启动 VIVADO,单击 Create Project

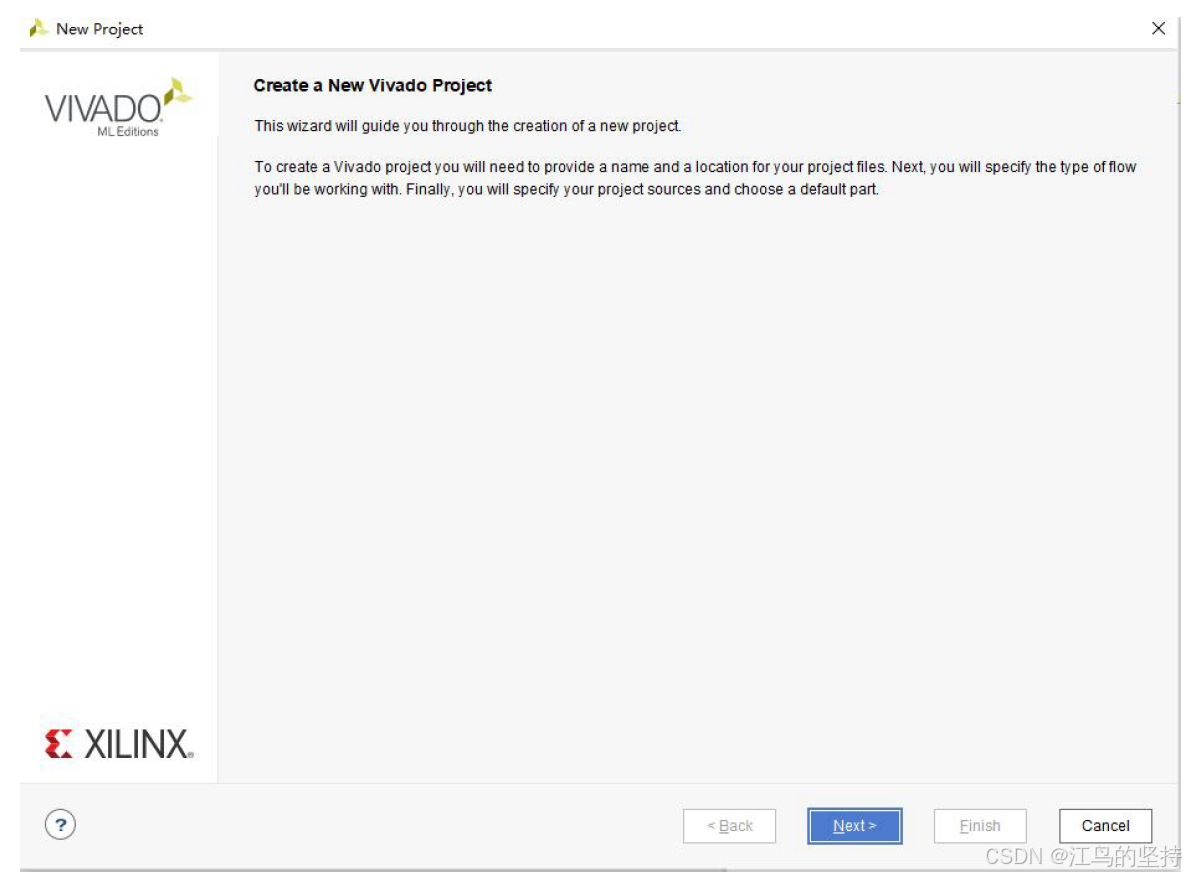

Step2:单击 NEXT

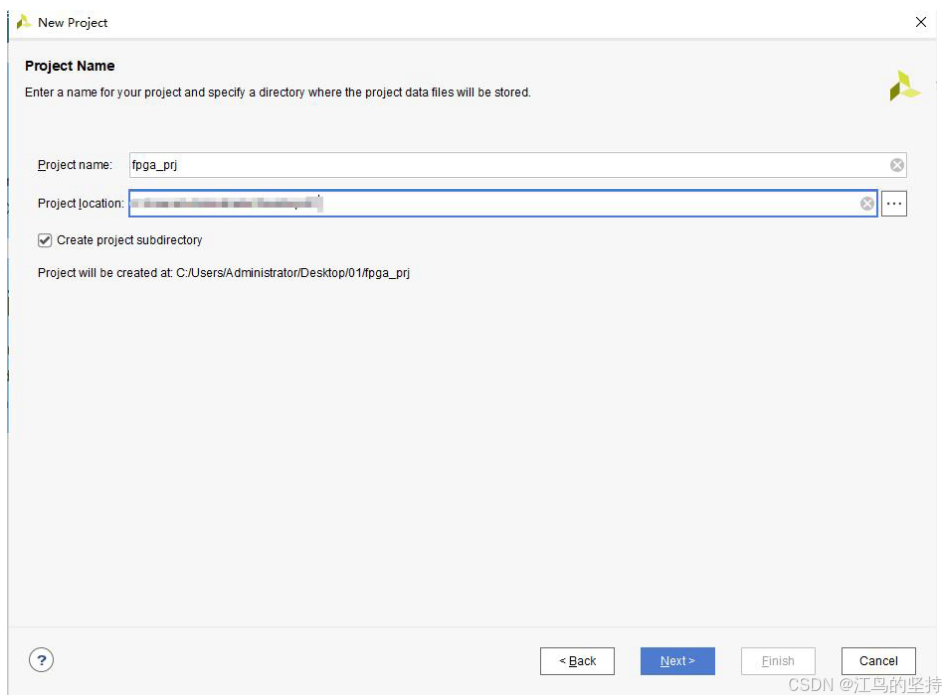

Step3:创建名为 fpga_prj 的工程

到对应的文件目录,文件路径自定义,不能有中文或非法字符,之后单击 NEXT

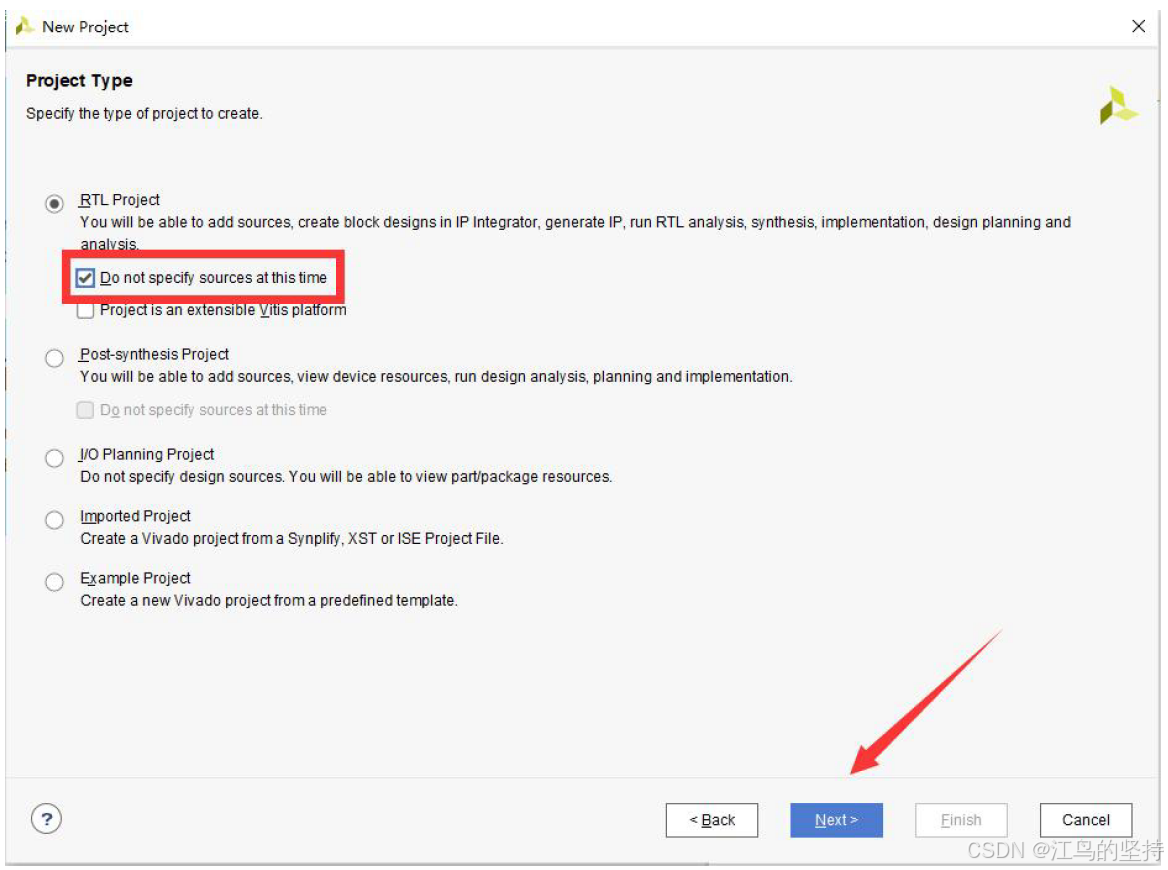

Step4:选择 RTL Project 并且勾选复选框,之后单击 NEXT

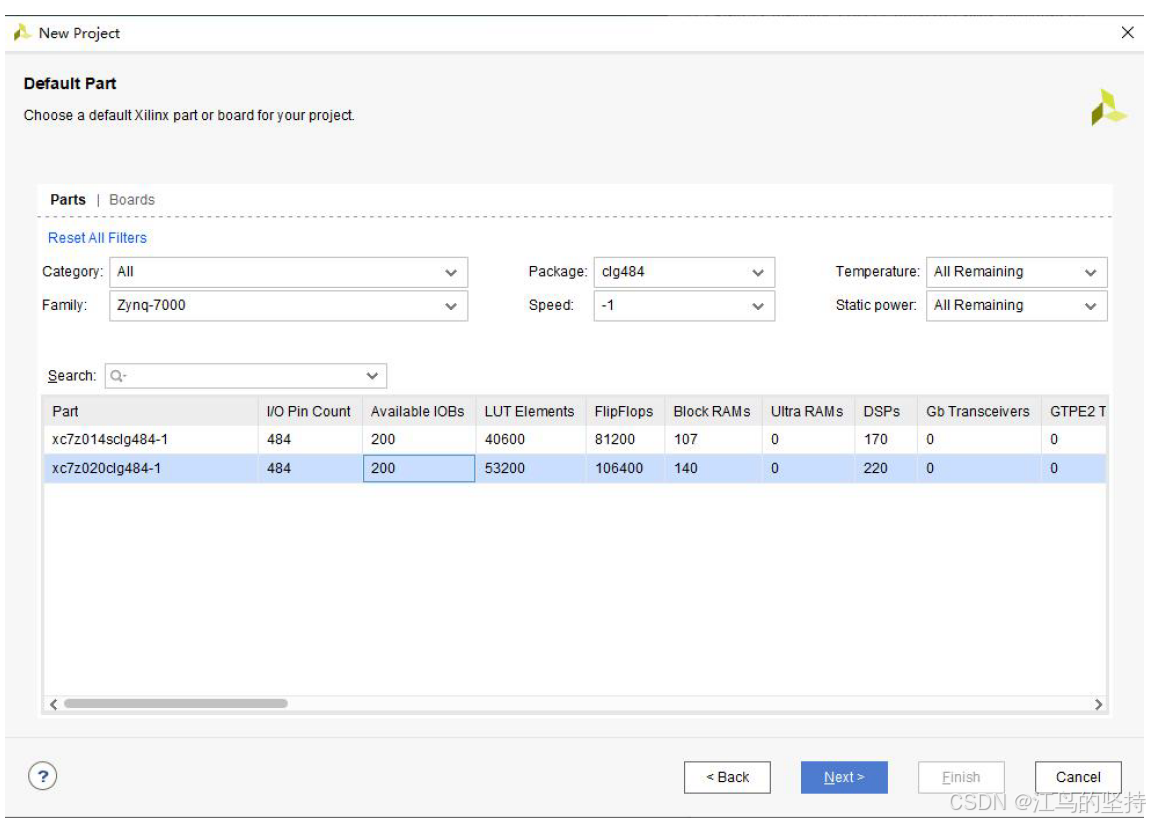

Step5:选择芯片的型号和封装速度等级:

核心板使用的芯片型号为 Zynq xc7z020clg484-1,clg484代表封装,-1为速率等级(-x,x数越大,速度越快)

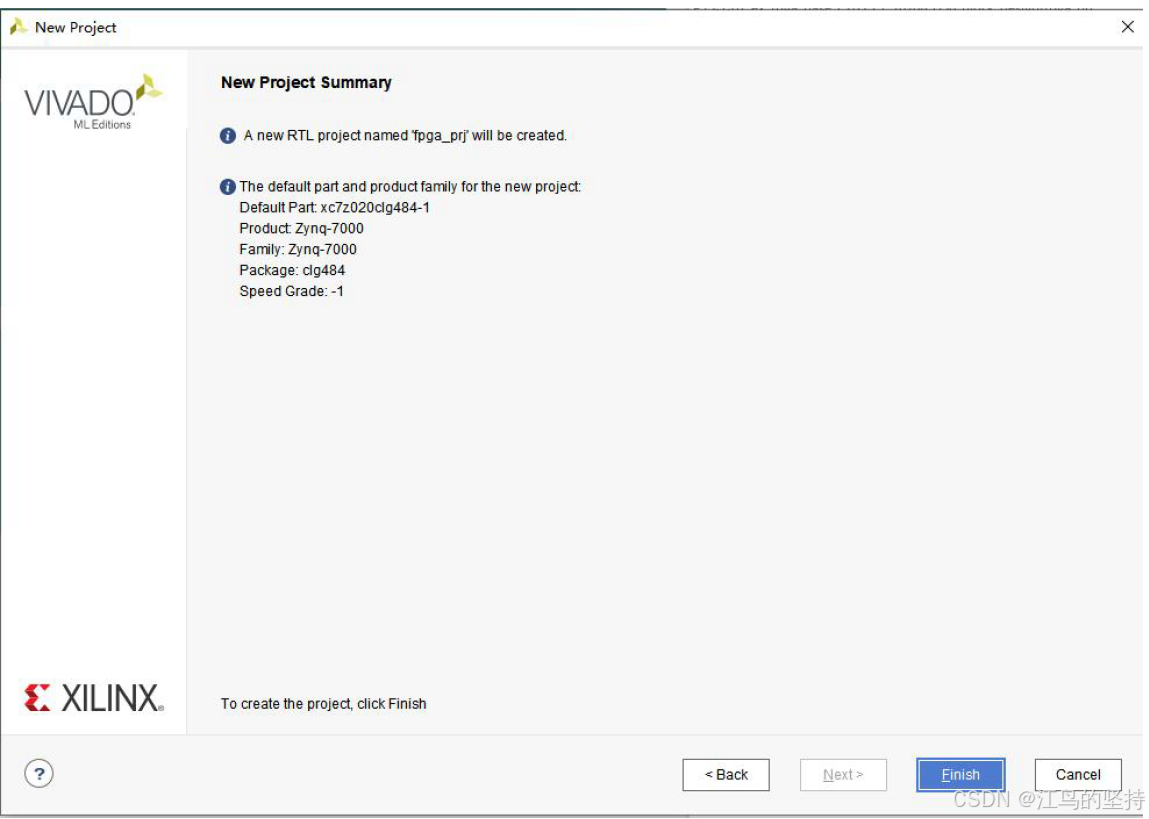

Step:6 单击 Finish 完成工程创建。

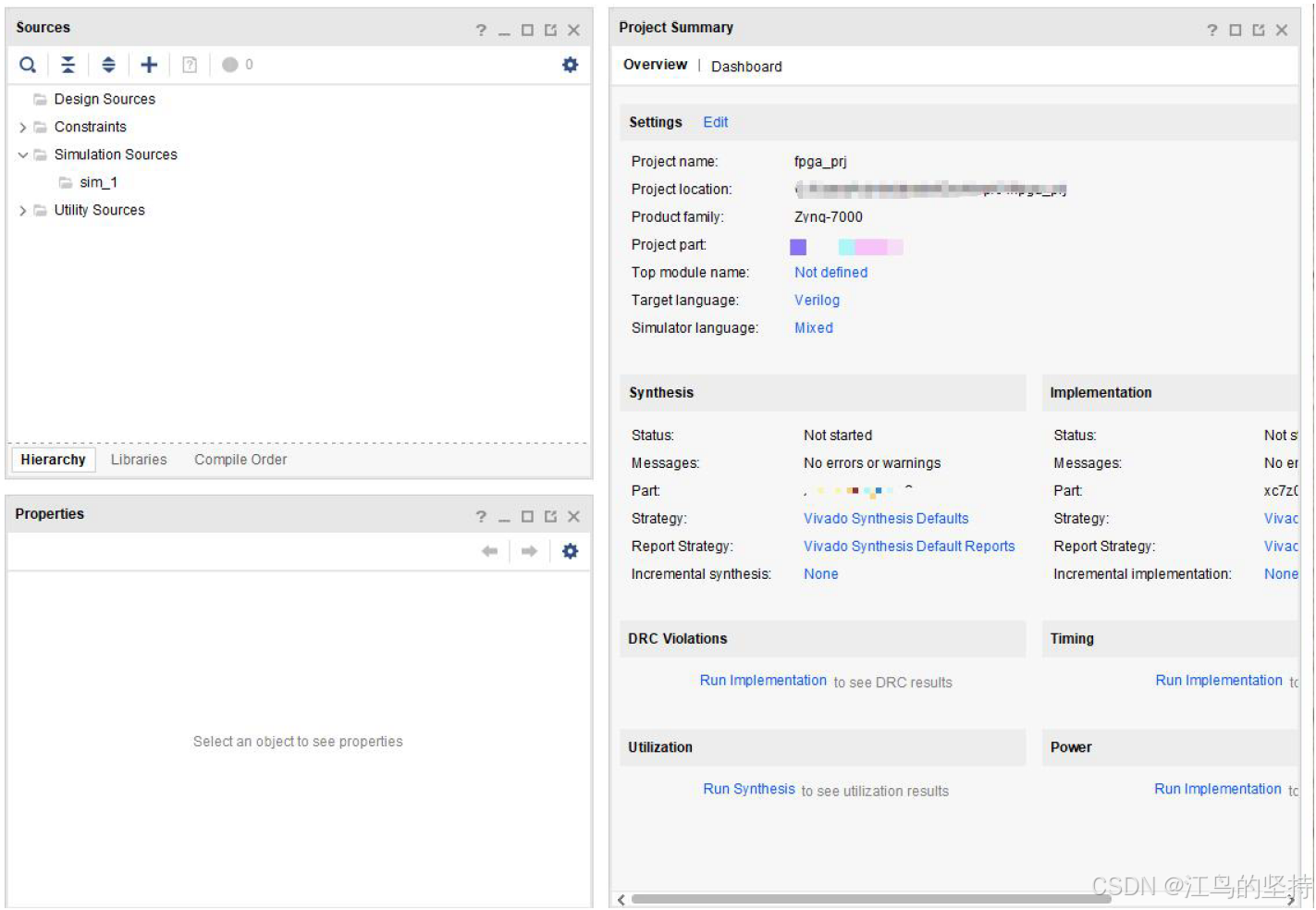

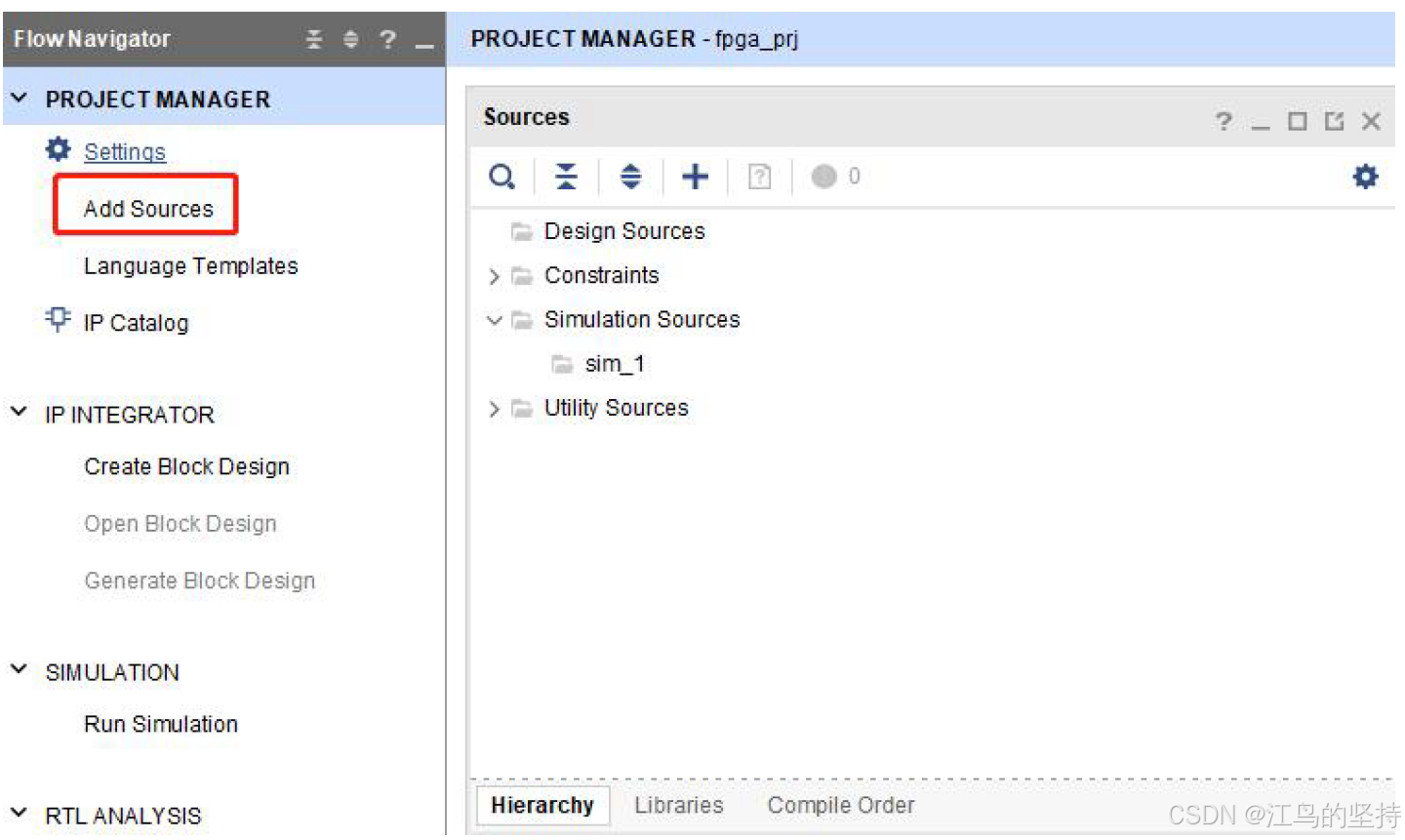

4、 添加工程文件

Step1:打开 VIVADO 软件

Step2:单击 Add Sources

Step3