如何抓取DP_AUX辅助通道数据

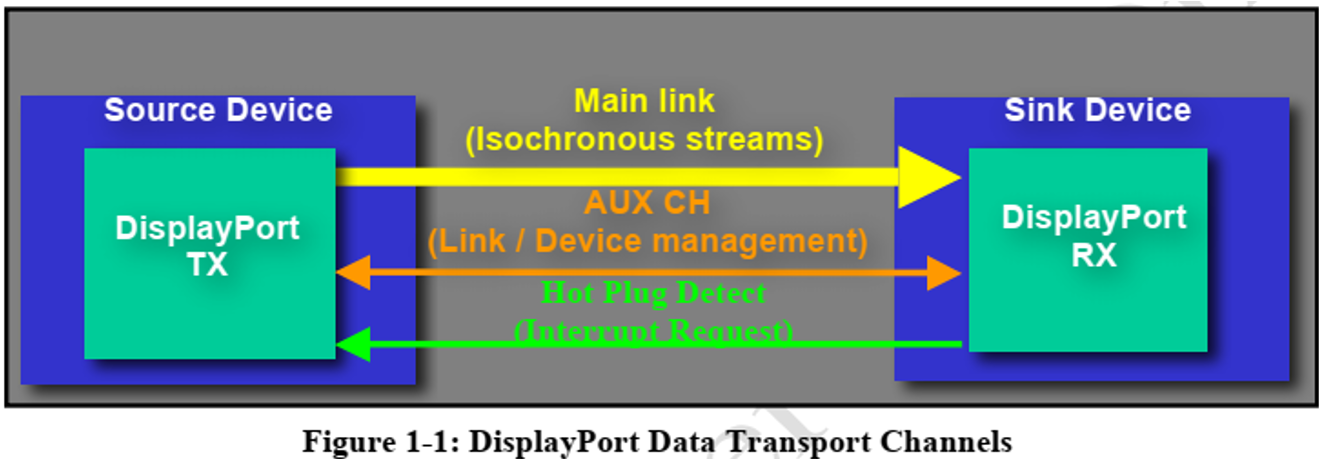

DisplayPort是数字式视频接口标准,包含影音传输的主要通道(Main Link)、辅助通道(AUX)、与热插拔(HPD)。

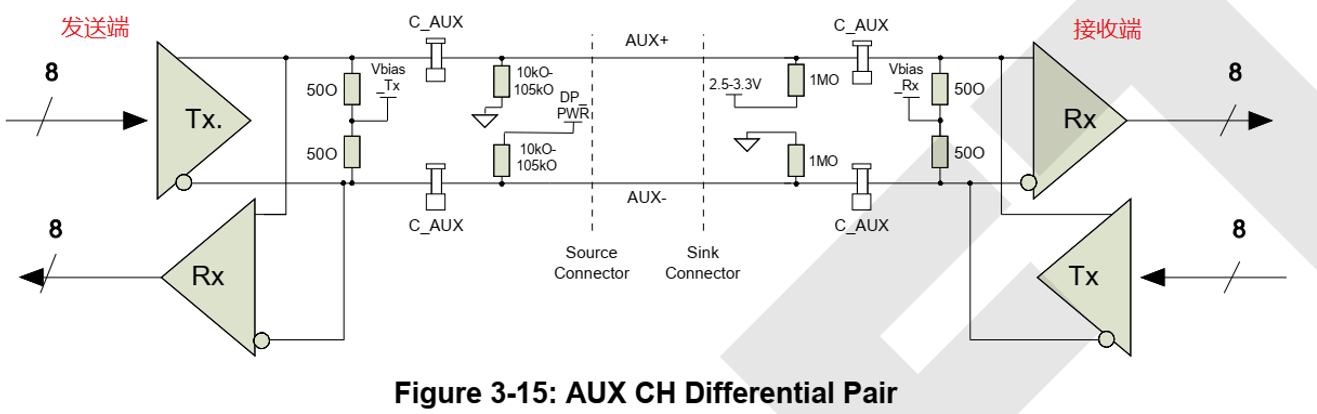

其中AUX:是一条独立双向半双工的传输通道,它也是一对差分信号线。其数据传输速率1Mbps,用来传输配置参数与指令。具体来说就是读取EDID和DPCD寄存器。

对于大多数DP和eDP接口,AUX通信是必须的,当然也有少数eDP屏可以不用AUX通信。在AUX通信控制之下,发送端和接收端完成Link Training链路训练,之后主链路的图像传输才能正常显示。

那么我们如何来抓取AUX通信数据进行分析呢?

1. 逻辑分析仪

目前市面大多逻辑分析仪都不带DP_AUX协议分析,好像只有皇晶的逻辑分析仪带DP_AUX协议分析。

不过皇晶逻辑分析仪分析DP_AUX只是按单端信号进行采集分析。如果有哪个逻辑分析仪能直接抓取DP_AUX差分信号分析就很方便了。

另外皇晶逻辑分析仪一般都很贵,如果有哪个便宜的逻辑分析仪能支持DP_AUX协议就最好了。

2. 采集方式

因为AUX信号是一对差分信号,如果直接用皇晶逻辑分析仪采集AUX的正端,信号摆幅非常小,通常只有几百毫伏。所以虽然可以采信号,但容易受干扰,采集信号不准确。

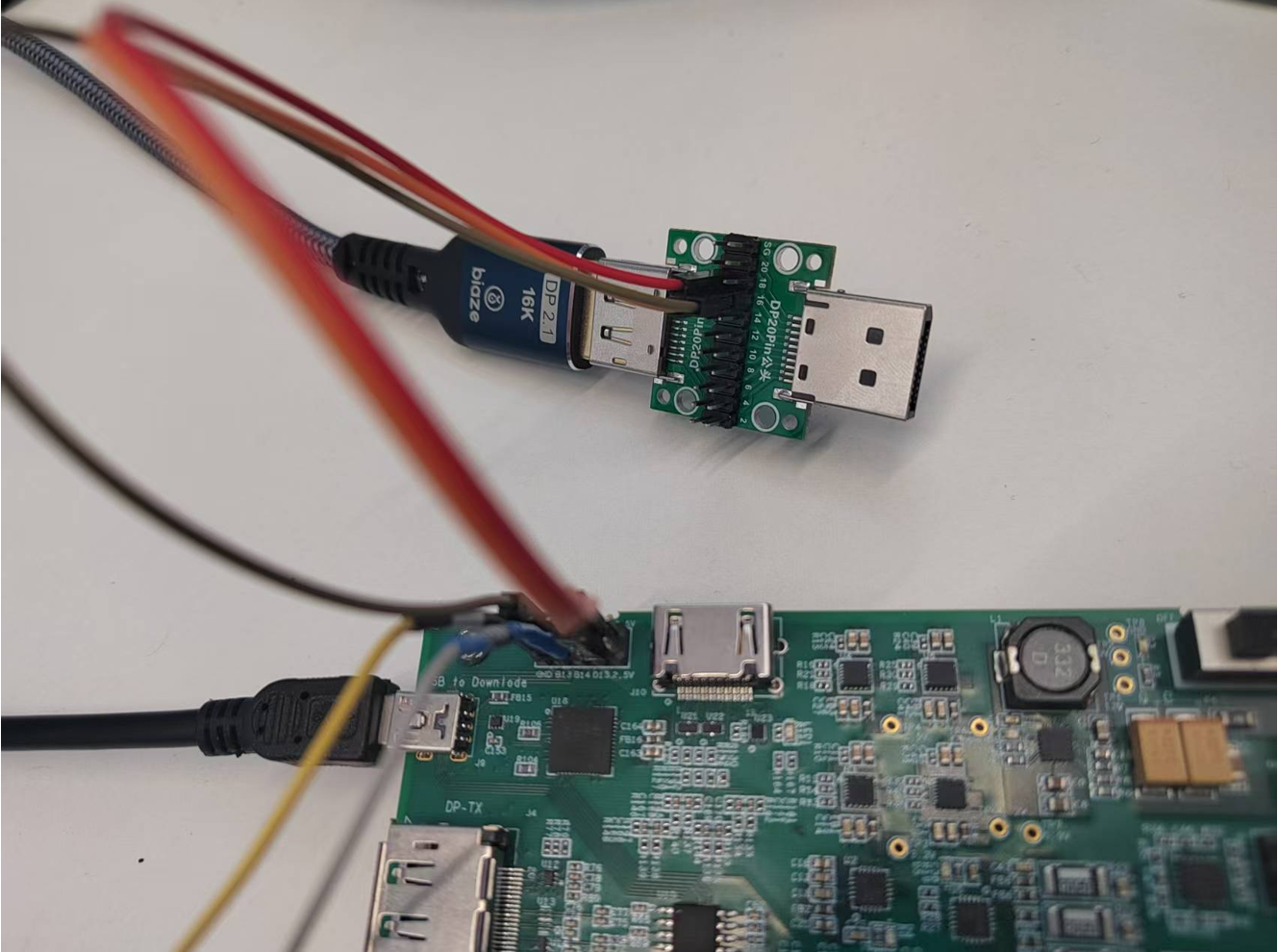

所以可以将差分信号转成单端再进行采集。这里我们利用一个DP口转接板和一个FPGA开发板,将AUX信号旁路到FPGA板上,在FPGA内利用LVDS IBUF,将差分信号输入,转成单端输出到GPIO。这时就可以用皇晶逻辑分析仪采集采集这个单端信号。

TLVDS_IBUF TLVDS_IBUF_inst

(.O (O_aux_test)

,.I (IO_aux_p)

,.IB (IO_aux_n)

);

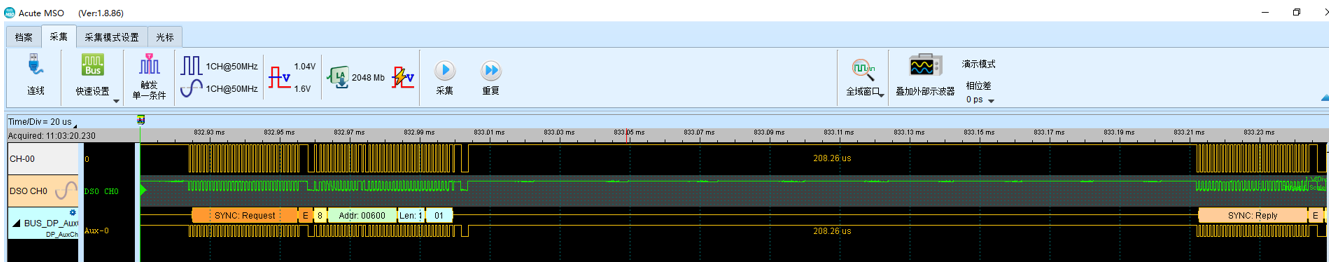

3. 信号采集

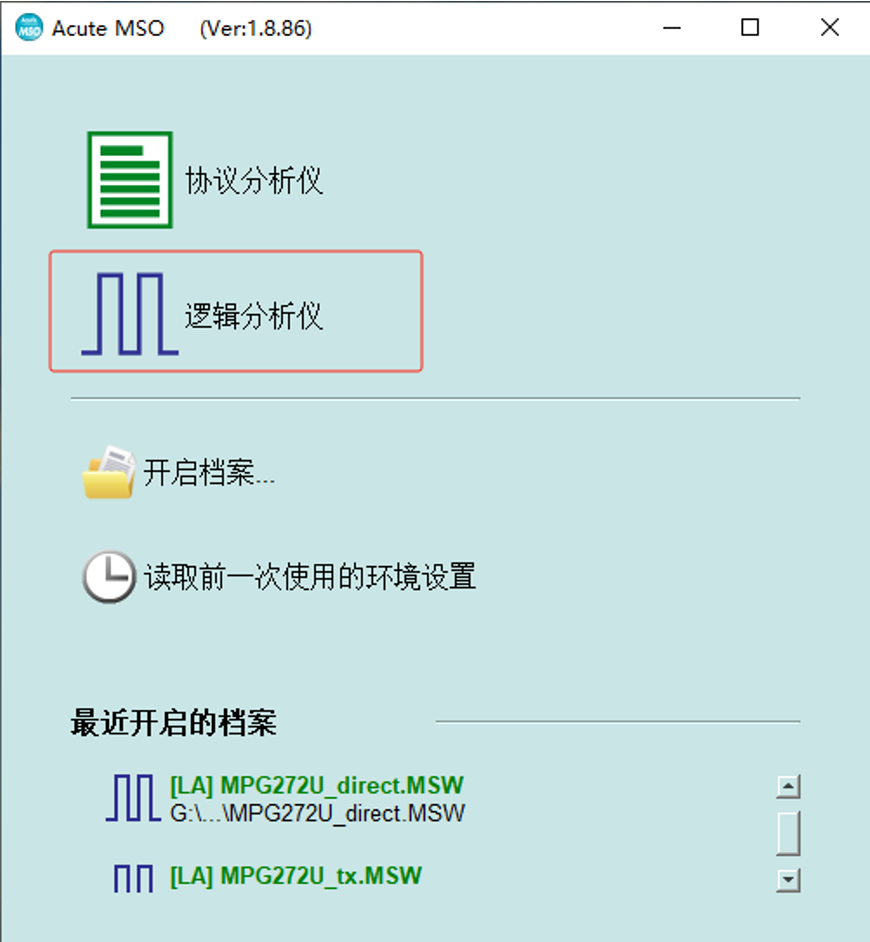

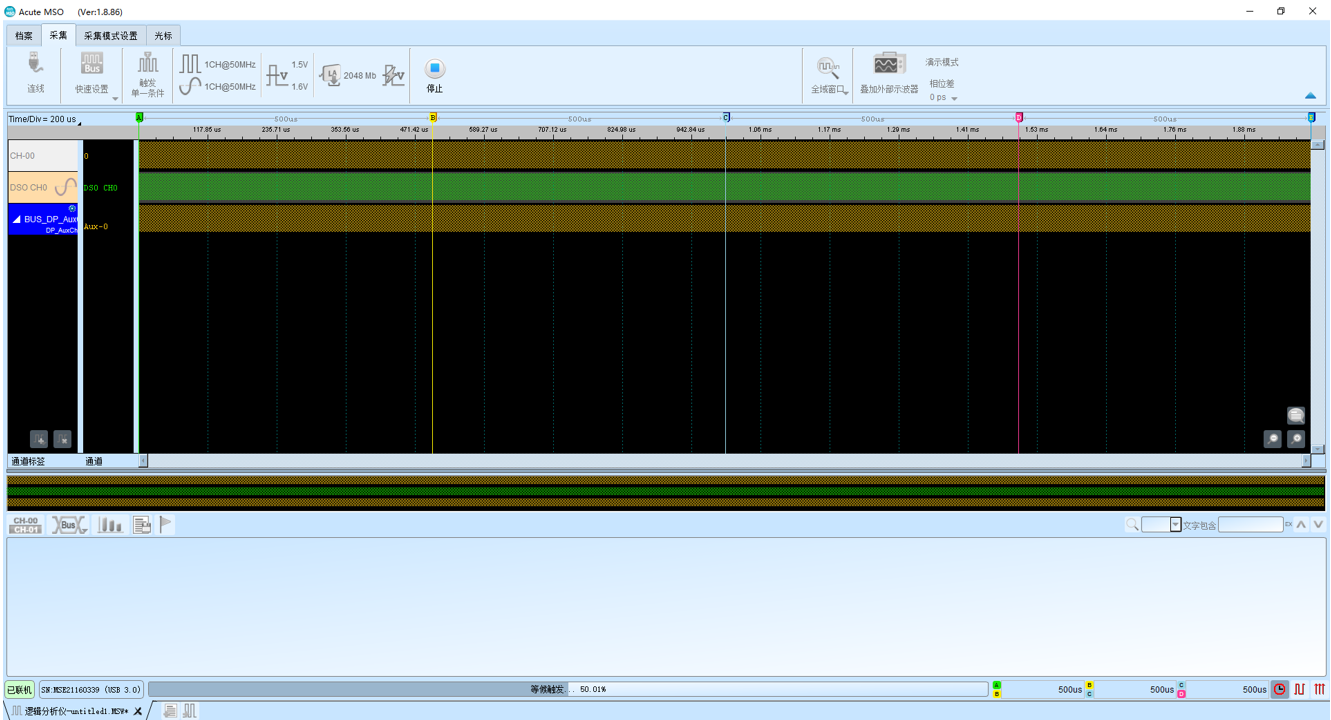

打开皇晶逻辑分析仪软件,可以选协议分析仪,也可以选择逻辑分析仪,选择逻辑分析仪便于看波形。

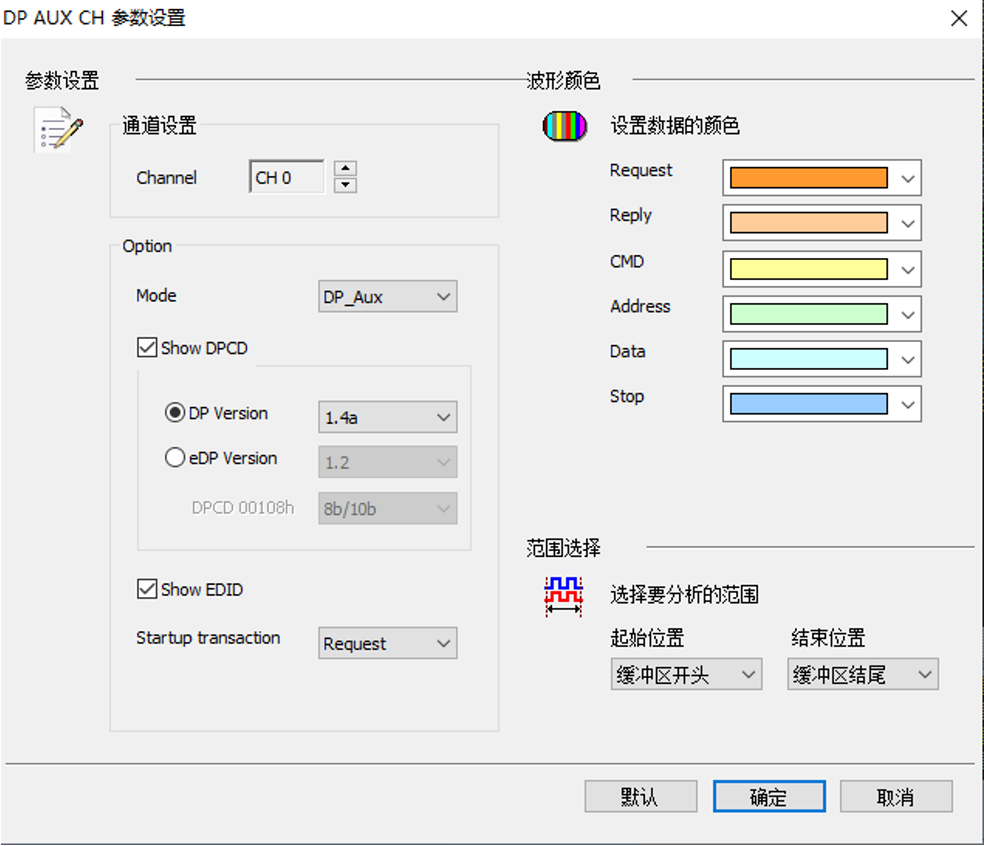

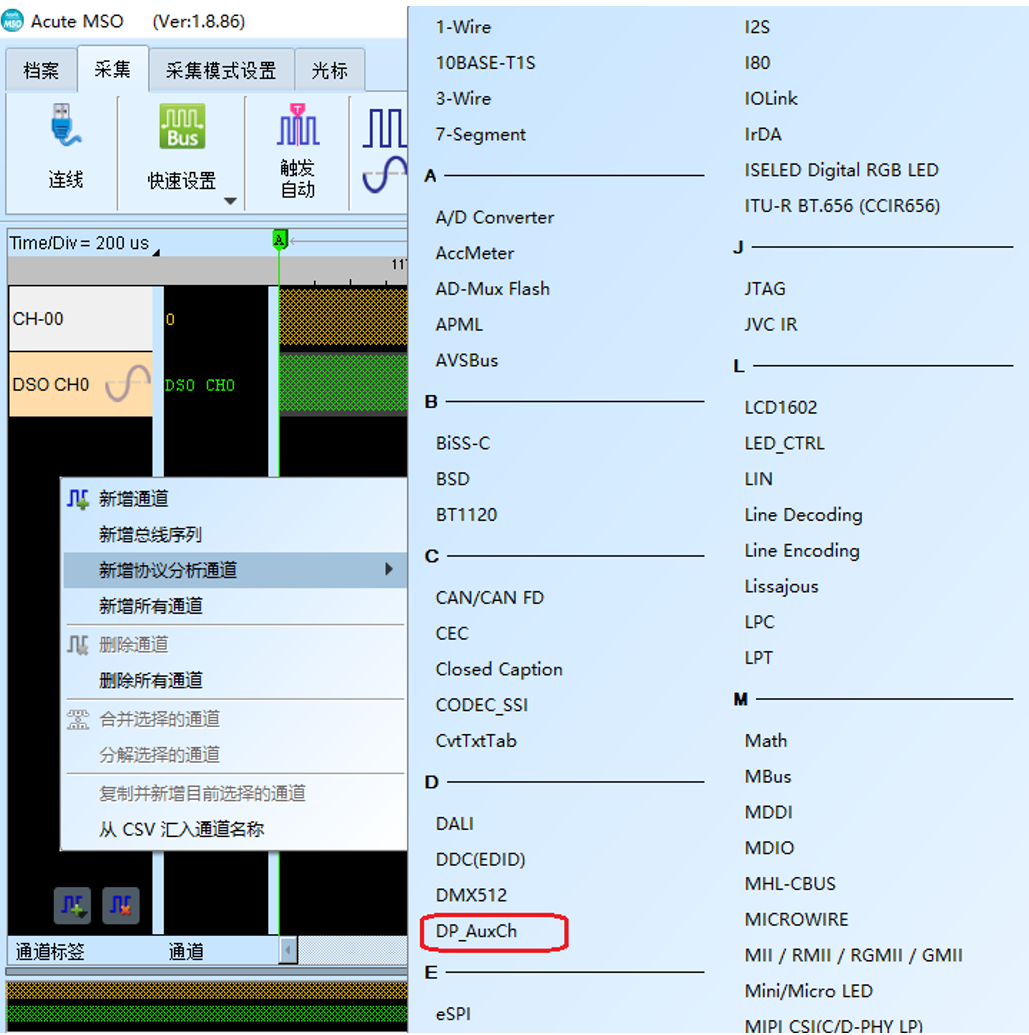

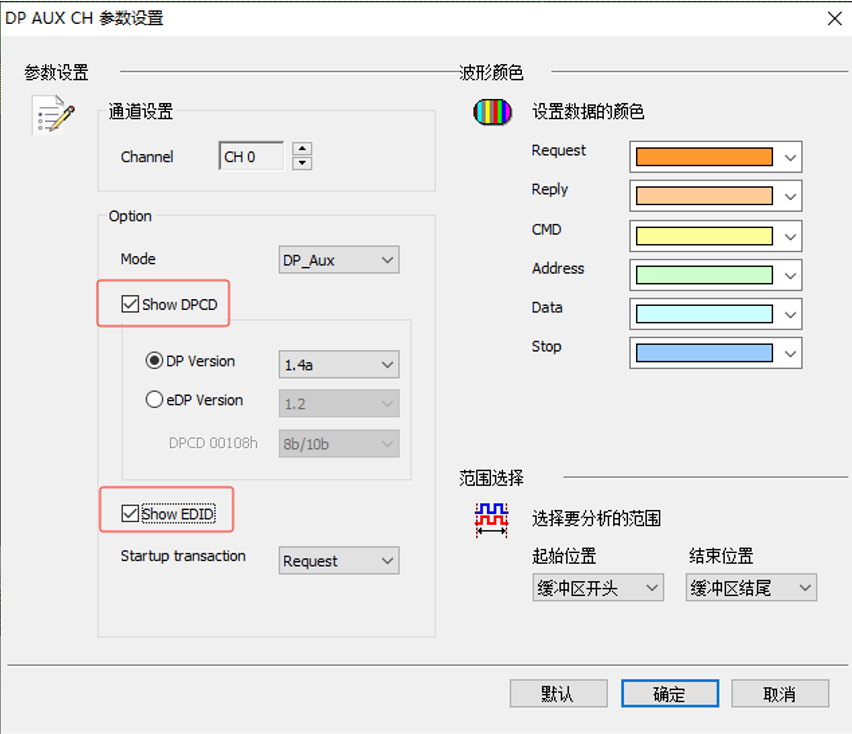

只保留CH-00通道,然后在左侧右键,选择新增协议分析通道,再选择DP_AuxCh。然后勾选Show_DPCD和Show_EDID。

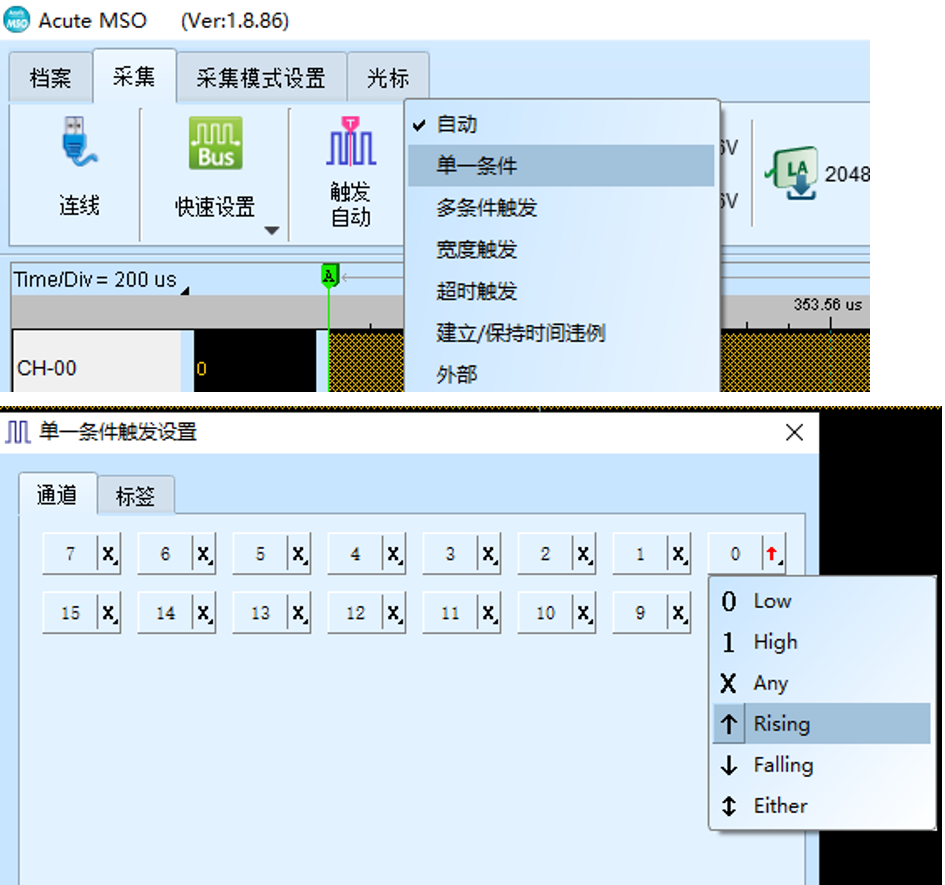

然后设置触发方式,点击触发自动,再点击单一条件,选择通道0,选择上升沿或下降沿触发都可以。

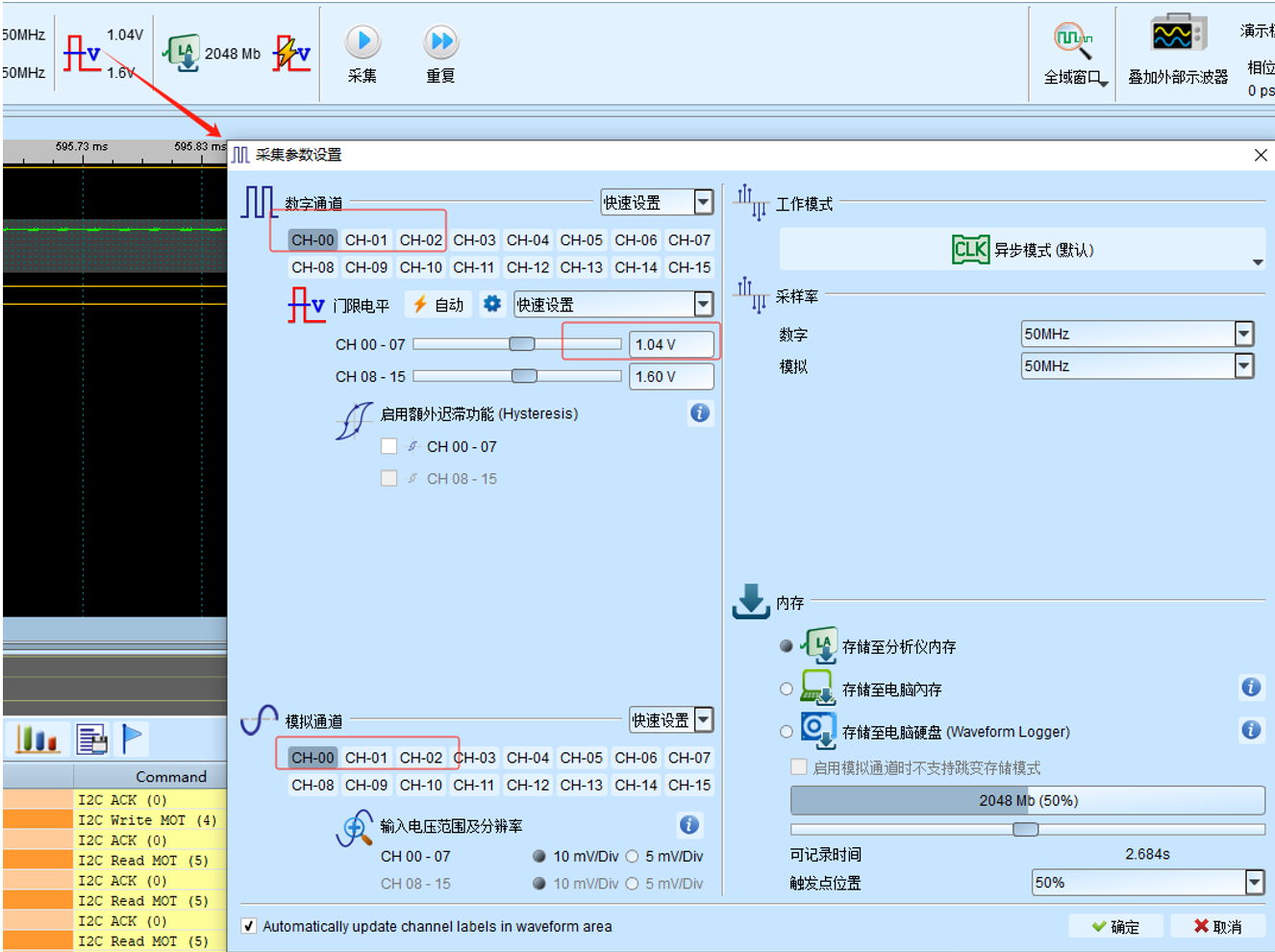

然后再点击触发电平设置,只保留CH-00通道,门限电平根据GPIO的电平标准自行进行设置。这里用了3.3V的GPIO,门限电平设为1.04V。

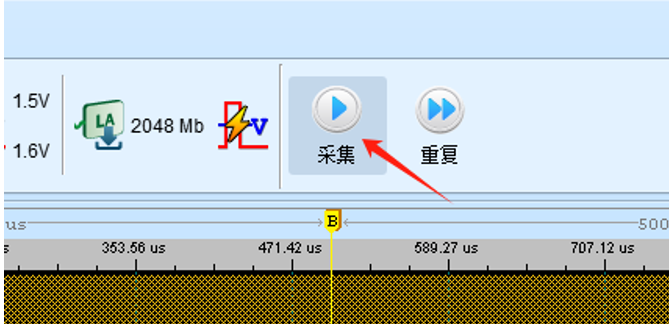

设置完成后,点击采集,会进入等待触发状态。

这时,插入DP线缆,或者打开DP显示器,显卡端就会进入AUX通信,就能抓到通信数据。不过FPGA的差分输入端没有电容,信号容易受干扰,也会影响到协议分析。