DisplayPort 2.0协议介绍(2)

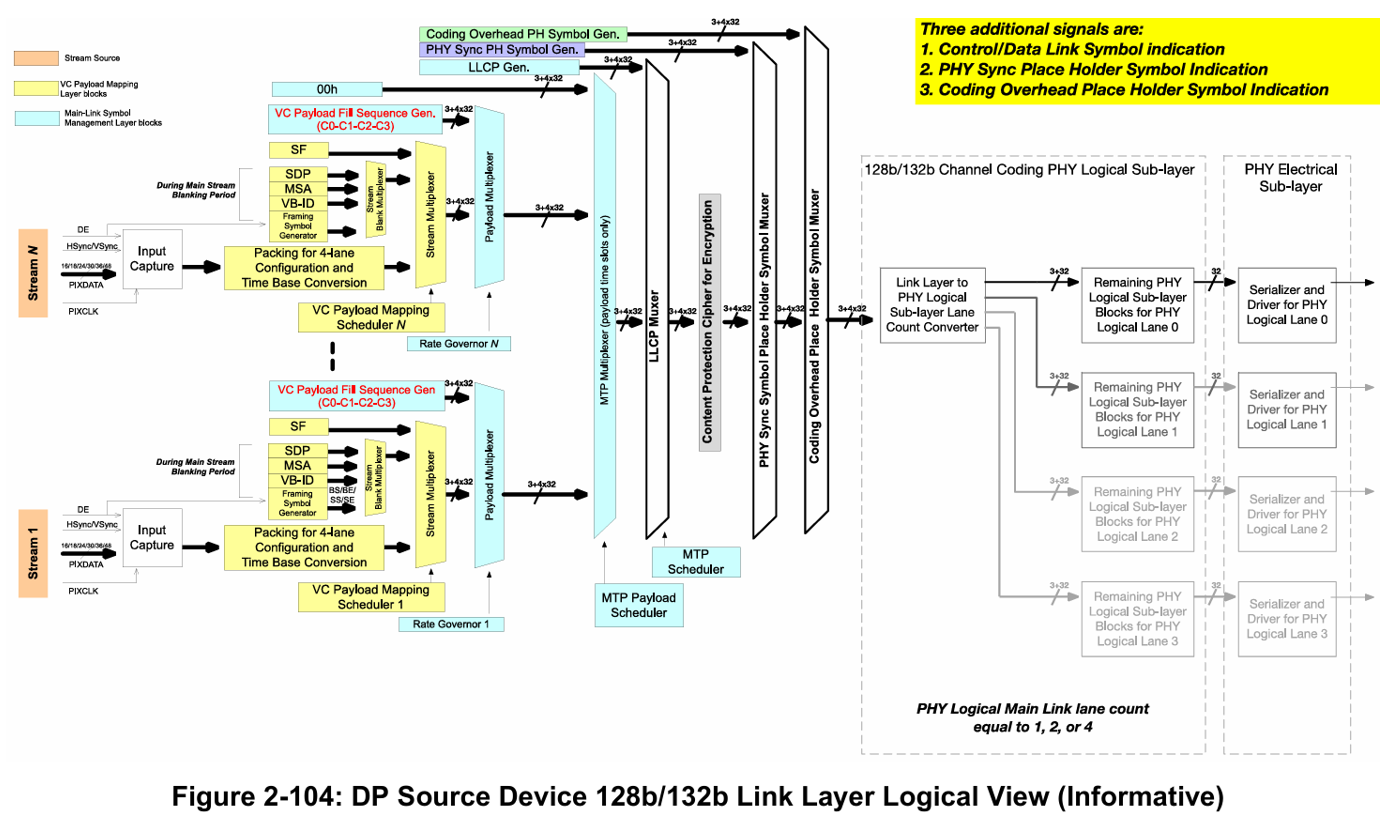

前面已介绍了DP2.0链路层的一些内容,继续学习Link layer链路层到PHY Logical Sub-layer物理逻辑子层的映射,以及物理逻辑子层的内容。下图右侧虚线框内是物理逻辑子层部分,看着框图简单,实际内容非常多。

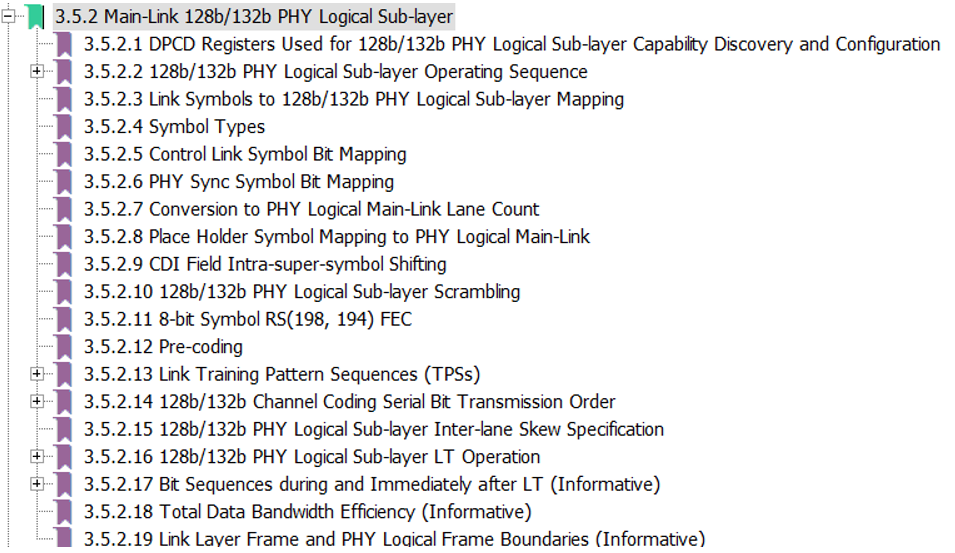

在DisplayPort 2.0协议的3.5.2章中分了19的子章节来介绍物理逻辑子层。

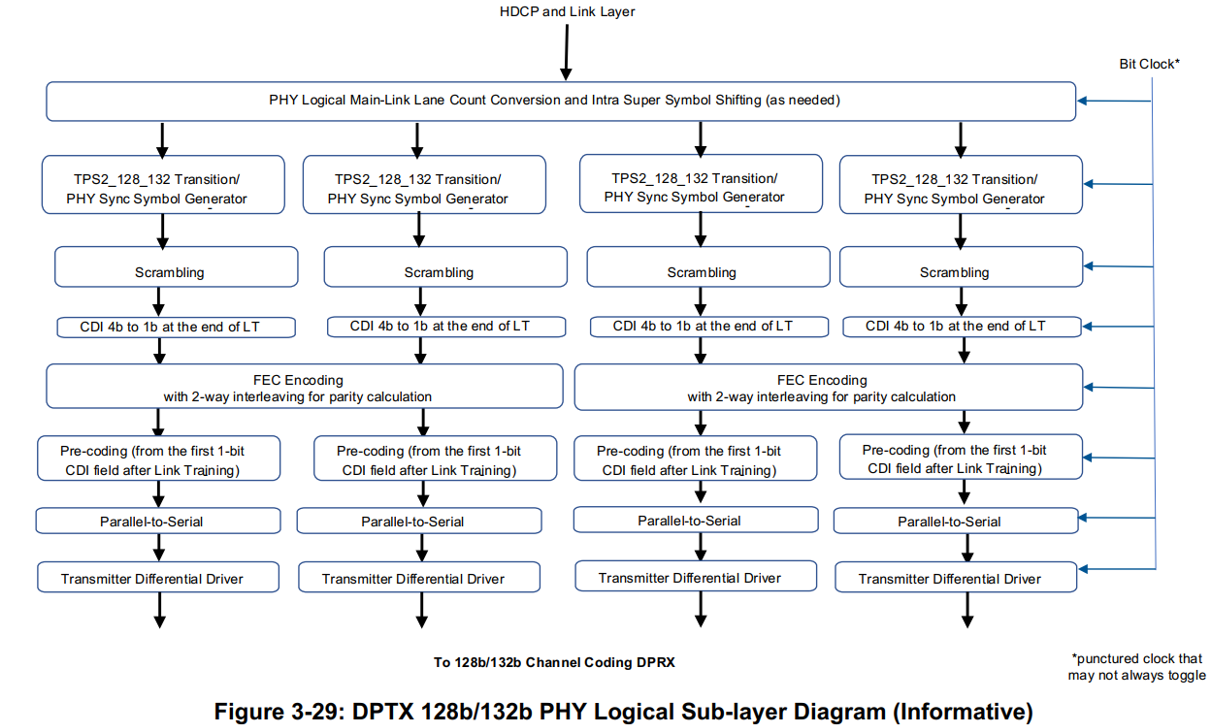

从链路层编码完成之后,进入物理逻辑子层,如下图所示,按照协议所写大体按如下7个部分顺序执行。

(1) link layer层到PHY logical sub-layer层通道数转换

(2) 内部超级符号移位

(3) 扰码

(4) Control Data Indicator(CDI)字段插入

(5) RS(198,194) FEC前向纠错码

(6) RS奇偶校验字节的双向交织

(7) 预编码

接下来我们对物理逻辑子层的一些概念做下介绍。

1.link layer层到PHY logical sub-layer层通道数转换

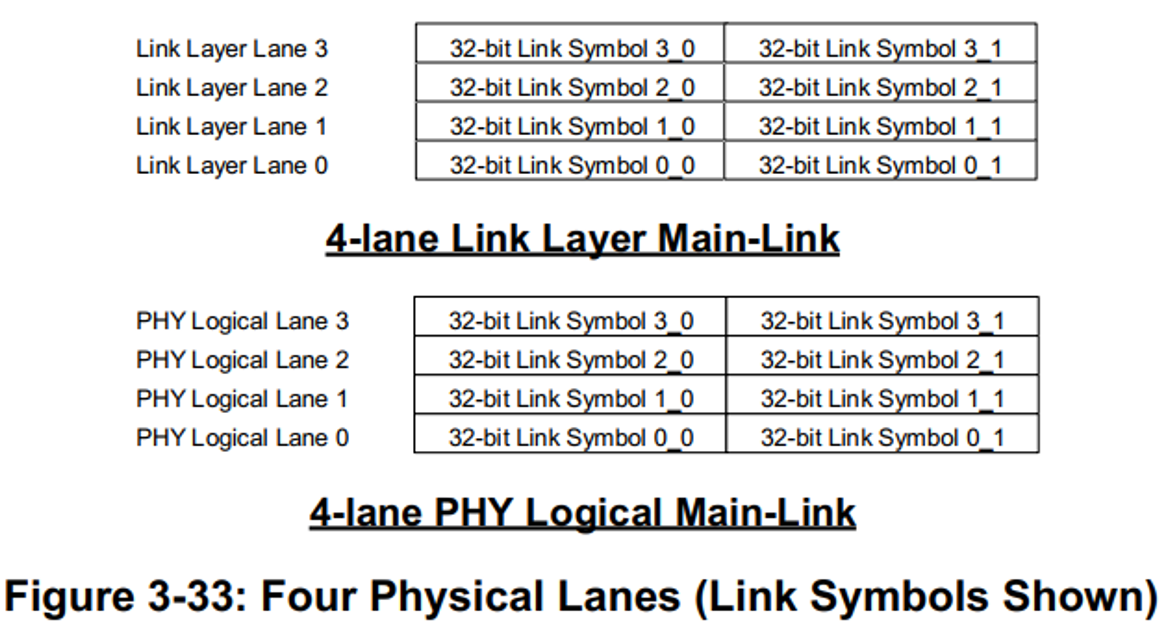

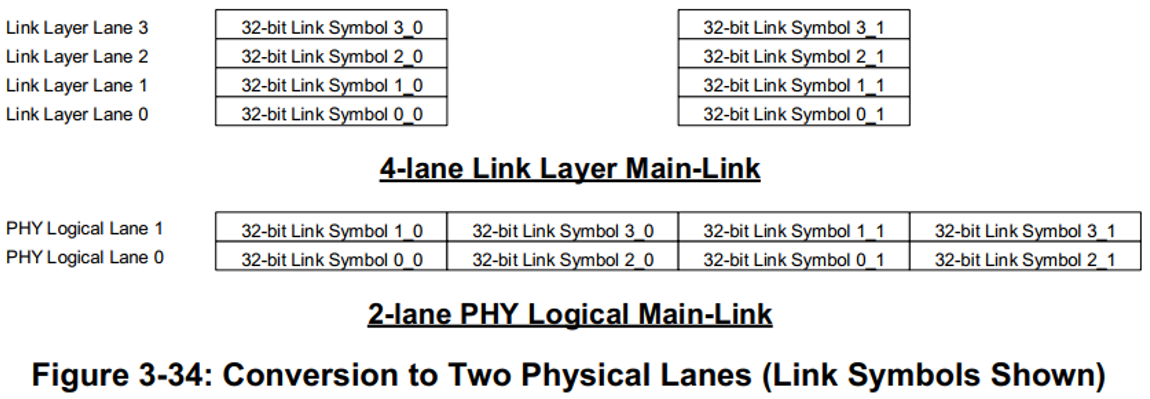

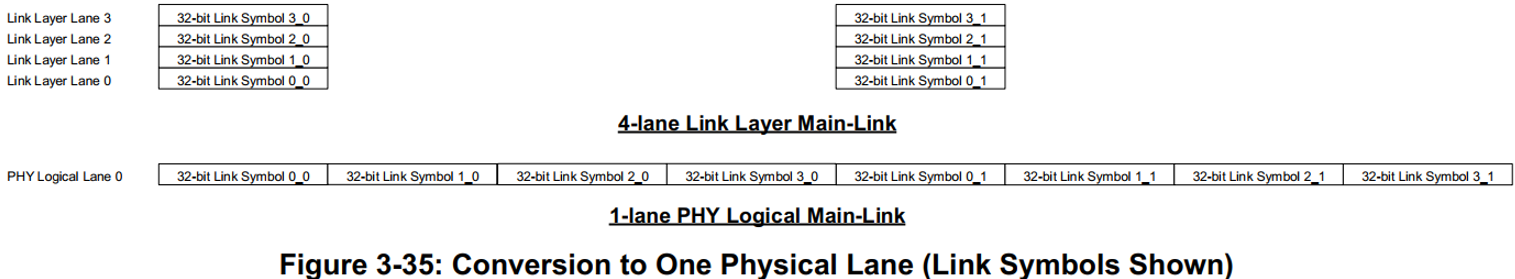

在链路层数据统一按4lane方式处理,但在物理逻辑子层,要根据实际lane数进行通道数转换。

物理逻辑子层实际lane数是4lane,处理最简单,每lane数据一一对应。

物理逻辑子层实际lane数是2lane,物理逻辑子层的lane0依次传输链路层lane0和lane2的32bit符号,物理逻辑子层的lane1依次传输链路层lane1和lane3的32bit符号。

物理逻辑子层实际lane数是1lane,链路层4lane的32bit符号依次传输。

2. Intra super symbol shifting内部超级符号移位

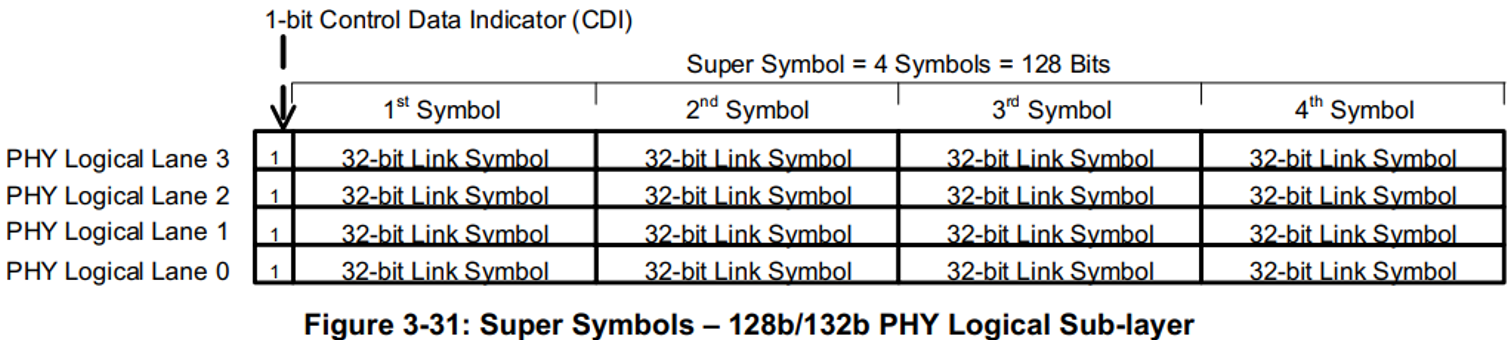

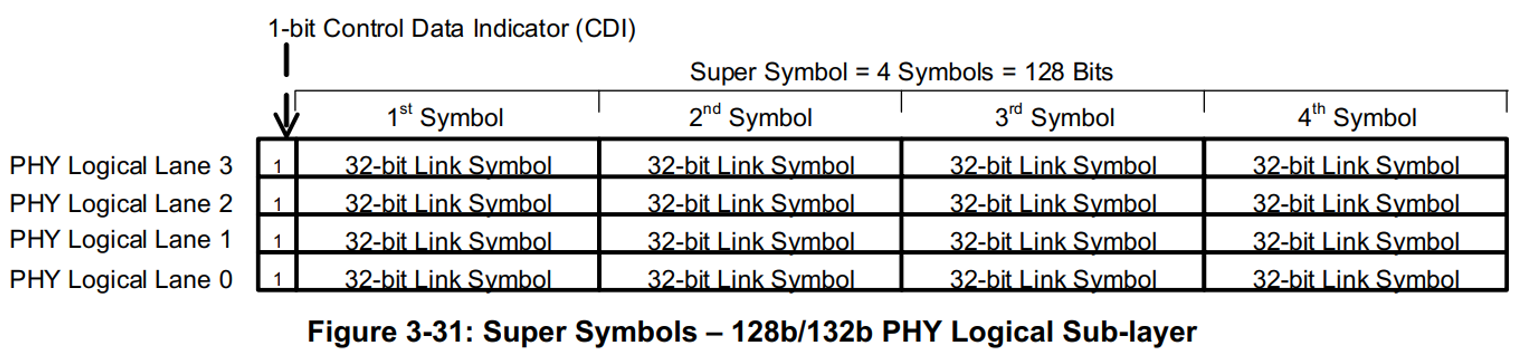

首先看一下super symbol超级符号的概念。在物理逻辑子层,1bit Control Data Indicator(CDI) 与4个32bit的link symbol链路符号数据组成1个super symbol超级符号。

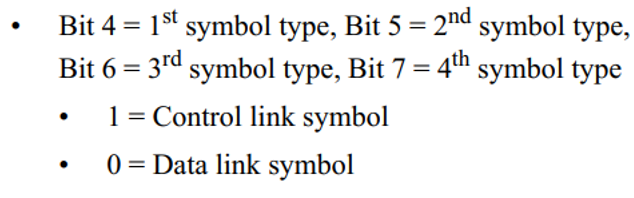

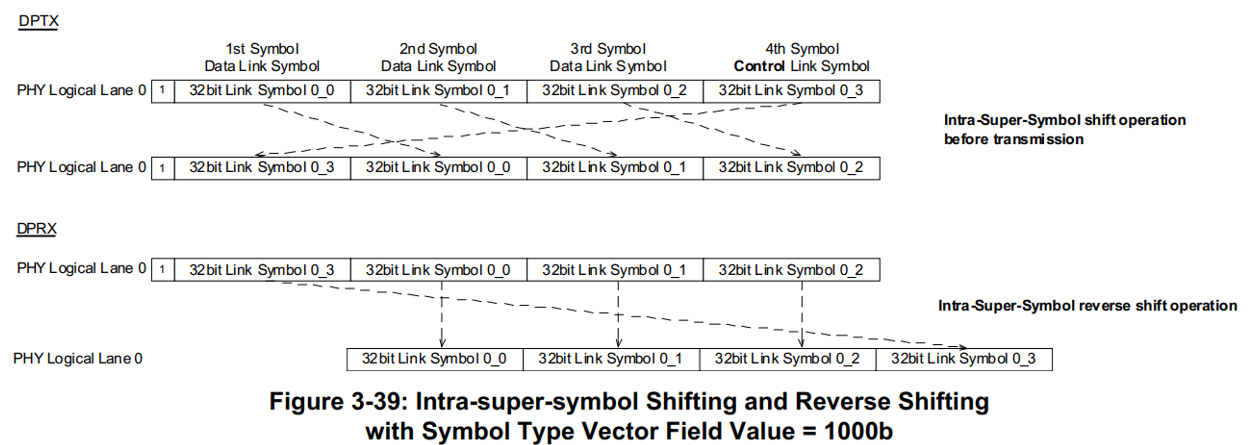

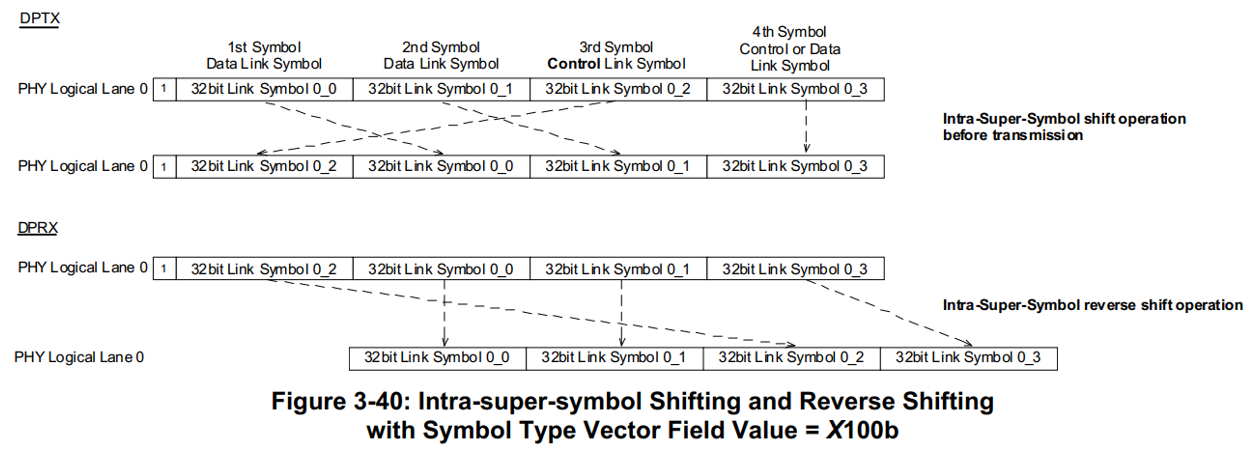

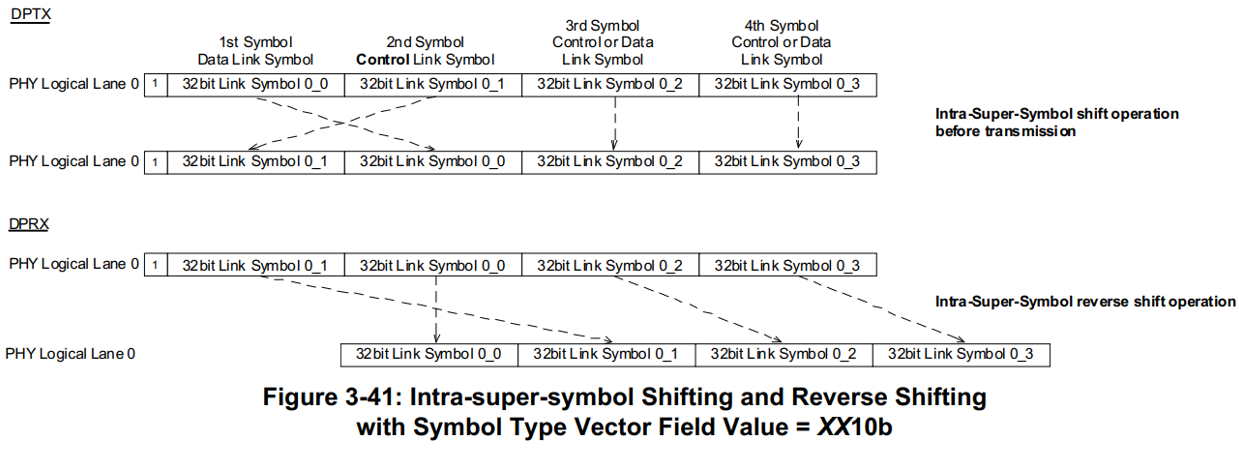

当超级符号包含了一个control link符号,但不是PHY sync符号,而且第1个符号不是control link符号,DPTX需执行intra-super-symbol shifting,将最近的control link符号移到第1个symbol位置。每个lane都需执行。在控制链路符号中的Symbol Type Vector field[7:4]指示是否是control link符号。

当Symbol Type Vector 的值为这些值时 1000b, X100b, and XX10b (where X is “don’t care”),需要执行内部超级符号移位。

1000b情况重排示意图。

X100b情况重排示意图。

XX10b情况重排示意图。

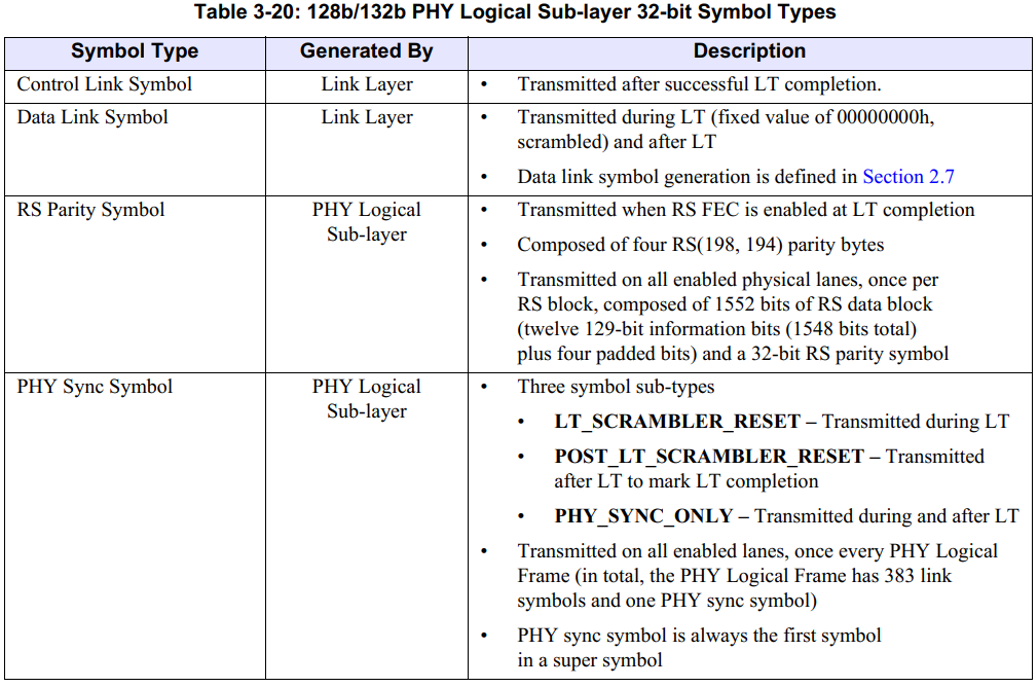

3. 物理逻辑子层符号类型

128b/132b通道编码物理逻辑子层symbol符号类型,一共4种。两种从link layer层产生,两种在物理逻辑子层产生。如下图所示。

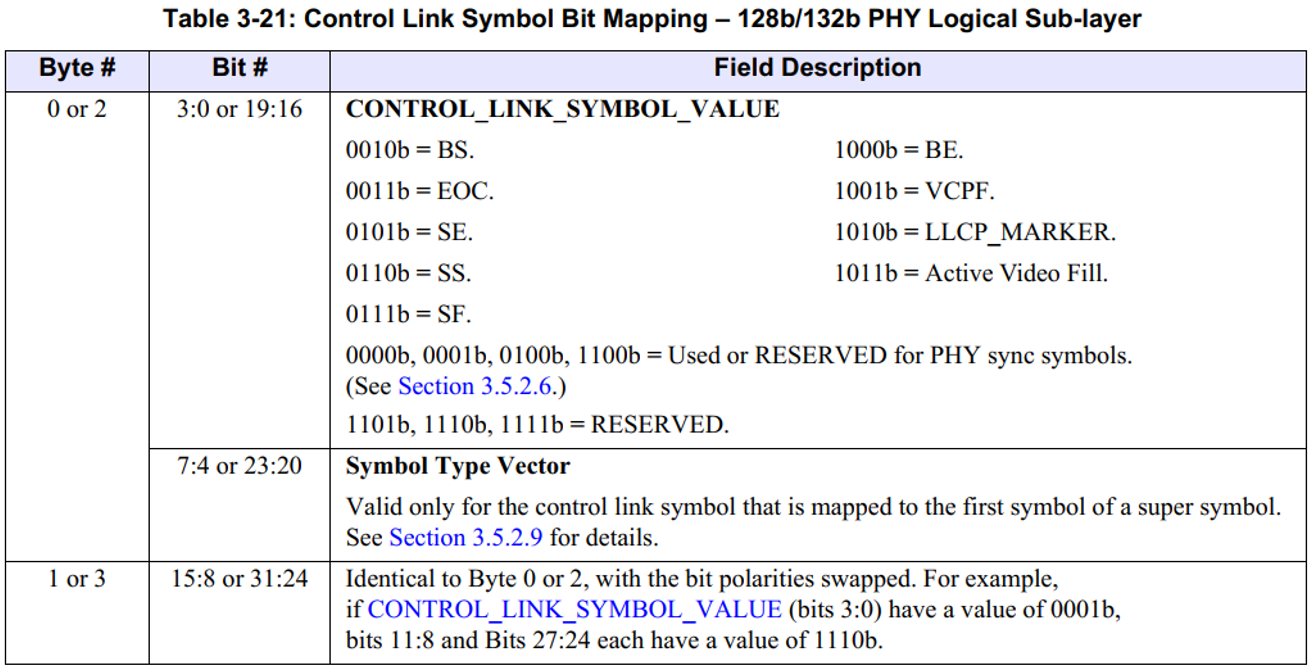

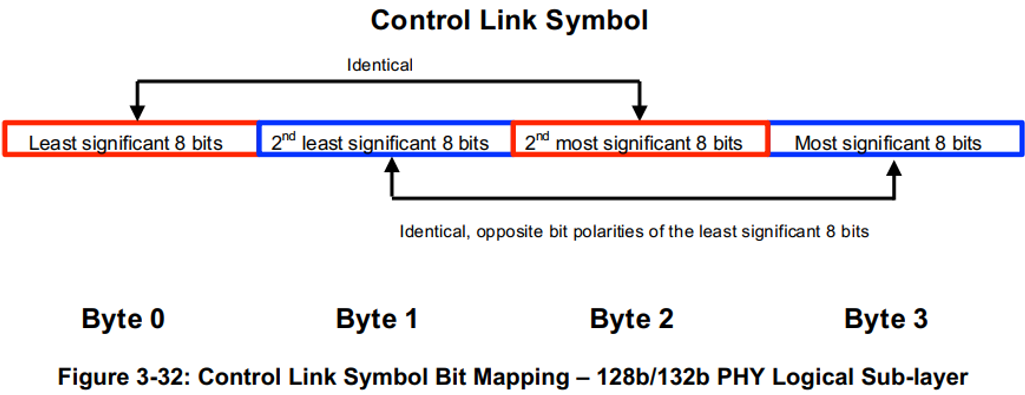

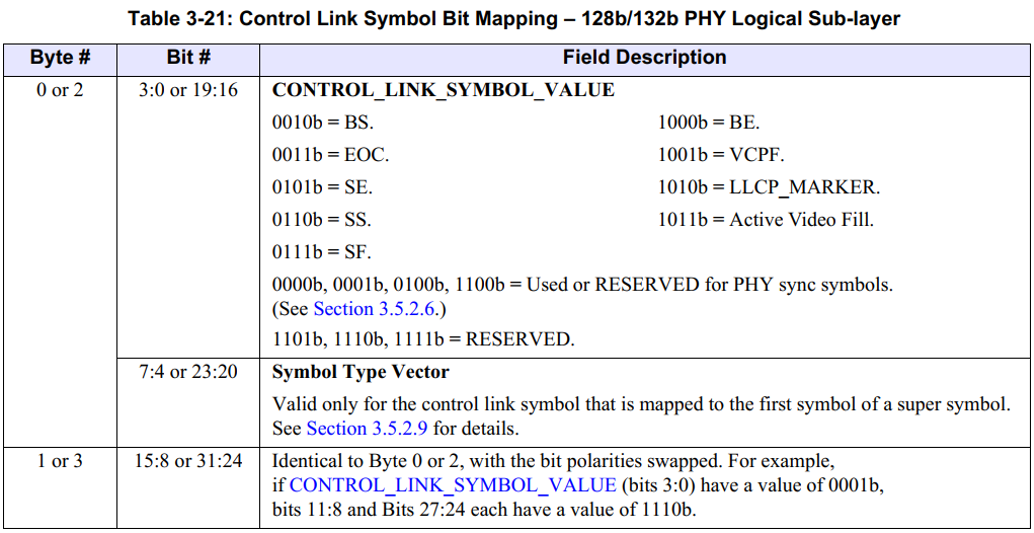

(1) Control link Symbol控制链路符号

控制链路符号是LLCP包的第1个32bit。结构如下图。

Byte0和Byte1相同,Byte2和Byte3相同,但Byte1是Byte0的按位取反,Byte3是Byte2的按位取反。

(2) Data link Symbol数据链路符号

在Link Training时发送00000000h数据,在Link Training结束发送视频数据。

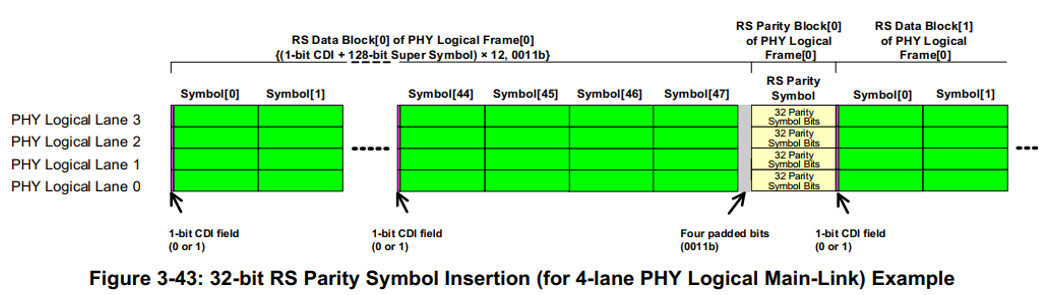

(3) RS Parity Symbol RS奇偶符号

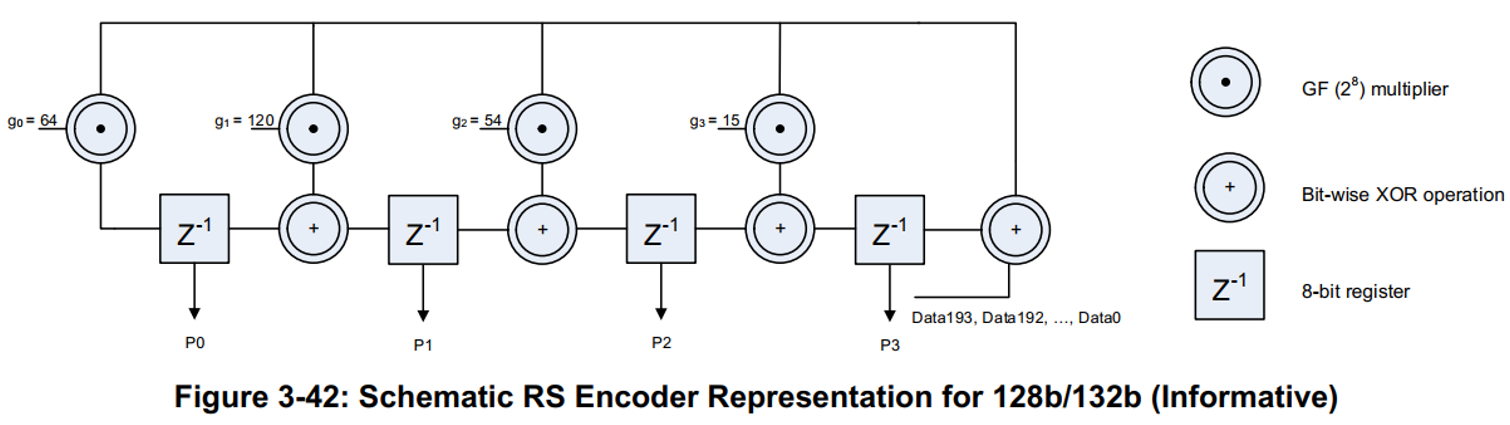

32bit的RS Parity Symbol 是RS data block数据块经过RS(198,194)多项式后之后计算出来的。

(4) PHY Sync Symbol 物理同步符号

在每个物理逻辑帧会插入PHY Sync Symbol物理同步符号。

物理同步符号格式在LT链路训练阶段和after LT completion链路训练结束阶段也不相同。

链路训练阶段使用3种符号:

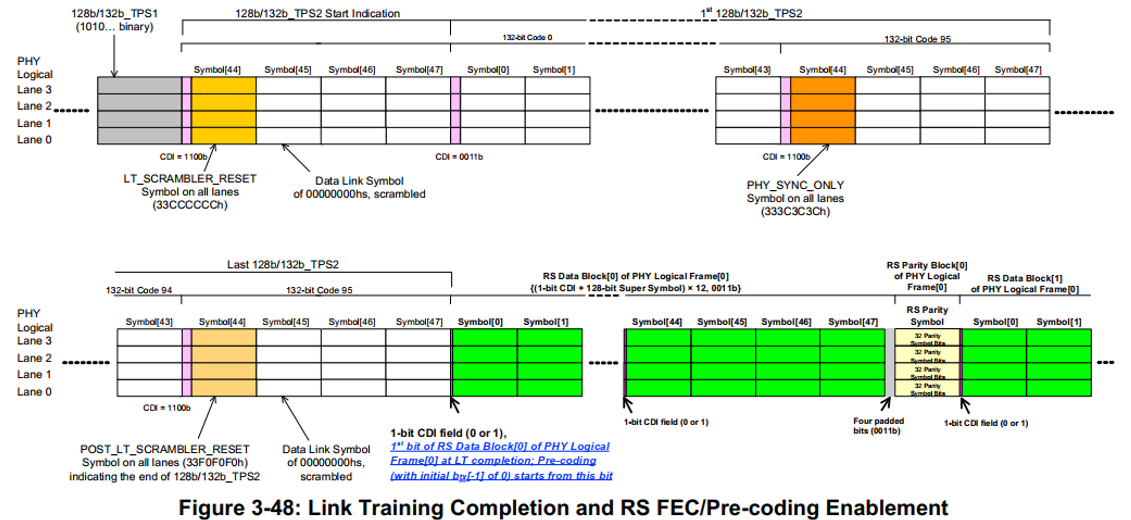

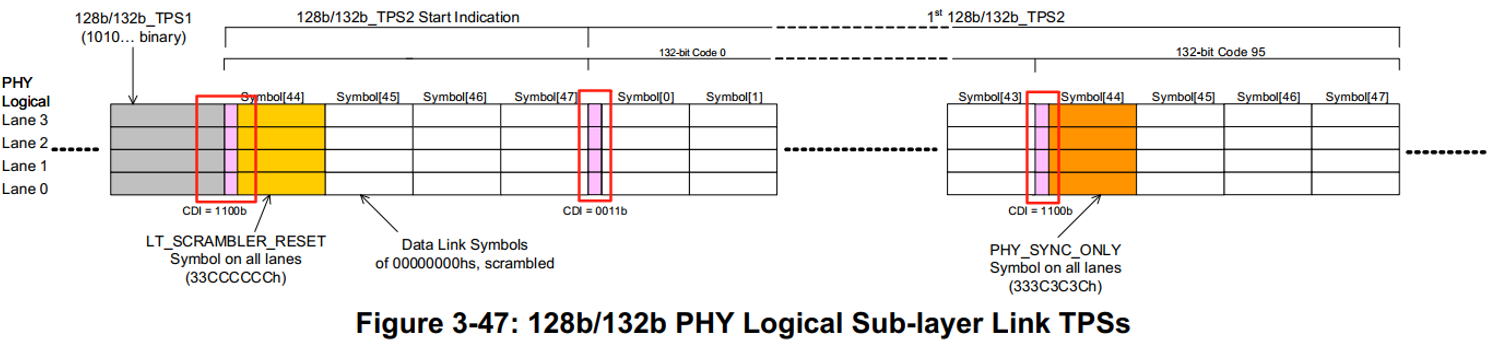

a) LT_SCRAMBLER_RESET符号, 128b/132b_TPS2开始时使用,值固定为33CCCCCCh

b) POST_LT_SCRAMBLER_RESET符号,128b/132b_TPS2结束时使用,值固定为33F0F0F0h

c) PHY_SYNC_ONLY符号,128b/132b_TPS2连续发送序列中间使用,值固定为333C3C3Ch

链路训练结束阶段只使用2种符号

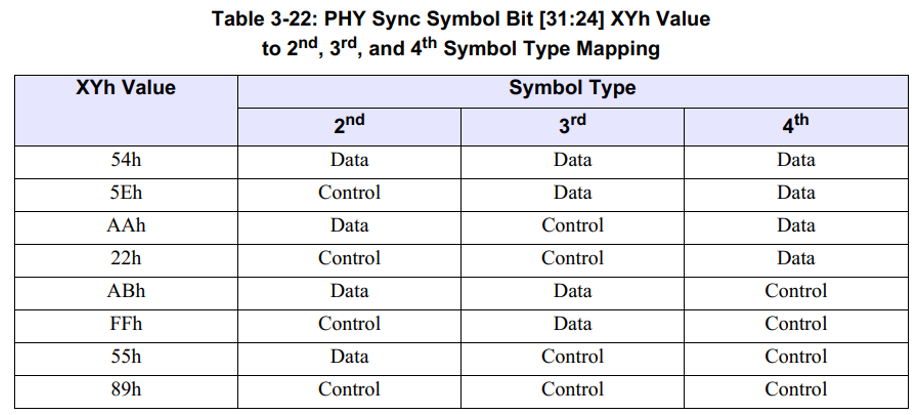

a) PHY_SYNC_ONLY符号,用XY444444h值替代,XY的值参见下表。

b) POST_LT_SCRAMBLER_RESET符号,用XY111111h值替代,每64个PHY_SYNC_ONLY符号用POST_LT_SCRAMBLER_RESET符号代替。

4. Scrambling扰码

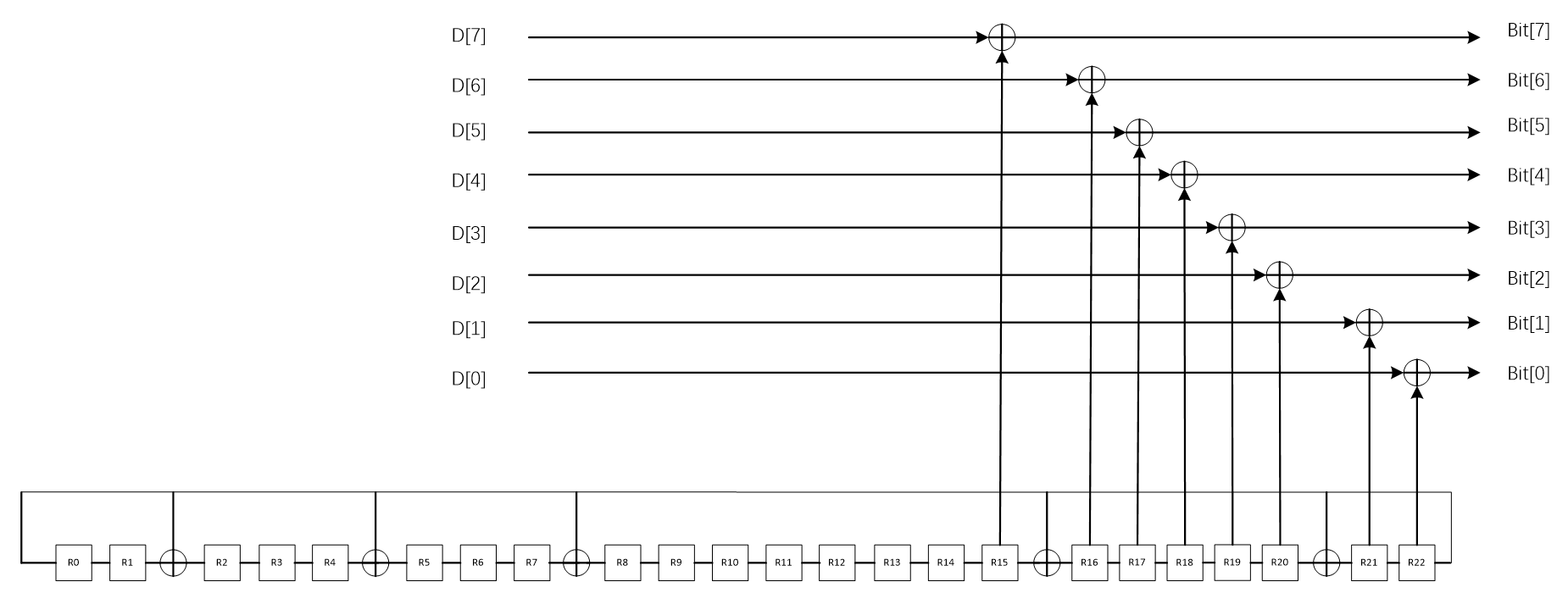

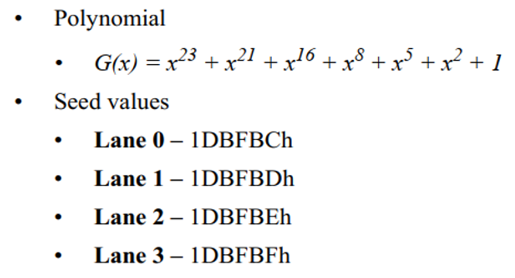

128b/132b编码的扰码多项式G(X) = X23 + X21 + X16 + X8 + X5 + X2 + 1

不同于8b/10b编码的扰码多项式G(X) = X16 + X5 + X4 + X3 + 1

扰码规则: (在3.5.2.17章节有示例数据,可用于验证Scramble和FEC)

(1)DPTX在扰码之前完成intra-super-symbol shifting,同理DPRX在扰码之后进行intra-super-symbol reverse shifting

(2)LT_SCRAMBLER_RESET和POST_LT_SCRAMBLER_RESET PHY同步符号不加扰。复位后,LFSR的值为种子值seed

(3)PHY_SYNC_ONLY PHY同步符号不加扰

(4)数据异或顺序,Control link symbols和data link symbols,LFSR输出的第1个字节与32bit的Control link and data link symbols的第1个字节相xor。LFSR输出的第1bit对应数据字节的bit0.

(5)CDI field,four padded bits,RS parity符号在扰码后添加。这些bit不加扰,也不用解扰。

由多项式并行产生32bit与数据加扰,每个lane独立加扰。扰码方式应该与8b/10b编码的类似,按字节异或加扰。

5. Control Data Indicator(CDI)字段

在PHY logical sub-layer层,插入Control Data Indicator(CDI)。在链路训练模式和链路训练完成之后,插入方法不同。

CDI字段大小如下:

•在链路训练模式,序列128b/132b_TPS2进行link训练时CDI为4位

•link训练完成后CDI为1位,1bit的CDI加4个32bit的link符号组成一个129bit的super symbol超级符号

•链路训练模式,序列128b/132b_TPS1进行link训练时不使用CDI

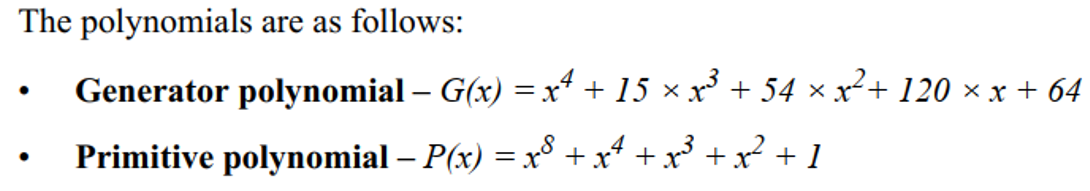

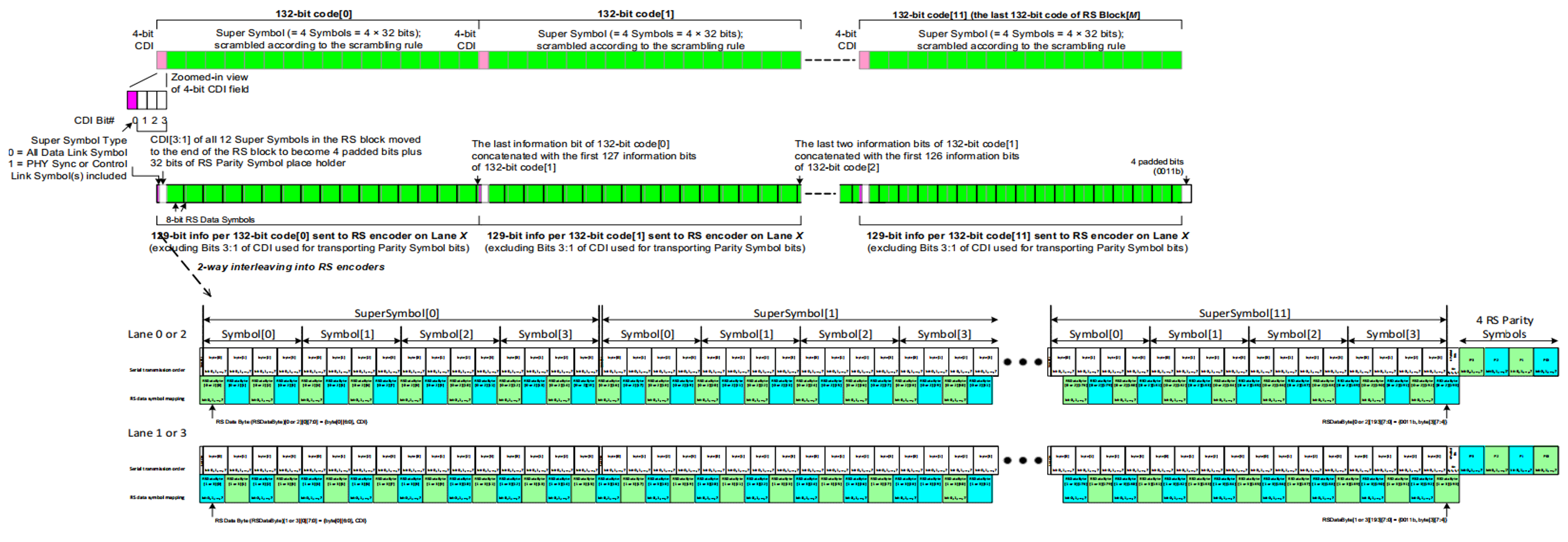

6. RS(198,194) FEC前向纠错码

RS(198,194),8bit symbol,输入符号数194,即194x8=1552位,输出符号数198符号,即198×8=1584位,增加了1个冗余符号位(32位)。每个RS data block数据块包含194个RS symbols(194x8=1552bits),可最多纠正2个RS symbol 错误。

每个lane的RS data block数据块由12个超级符号,12个CDI bits,和4个padding bits(0011b)附加bits组成。12*128bits + 12bits + 4bits = 1552bits

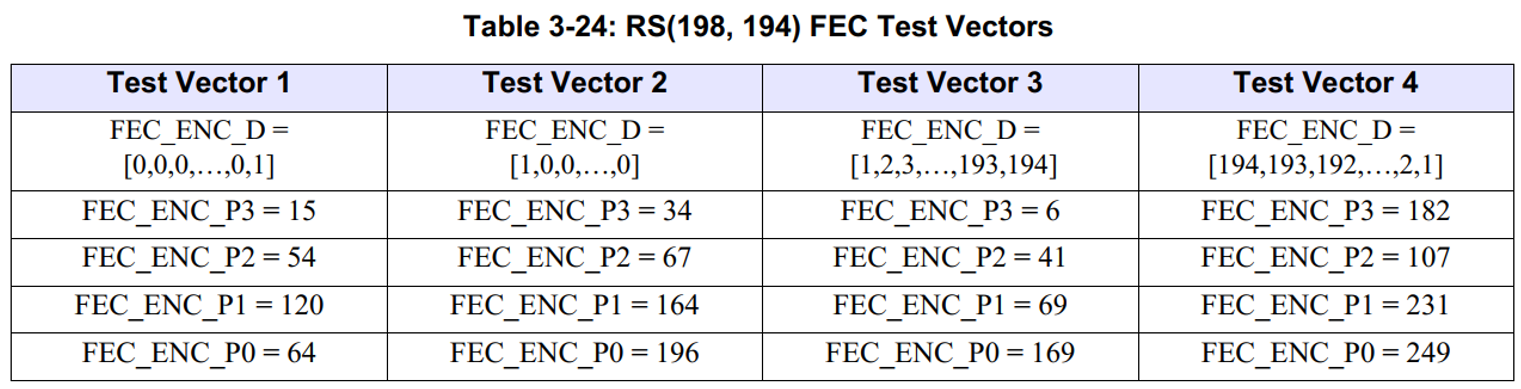

数据验证用 Table 3-24的测试向量验证。

测试向量1由193个字节0和1个字节1组成。

测试向量2由1个字节1和193个字节0组成。

测试向量3第1个字节1,其余字节依次递增,最后1个字节是194。

测试向量3第1个字节194,其余字节依次递减,最后1个字节是1。

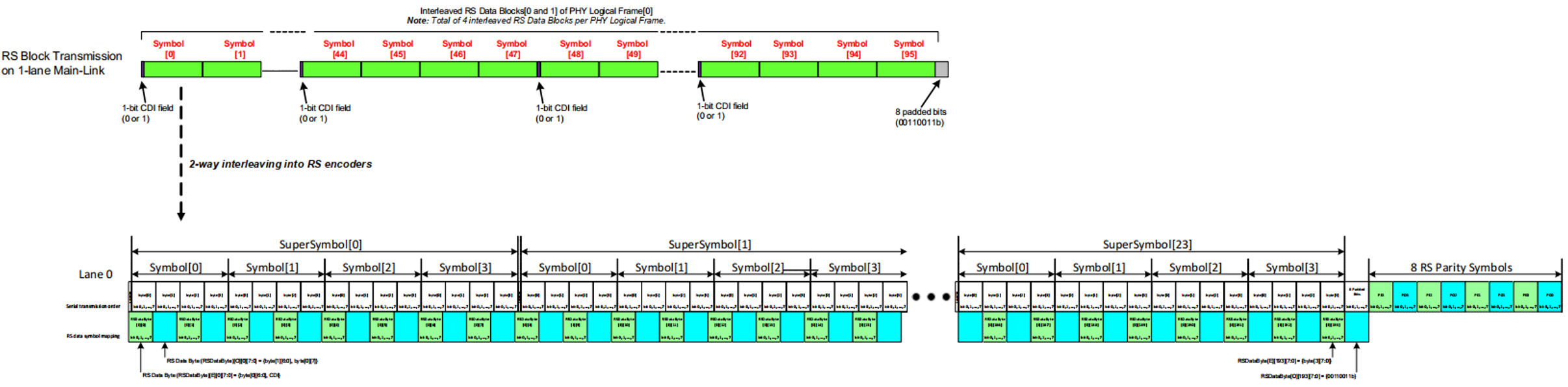

7. 2-way interleaving of RS parity bytes (RS奇偶校验字节双向交织)

4 lane或2 lane情况,每lane 1个RS Data block。

1 lane情况,2个RS Data block被交织。需要2个RS encoder。

8. Pre-coding预编码

预编码这种转换便于DPRX的RS FEC解码器进行纠错。可以将连续出错转换成首尾2个错误。

预编码开始于1-bit CDI of RS Block[0]。也就是说LT时不用预编码。

The initial btx[-1] and brx[-1] values初始值要清零。

9. Link Training Pattern Sequences (TPSs)

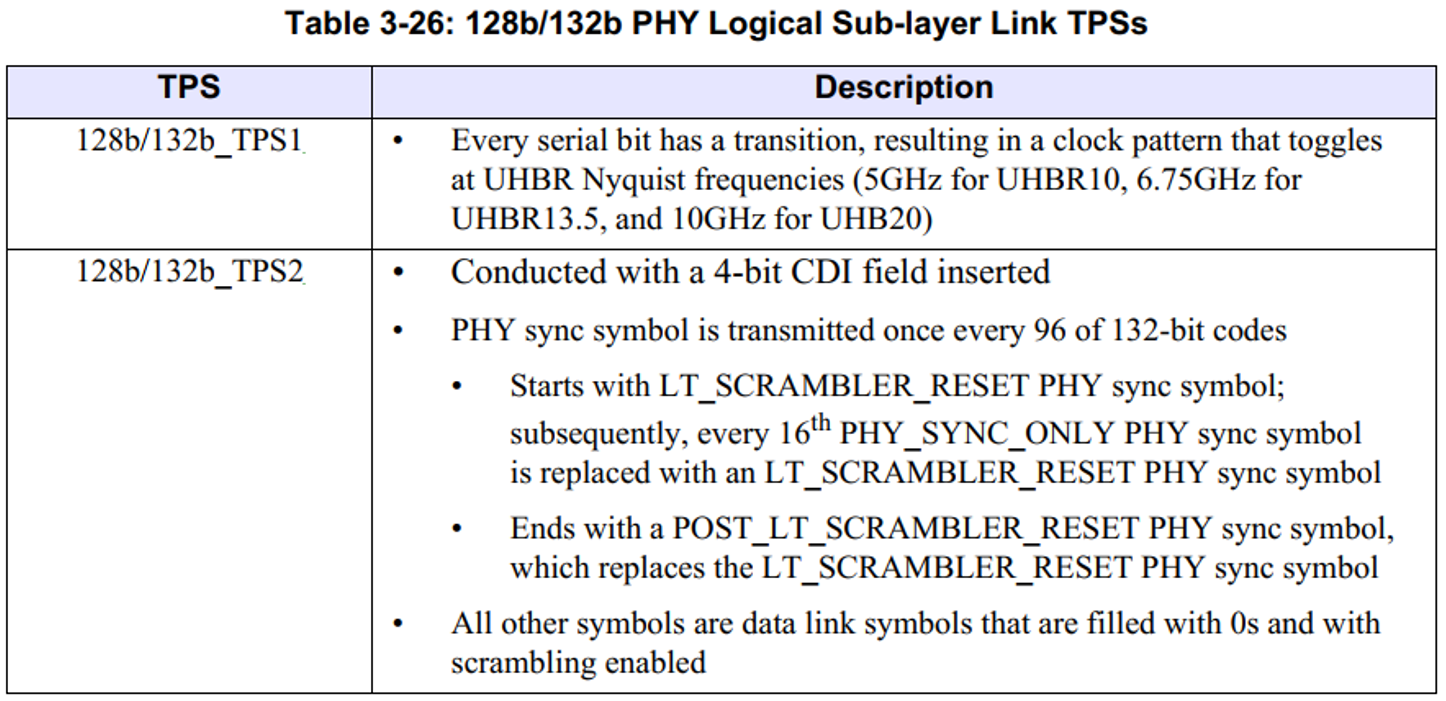

128b/132b物理逻辑层定义了两种TPS,分别是128b/132b_TPS1和128b/132b_TPS2。

128b/132b_TPS1:和TPS1类似,就是0,1连续翻转。

128b/132b_TPS2:插入4bit CDI域,除同步符号,其他是0数据扰码后的data link symbol。

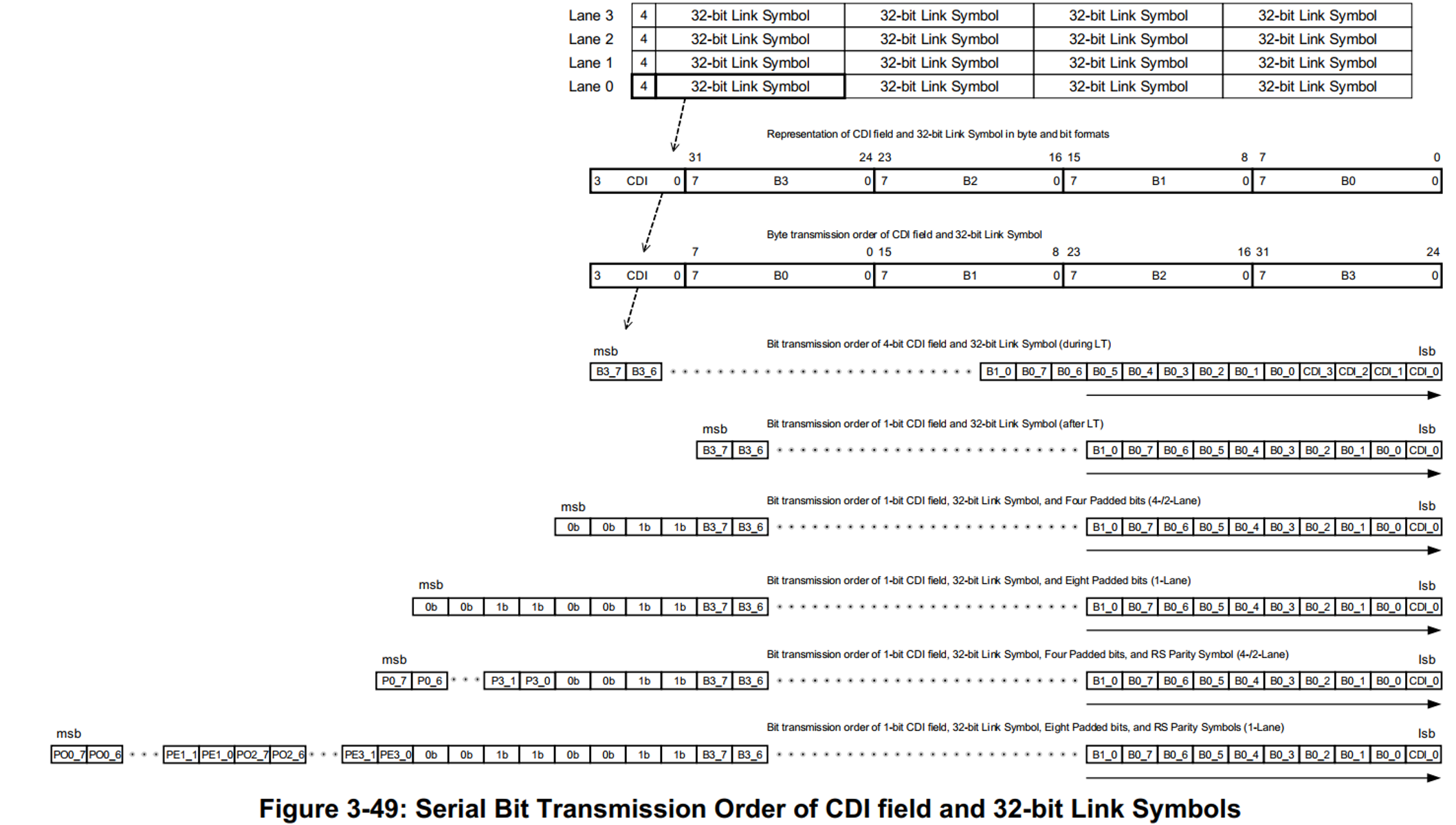

10. 128b/132b Channel Coding Serial Bit Transmission Order

Bit传输顺序,按以下顺序传输:

(1)CDI

a)during LT,4bit CDI,bit0先传,bit3后传

b)after LT,1bit CDI先传

(2)4个32bit link symbols

LSB低字节先传,字节中bit0先传

(3)RS data block padded bit

a)4或2 lane,4bit padded bit,bit0先传

b)1 lane,8bit padded bit,bit0先传

(4)32bit-RS parity symbol

MSB高字节先传,字节中bit0先传

在最后预编码之后,要做并串转换, SERDES的实际数据位宽与132bit可能并不相同,所以还要利用Gearbox做位宽转换,这在协议中并不体现。